摘 要:设计一种确保AFDX交换机数据帧发送和接收顺序保持一致的虚拟链路调度模块,实现对各端口虚拟链路校验请求的有序处理。通过HDL描述,设计完整的硬件电路,并利用FPGA加以实现。对设计进行仿真,并加入断言检测。结果表明,此设计符合AFDX交换机端口对数据帧请求处理的要求,有效地保证了AFDX交换机各端口公平调度,满足航空电子数据确定性的要求。

关键词:AFDX; 虚拟链路; 调度; 断言

引言

随着航空电子技术的不断发展,传统通信网络的数据总线已经无法满足下一代航电系统对通信速率、处理能力、可靠性等的要求。航空全双工交换式以太网AFDX/ARINC 664(Avionic Full-Duplex Switched Ethernet)是适用于航电系统信息传输的确定性飞机数据网络总线系统[1,2]。它基于标准的IEEE802.3技术[3],在以太网基础上增加了确定性定时机制和可靠的信息传输机制以适应航电应用;确定性定时机制通过具有有限带宽和帧传输间隔的虚拟链路技术实现,可靠的信息传输通过帧管理机制实现,包括信息的冗余传输和完整性检查[4];传输速率支持10Mb/s和100Mb/s,是现代航空数据总线的最佳选择之一。

AFDX网络主要由终端系统(ES)、交换机(SW)和链路三部分组成。AFDX交换机是其核心部件[5]。它可以接收来自任一端口的帧,并将其转发到一个或多个端口(包括接收端口)[6]。

本文设计并验证了一种实现AFDX交换机各端口公平调度、确保数据帧正确发送和接收的端口链路校验请求模块。

1 设计原理

AFDX终端系统通过虚拟链路(VL)交换以太网帧,在网络的任何一个VL中,只有一个ES能作为它的源。即对于任何一个VL,一个ES不能同时设计成它的发送方和它的接收方。VL是一个概念上的通信载体,定义了一个逻辑的单向连接,这个连接从一个源ES到一个或多个目的ES。对于每一个VL,ES应保持发送和接收数据的顺序一致,即顺序的完整性。在交换机中应该保持VL相关的输入帧和输出帧的顺序,AFDX的用户按照帧被发送的顺序对帧进行接收[7~9]。

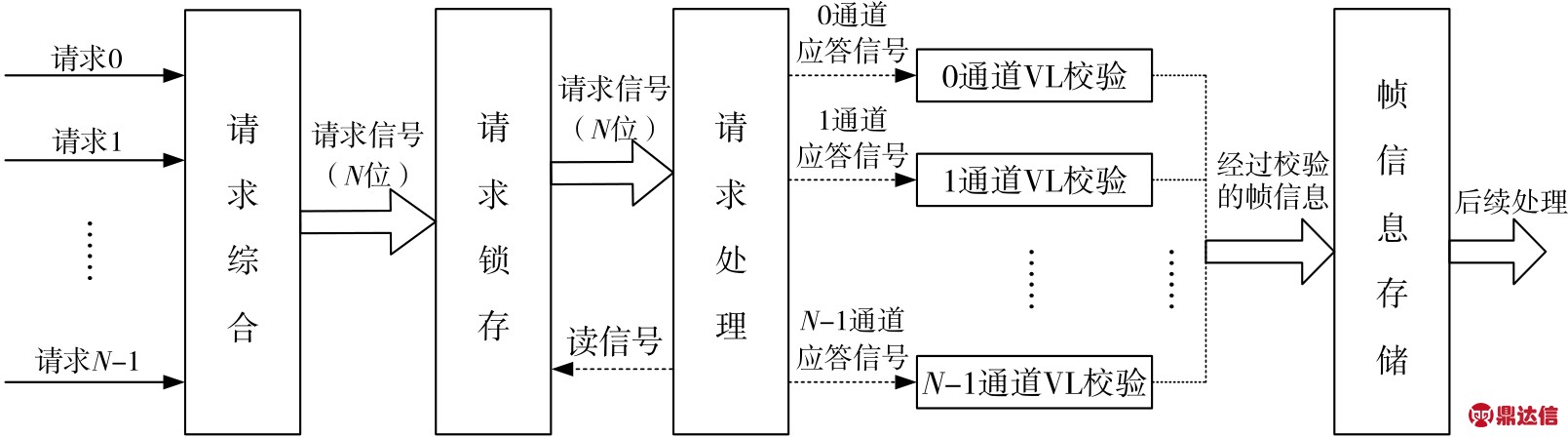

当多个端口请求发送数据时,需要对所有的请求进行合理的处理,从而产生正确有序的应答信号。根据这些应答信号,调度相应的链路通道,对其进行VL校验后,将帧数据信息存入合适的存储器中,以方便后续模块进行处理。具体流程如图1所示。

本文设计的链路调度模块主要包括请求综合、请求锁存、请求处理和经过校验后的帧信息数据存储,以确保AFDX交换机中的数据帧转发顺序与接收顺序保持一致。其主要工作流程如下:

图1 多端口请求发送数据的具体流程

①当任意通道的请求信号有效时,请求综合模块汇总所有通道的请求信息,并传递给请求锁存模块;

②请求锁存模块将所有通道的请求信息锁存,并写入请求信号存储器中;

③当请求信号存储器中存在请求信息时,请求处理模块产生读信号,并根据存储顺序从请求信号存储器中读出相应的请求信息;

④请求处理模块根据读出的请求信息按照请求位的状态和顺序,产生与之对应的该通道的VL校验应答信号;

⑤根据产生的应答信号对相应通道进行VL校验,并存入帧信息数据存储器中,以供后续模块处理。

2 模块设计

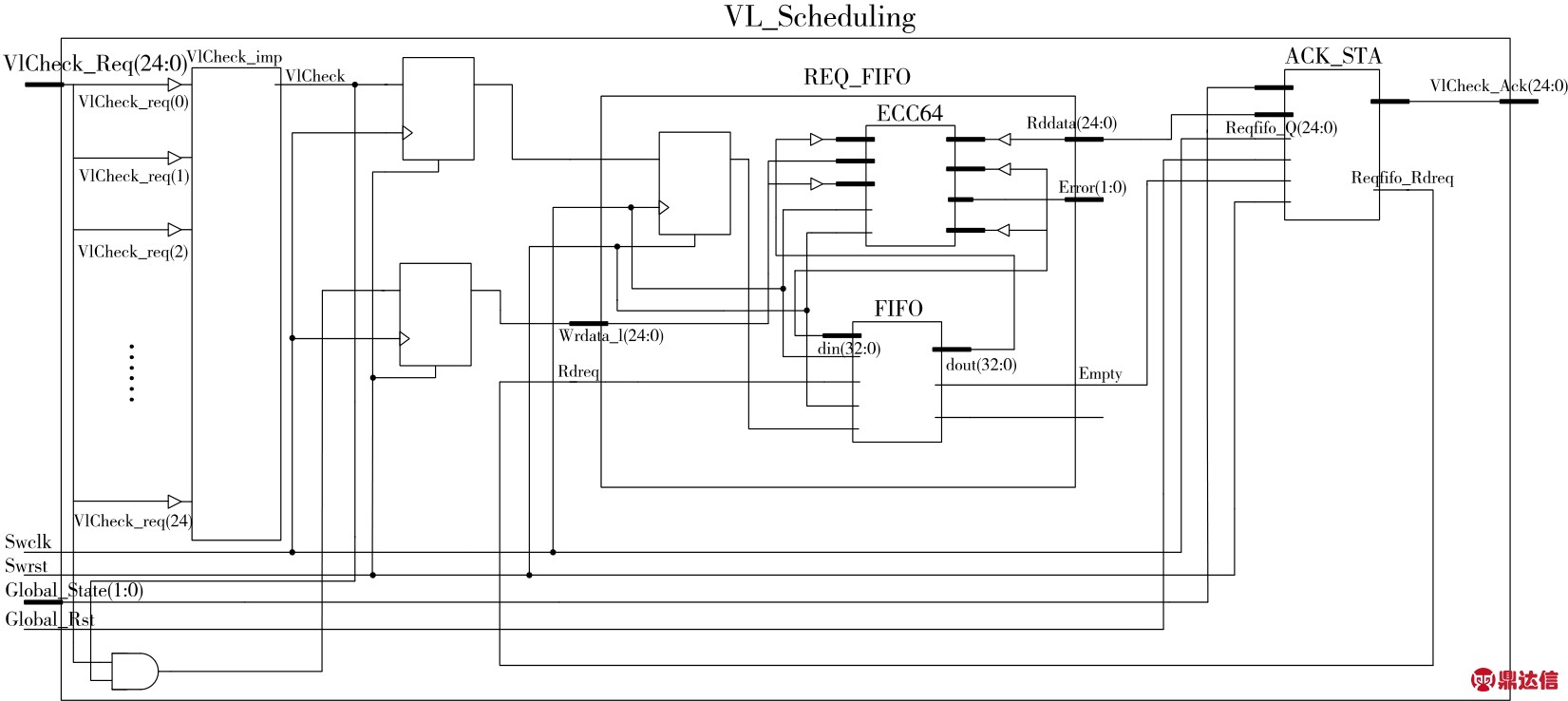

本文设计的链路调度模块由一个存储器FIFO、一个64位的错误检查和纠正模块ECC64及请求处理模块ACK_STA组成,如图2所示。FIFO用于存储AFDX交换机端口请求信息,并采用汉明码实现检查和纠错功能(ECC64模块)。ECC64模块利用64位的数据和8位优先级检查并改正所有1位错误,同时检查所有的2位错误。ACK_STA模块用于处理请求信号,产生应答信号,从而作为一个时间控制口,为后续每个端口的数据处理提供VL入口。

图2 链路调度模块结构图

当AFDX交换机处于正常工作状态时,在某个系统时钟的上升沿,部分通信口同时发出VL校验请求(对应VL校验请求信号VlCheck_req在该位产生一个时钟周期的高电平)。VlCheck_imp模块对所有的请求信号进行综合处理后,向REQ_FIFO模块发出写申请。REQ_FIFO模块包括64位错误检查和纠正模块ECC64和存储器FIFO。VL校验请求信号VlCheck_req经过ECC64模块,得出64位的数据和8位的优先级校验位。当存储器FIFO非满时,将数据信息和校验位存入FIFO中,等待ACK_STA模块进行处理。当FIFO非空时,ACK_STA模块从FIFO中读取数据,采用Round Robin调度机制,进行状态转换,从而产生VL校验应答信号VlCheck_Ack,供后续模块处理。

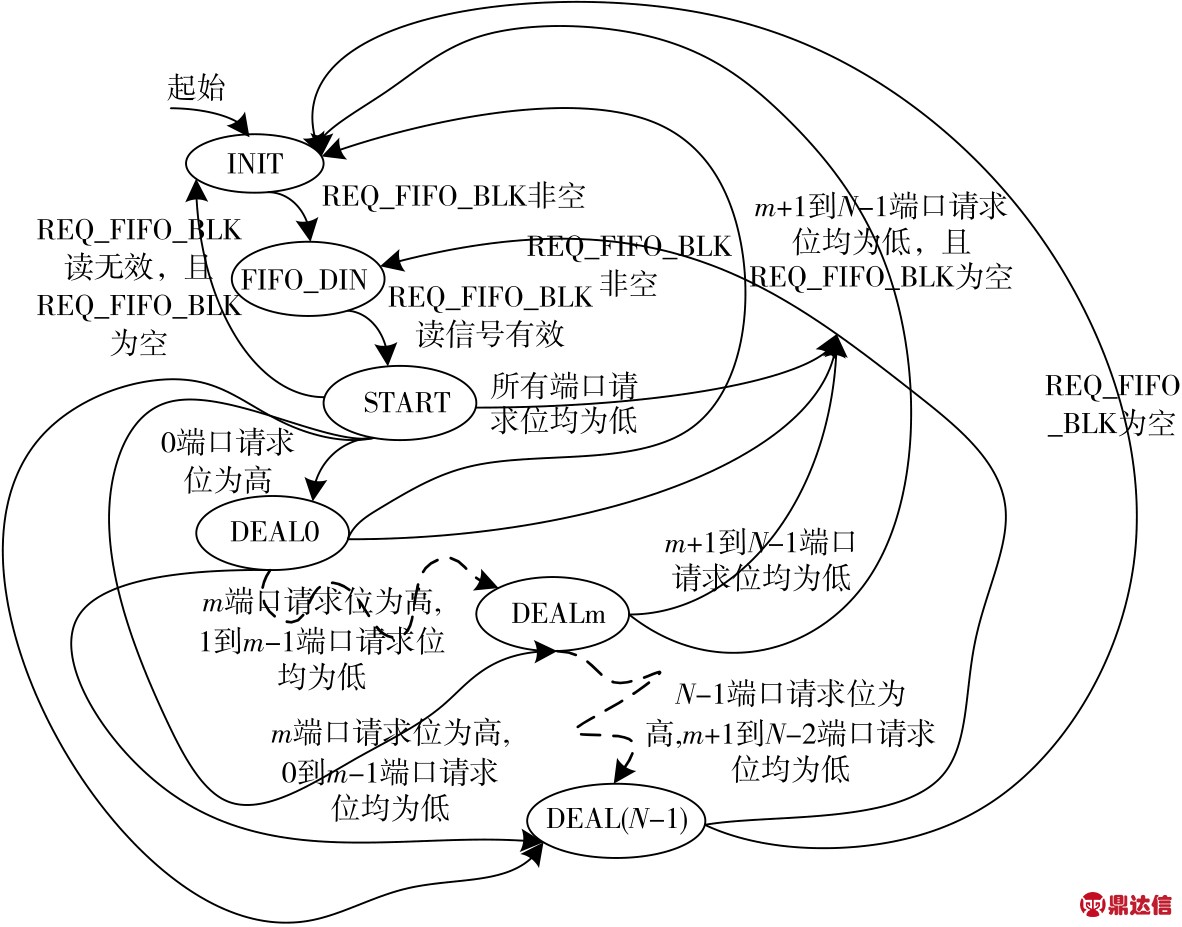

ACK_STA模块状态描述如下:

①系统起始时,ACK_STA模块进入INIT状态;

②当ACK_STA模块处于INIT状态时,如果FIFO非空,则进入FIFO_DIN状态,否则仍停留于INIT状态;

③当ACK_STA模块处于FIFO_DIN状态时,若FIFO读信号有效,则状态机进入START状态,否则仍停留于FIFO_DIN状态;

④当ACK_STA模块处于START状态时,若第n端口请求位为高,且前n-1端口请求位为低,则进入DEALn状态;若所有请求位均为低,且FIFO非空,则进入FIFO_DIN状态,反之FIFO为空,则进入INIT状态;

⑤当ACK_STA模块处于DEALm状态时,若第n(n>m)个端口请求位为高,且第m+1到第n-1个端口请求位为低,则进入DEAL(n)状态;若第m+1到第N-1端口请求位均为低,且FIFO非空,则进入FIFO_DIN状态,反之FIFO为空,则进入INIT状态;

⑥当ACK_STA模块处于DEAL(N -1)状态时,若FIFO非空,则进入FIFO _DIN状态,反之FIFO为空,则进入INIT状态。

ACK_STA模块状态图如图3所示。

图3 ACK_STA模块状态图

3 仿真验证

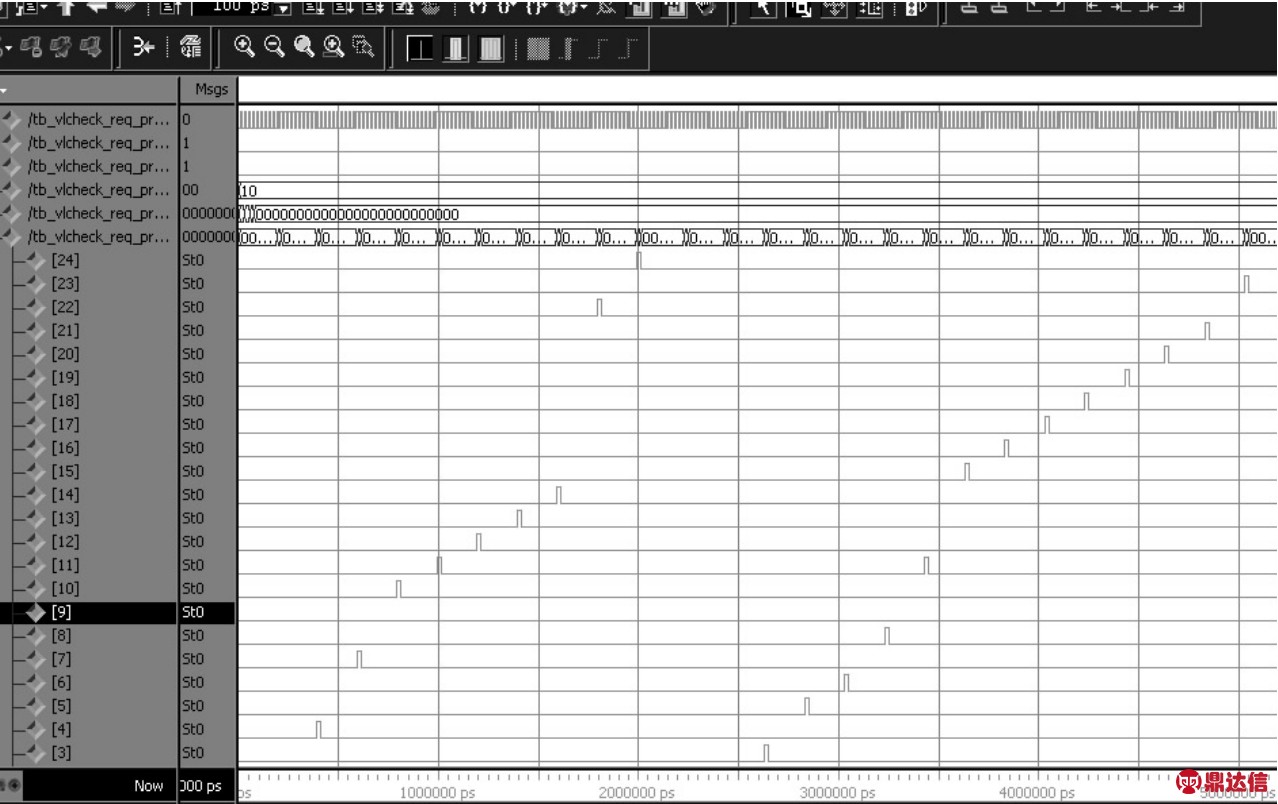

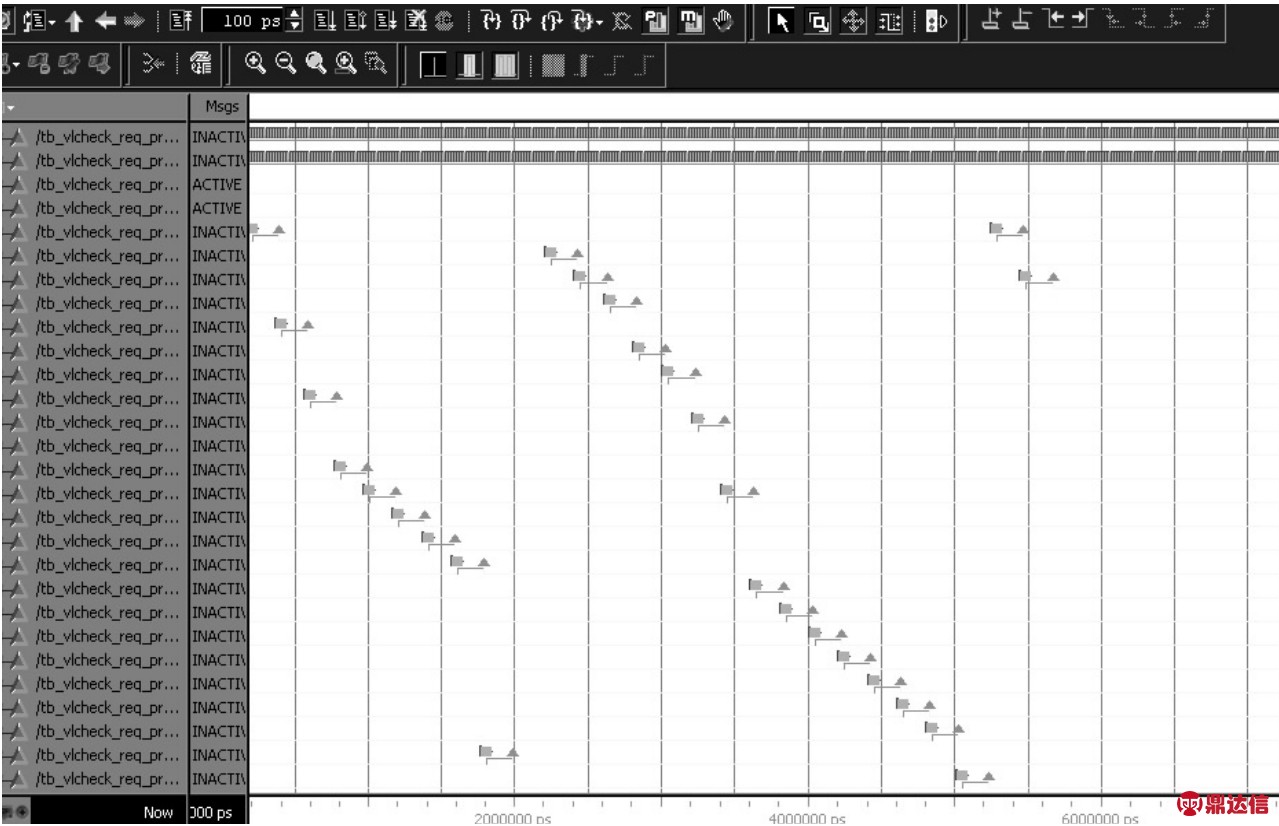

本设计利用Mentor公司的Questa 6.6进行功能仿真,时钟设置为50MHz,设定AFDX交换机整体复位信号和工作状态信号的状态,模仿一个或多个端口的发送请求信号作为激励,对该模块进行测试。测试波形如图4所示。

图4 仿真波形

图中所展开信号的每一位分别对应一个AFDX交换机端口,从仿真波形可以看出,本文设计的模块能够根据所有端口的校验请求,产生有序的链路校验应答信号,满足AFDX交换机链路调度模块的设计要求。

此外,本设计采用SVA(System Verilog Assertions)对复位后各信号状态、应答信号的保持周期及写入FIFO和从FIFO中读出的请求信号进行检测。当ACK_STA模块响应某端口的请求信号时,此端口对应应答信号的该位产生1个时钟周期的高电平,然后保持9个时钟周期的低电平。部分端口断言测试代码如下:

property port0_dataflow;

@(posedge Swclk) disable iff(Swrst||Global_Rst||(Global_State==′Global_State_INIT))

(ACK_STA.Reqfifo_Q[0]==1′b1)&&((VlCheck_Ack[24:1]==24′d0)&&(VlCheck_Ack [0]==1′b1))|->##1(VlCheck_Ack[24:0]==25′d0)[∗9];

endproperty

assert property(port0_dataflow);

其断言测试结果如图5所示。

图5 断言测试结果

图中一个“方块”代表一处断言的开始,一个“三角”代表一处断言成功通过。从测试结果可以看出,本设计满足AFDX交换机链路校验模块对请求信号的时序要求。

4 结束语

本文设计的链路调度模块主要应用于航空电子系统的AFDX交换机,它利用FPGA实现接收交换机所有端口的请求处理功能。本文在Questa 6.6下完成了仿真,并采用xilinx公司的Virtex5系列FPGA器件进行综合、布线后下载到电路板,在AFDX交换机板卡上通过了验证。实验结果表明,本设计有效地保证了AFDX数据帧转发顺序与接收顺序的一致性,符合AFDX交换机端口对数据帧请求处理的要求,满足新一代航空电子设备中数据通信的要求。