摘 要:介绍一种基于FPGA和DSP、高速串口驱动芯片、电源芯片、时钟芯片等硬件结构耦合设计的高速串口通信方法,使用芯片内核,通过软件编程实现高速串口通信平台。系统通过DSP进行通信数据组包、解析、纠错;FPGA实现高速率设计、串口时序转换、数据交互;结合高速串口驱动芯片和串口调试终端实现高速数据传输。装置通信速率可达到10 Mb/s,数据传输可靠性高,在机载和地面设备中可广泛应用。

关键词:高速率;串口通信;DSP;FPGA;误码率;可靠性

在数字通信领域中,串口通信作为一种通用手段,广泛应用于任务处理机、监控台、模拟器等通信设备中。简单的低速串口传输在实时性要求高、数据量大的机载、地面系统进行人机交互的远程测控中,不能满足硬件扩展和调试要求。本文设计了一种基于DSP+FPGA的硬件平台。DSP芯片具备普通微处理器的运算和控制功能,FPGA芯片发挥其快速性、设计的灵活性、可移植性、逻辑资源密度高等特点。将两者功能耦合设计,使用芯片内核和相应语言编程,结合电源芯片、时钟芯片、高速驱动芯片等完成串行数据高速精准传输。

1 高速串口传输系统硬件结构

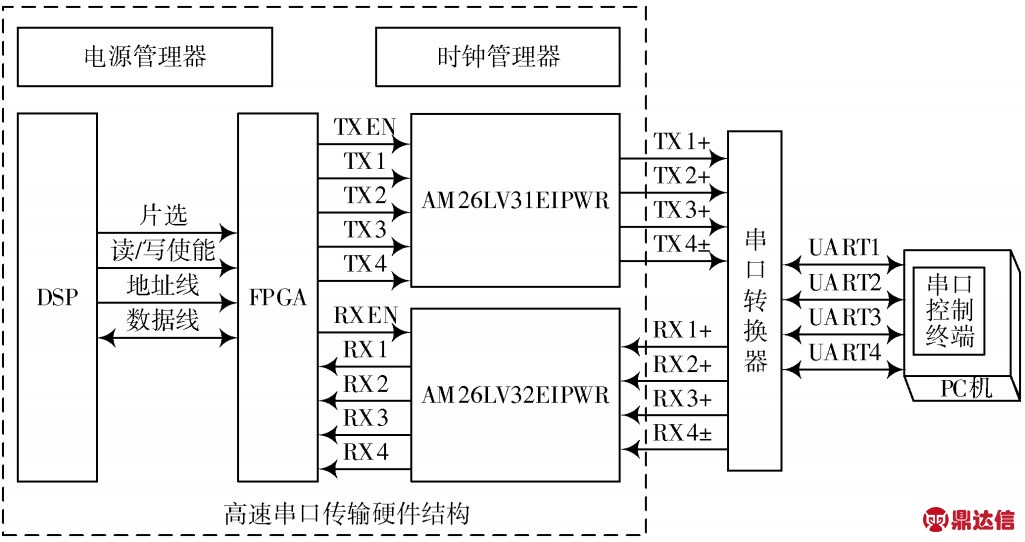

系统硬件架构如图1所示,由电源管理器、时钟管理器、高速串口驱动芯片AM26LV31E和AM26LV32E,DSP,FPGA等模块构成,结合多串口转换器、PC机中的串口控制终端协同工作。

电源管理器为系统各模块提供工作电源。外部稳压源输入系统5 V电压,由电压管理器分别生成1.0 V,1.2 V,3.3 V 电 压 ,为 DSP,FPGA,AM26LV32E,AM26LV31E等模块提供工作电压。

时钟管理器为系统中各模块分配工作时钟,确保系统中DSP和FPGA的工作时钟稳定可靠。

DSP模块具有高度集成性,具备多种存储器接口,带有DMA通道控制器,保证数据传输和计算处理并行工作,编程方便,容易实现,精度高、稳定性好、抗干扰能力强等特点,在本系统中承担运算和控制功能。DSP通过外部存储器接口EMIFA中的片选线、读写使能线、地址线、数据线与FPGA模块连接[1]。在DSP调试软件CCS4.2中使用C语言和汇编语言进行编程,实现数据组包、解析、纠错、指令控制等。

图1 高速串口传输系统硬件结构

Fig.1 Hardware structure of high⁃speed serial transmission system

FPGA模块具备处理速度快、逻辑资源密度高等特点,在本系统中承担数据收发、指令交互、时序转换、数据存储等工作[2]。FPGA的通用输入输出引脚分别与DSP模块、串口驱动芯片相连[3]。FPGA通过在ISE 14.7开发环境中使用VHDL语言编程,在ModelSim SE 10.4中仿真模拟,调用DCM内核、RAM内核等资源,生成串并转换时序、存取数据、指令收发、信息交互等。

基本的UART通信需要4条信号线:接收端RXD±和发送端TXD±。UART数据发送和接收的帧格式,低位先传:第一位为起始位,置“0”,表示通信开始;最后一位为停止位,置“1”,表示通信结束[4]。本系统选用TI公司的AM26LV31E和AM26LV32E完成高速串口驱动。通过芯片使能线和4路数据线将FPGA与AM26LV31E模块、AM26LV32E模块连接。AM26LV31E支持4路RS 422数据发送单端转差分,最高转换速率为32 MHz,4路共用一组使能控制线。AM26LV32E支持4路RS 422数据接收差分转单端,最高转换速率为32 MHz,4路共用一组使能控制线。AM26LV31E模块接收FPGA发送的使能信号、4路数字信号。AM26LV32E模块接收FPGA发送的接收使能信号,发送4路数字接收信号至FPGA。本系统RS 422作为平衡通信接口,可实现10 Mb/s的传输速率。4路RS 422信号经过9针D型串行接口通过串口转换器合并连接至PC端机。

2 软件架构

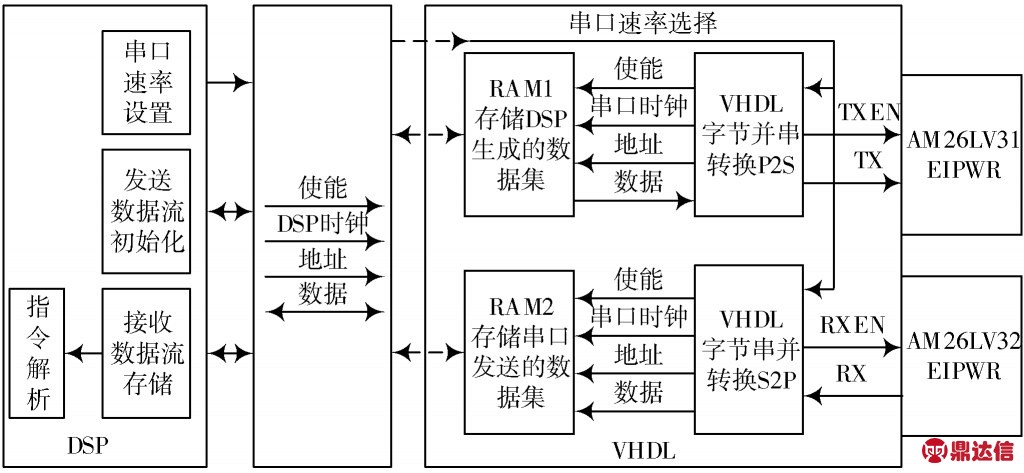

高速串口传输系统软件架构如图2所示。

2.1 高速波特率的实现

针对数据传输需求,将串口传输速率设为可调模式,包括三档速率:115.2 Kb/s,1.44 Mb/s,10 Mb/s。在DSP中控制串口速率,FPGA中配置相应的DCM核进行分频。用不同的波特率控制串口收发。串口调试终端按协议发送、接收数据,实现通信交互[5]。

图2 高速串口传输系统软件架构

Fig.2 Software structure of high⁃speed serial transmission system

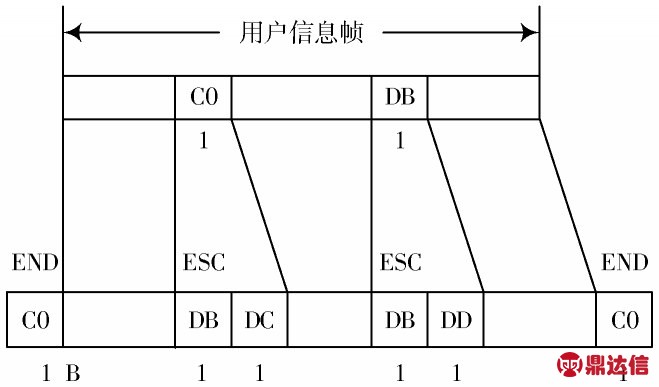

2.2 SLIP封装协议

RS 422串口通信采用SLIP封装协议。SLIP是一个面向字符的协议,在每个用户信息帧的首尾各加一个特殊的标志字节,封装成为SLIP帧,如图3所示。标识字节的编码为0xC0。 若用户信息帧中的某一个字节与0xC0一样,那么将该字节更换成0xDB,0xDC。这里的特殊字符0xDB称为SLIP转义字符。本系统中,在DSP中完成数据包封装和解析。

图3 SLIP封装

Fig.3 SLIP packaging

2.3 配置两个双口RAM

为解决数据的存取和采样时钟不匹配问题,系统使用FPGA内部两个双口RAM,分为A,B两个接口模块[6]。串口数据在RAM_A模块中存储转换,数据8比特位传输,地址设置为8位。系统处理数据在RAM_B模块中存储转换,数据16比特位传输,地址设置为7位。

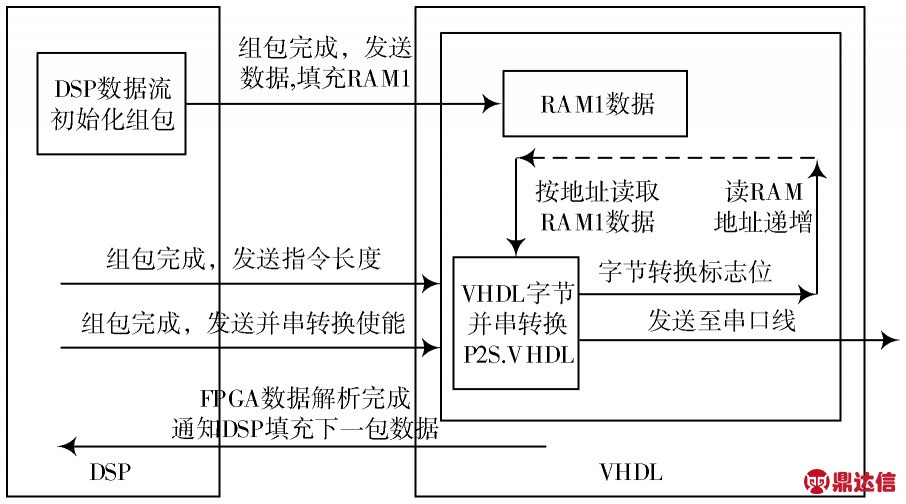

2.4 DSP传输数据至串口通信流程

DSP数据传输至串口通信流程按一包数据完成一个进程,具体流程如图4所示。DSP内部首先完成数据包初始化。在初始化时,将上文提到的SLIP协议应用在组包过程中。DSP发送数据包长度、串并转换使能信号给FPGA,准备转换。在FPGA中用VHDL编写的串并转换文件(P2S.VHDL),将DSP控制的串口速率作为时钟采样。FPGA中RAM1的A模块接收P2S.VHDL文件。A模块CLKA为DSP配置的高速串口速率,WEA始终为“0”,A模块始终处于读状态。P2S.VHDL文件每运行一次生成10位串行数据和并串转换结束标志位。其次,串行数据实时输出。而后,并串转换结束标志位控制RAM1的A模块读地址增加,将读取的字节依次输入P2S.VHDL文件,直至转换完全部数据包长度的数据。在一包数据转换结束后,FPGA发送回握手信号。通知DSP一次解析完成,继续填充下一包数据[7]。

图4 DSP数据传输至串口通信流程

Fig.4 Communication process of data transmitted from DSP to serial port

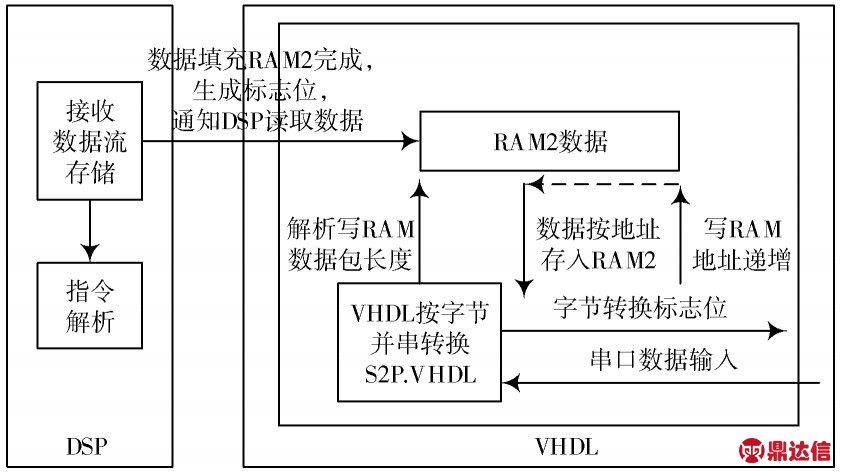

2.5 串口传输数据至DSP通信流程

串口数据传输至DSP通信流程按一包数据完成一个进程,具体流程如图5所示。

图5 串口数据传输至DSP通信流程

Fig.5 Communication process of data transmitted from serial port to DSP

在FPGA中用VHDL编写的串并转换文件(S2P.VHDL),将DSP控制的串口速率作为时钟采样[8]。FPGA中RAM2的A模块接S2P.VHDL文件。RAM2的A模块WEA置“1”,A模块处于写状态。数据从串口调试终端输入FPGA中,S2P.VHDL文件每运行一次生成一个字节和串并转换结束标志位。首先,对第一字节进行有效性判断。第一字节为0xC0,代表本包数据有效,则进入第二字节判断;否则,丢弃本包数据。其次,对第二字节进行数据包长度判断。第二字节为0x11,0x12,0x13等,解析数据包长度具体对应如表1所示。将解析的长度值作为本次填写RAM2的总长度。同时,RAM2的A模块ADDRA根据串并转换进程结束后生成的标志位进行递增,依次存储数据。将转换的字节依次填入RAM2中,直至写入全部数据,完成RAM2初始化。此时一包数据存储完成,生成标志位返回DSP中断。DSP判断中断到来进入指令解析步骤[9]。

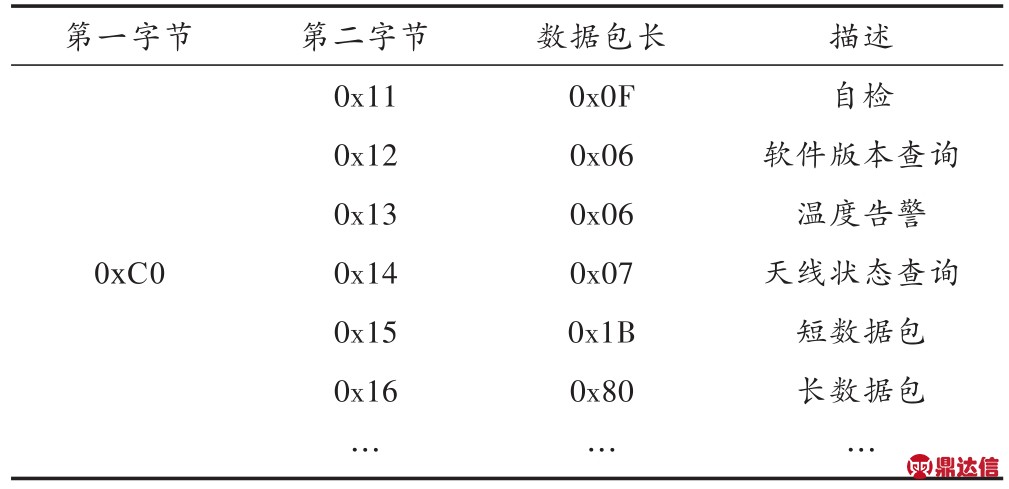

表1 解析数据包

Table 1 Parsing packets

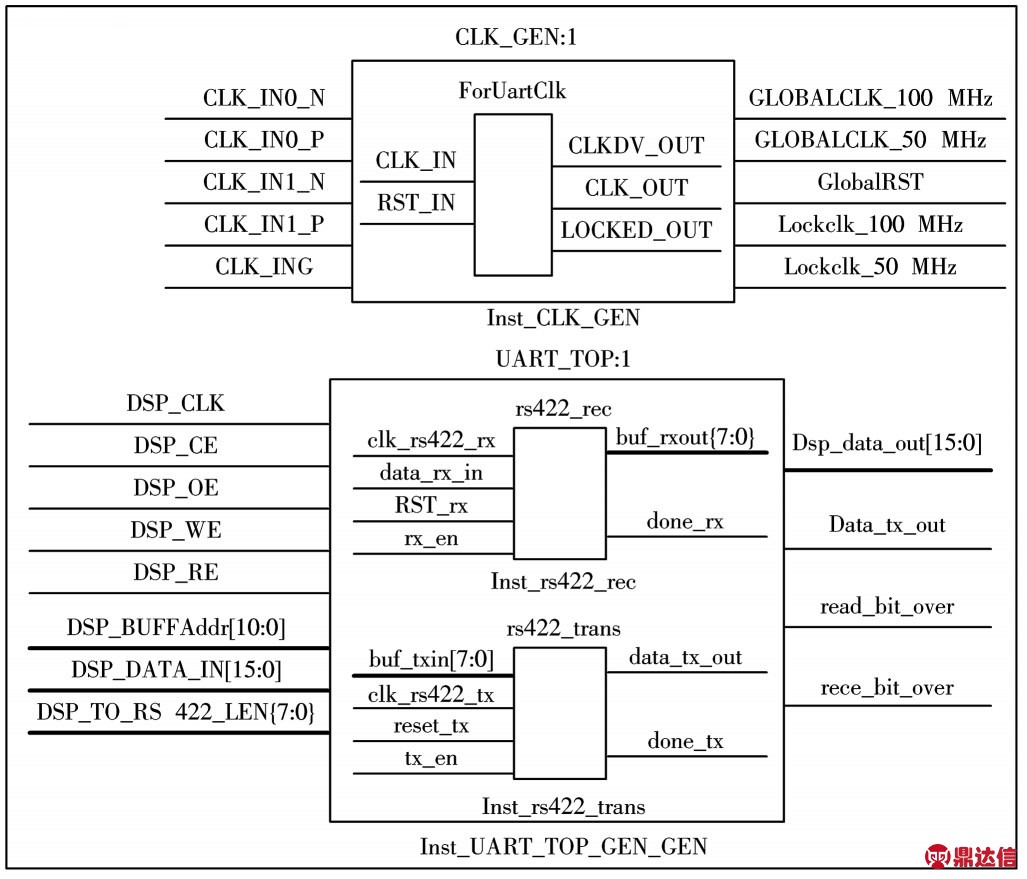

2.6 系统设计的RTL

系统设计的部分RTL如图6所示,由串口发送模块(rs422_trans)、串口接收模块(rs422_rec)、波特率发生器(CLK_GEN)3个模块组成。其中,波特率发生器产生可调的串口采样时钟。UART_TOP模块即串口收发顶层模块实现各模块间的信号连接。rs422_trans模块负责数据串并转换,rs422_rec模块负责数据并串转换。

图6 RTL可视图

Fig.6 RTL visible picture

3 测试结果

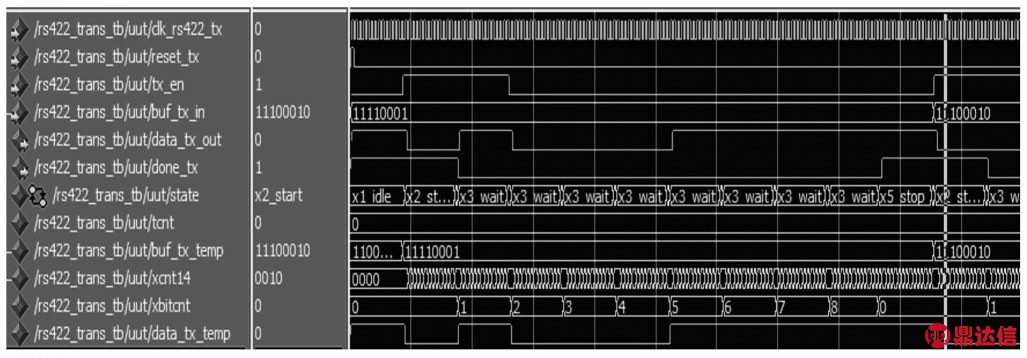

3.1 仿真测试结果

本系统在ModelSim 10.1环境中进行验证[10]。模拟DSP发送数据并串转换,仿真结果如图7所示。当buf_tx_in输入为“11110001”时,data_tx_out按时钟输出“0,1,0,0,0,1,1,1,1,1”,done_tx在转换结束后输出“1”。

图7 DSP发送数据并串转换

Fig.7 Parallel⁃serial conversion of data sent by DSP

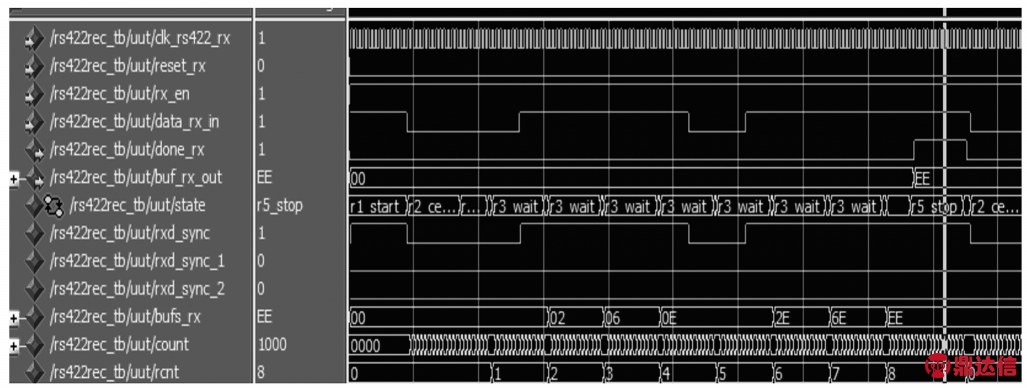

模拟串口发送数据串并转换,仿真结果如图8所示。当data_tx_in按时钟输入“0,0,1,1,1,0,1,1,1,1”,buf_rx_out输入为“0xEE”时,done_rx在转换结束后输出“1”。

图8 串口发送数据串并转换

Fig.8 Parallel⁃serial conversion of data sent by serial port

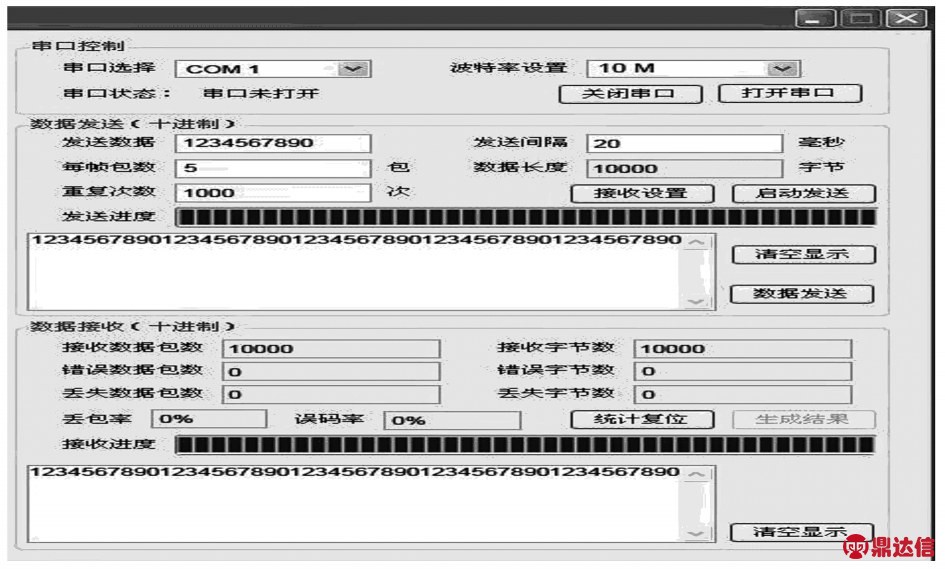

3.2 硬件测试结果

PC端机中设有串口测试终端。测试软件在Visual Studio 2010平台上使用C++语言编程。终端界面负责下达、数据收发检测、实时状态上报、误码率判断等工作。如图9所示,测试时将波特率设定为10 Mb/s,以十进制发送数据包“123456789”,验证串口传输误码率。重复次数为10 000次时,误码率为0。验证了该通信方法的可靠性。

图9 串口测试终端

Fig.9 Test terminal of serial port

4 结 语

本文方法在任务处理机原有的硬件平台上,以DSP+FPGA为基础开发,结合电源管理模块、时钟配置模块、驱动芯片AM26LV31E和AM26LV32E实现串口高速传输功能。重点介绍了系统的硬件设计和软件架构。DSP通过外部存储器接口EMIFA与FPGA模块连接,使用C语言和汇编语言编程,实现数据组包、解析、纠错、指令控制等。FPGA的通用输入输出引脚分别与其他芯片相连,使用VHDL语言编程,在ModelSim SE 10.4中仿真模拟,设计实现UART协议电路,使用较少的资源实现高速串口通信,可移植性高。在工程应用中结合串口调试终端与PC机通信,实现串口通信无差错传输,速率可达到10 Mb/s。该系统可根据需求加入数据校验方法,对数据包进行加解密保护;可选择不同的串口速率进行高速、大容量的数据传输,可靠性和稳定性能完备;满足了实时性要求高、数据量大的数字通信系统通信需求,硬件扩展性强,可靠性高、调试直观,可广泛应用于机载和地面设备中。