摘要:由于FPGA配置存储器具有掉电易失性,系统设计中的主控器需要操纵非易失性存储器对其进行配置;另外,在某些系统工作过程中需要对FPGA配置码流进行实时更新以升级系统,对FPGA码流进行回读以获取系统的实时工作状态;针对这些需要,设计并实现了一种基于串口通信的 FPGA配置控制方法:以CPLD作为配置主控器,通过串口对CPLD的工作状态进行控制,成功实现了Flash的擦除、烧写、FPGA配置以及回读功能;由于串口协议比较简单,只需简单的转换就可完成与其它传输协议的交互,使得设计的配置控制方案具有比较好的可移植性和通用性。

关键词:串口通信;现场可编程门阵列;Flash;配置

0 引言

SRAM型FPGA由于具有比较高的集成度和很强的逻辑功能,并且可无限次重复擦写,被广泛应用于现代数字系统的设计中。由于FPGA配置存储器的易失性,每次系统重新上电时,都需要对其重新进行配置。在进行系统重构或改变系统工作模式时,往往也需要对FPGA进行在线重配置,以获得更加灵活的设计和更加强大的功能。在这些过程中,如何根据系统的需求,快速高效地将配置数据写入FPGA,对其进行在线重配置,是整个系统重构的关键[1]。

本文根据Xilinx产品手册及相关文献开展的研究,设计了一种新型基于串口控制的FPGA配置控制方案。当Flash存储器需要更新时,可通过网络或者上位机由串口向CPLD发送Flash写指令,向Flash的特定存储位置写入配置数据;当系统需要更新时,可通过串口向CPLD控制器发送配置命令,重新配置或部分配置FPGA;在需要对FPGA进行回读操作时可以通过串口向系统发布回读指令,对FPGA进行全配置码流回读或者指定帧数码流的回读。通过串口和CPLD间的通信完成CPLD控制状态实时切换,不仅节约了成本,还有效地缩小了系统体积,有利于系统后续的升级更新[2]。

1 方案设计

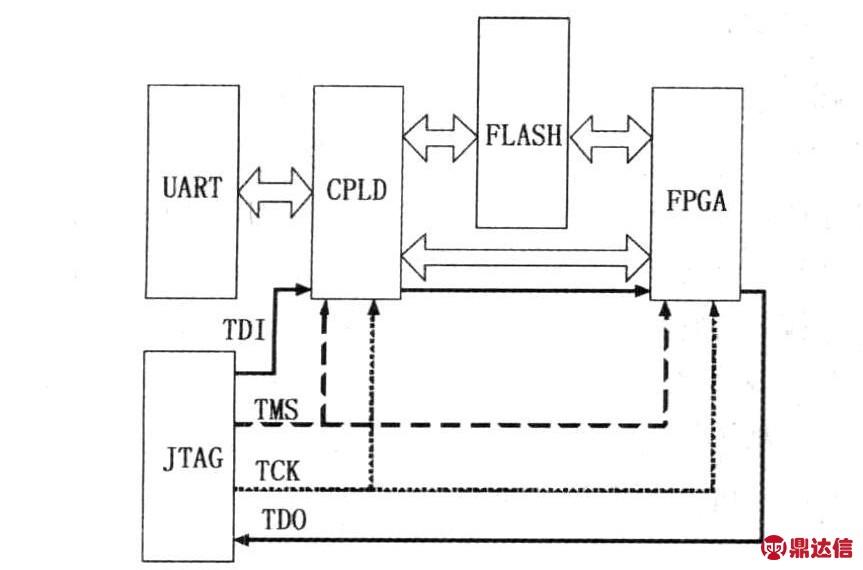

由于CPLD的可重构以及掉电非易失特性,在围绕FPGA架构的系统设计中经常将其作为主控器实现相关配置和升级控制功能,图1所示为设计方案整体的结构框图,由UART接口、CPLD、Flash存储器、FPGA、JTAG接口以及相应的外围辅助电路构成。通过串行通信接口与CPLD的实时交互,完成特定指令对应的操作。可以通过上位机与UART间的通信完成本地相关控制功能;也可以将整个系统作为网络终端,通过将解码后的有线网络传输协议或者无线射频传输协议转换为串口传输协议的方式完成远程配置控制功能[3]。由于串口传输过程只需要两根信号线:传输线TX以及接收线RX,传输协议简单,可以很方便地完成与其它高端传输协议的交互,使得这种配置控制方案具有比较好的通用性,通过附加不同模块完成系统间的快速移植。

除用于配置控制所需的结构模块外,系统还保留了JTAG扫描链结构模块。这一设计主要是为了兼顾开发阶段系统调试的需要,在调试成功以后,将设计的控制码流下载到CPLD中,可以完成预期的各项系统功能;在需要对CPLD的配置控制功能进行升级时,也可以通过JTAG接口实现。

2 方案实现

2.1 系统硬件设计

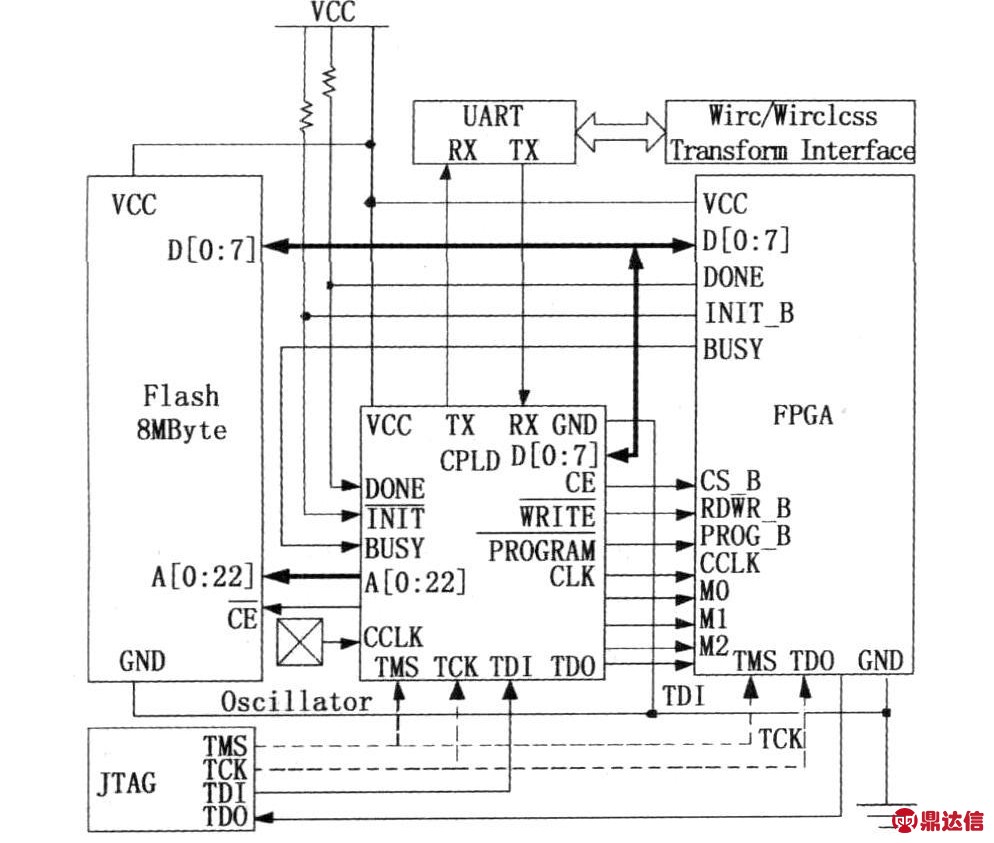

根据方案设计部分的描述,本文实现的配置控制系统电路图如图2所示:FPGA与配置相关的各个管脚均与控制CPLD的特定管脚相连,通过CPLD可以控制FPGA处于配置还是回读状态,还可以通过控制配置模式选择位选择FPGA是通过串行还是并行模式进行配置;此外,可以通过CPLD对flash存储器进行控制。由于串口传输协议具有很广泛的通用性和很好的易用性,很容易与其它协议进行交互,通过串行接口向CPLD发送命令以及收发数据时,可以通过有线或者无线的方式进行。即便是在本地控制模式下,串口本身也可以传递比较远的距离,因此本文设计中选择串口对配置进程进行控制。

图1 FPGA配置控制硬件框图

在应用串口进行传输时,首先要对通信双方的波特率、数据位数、停止位、校验位等需进行统一。本文设计中采用PC机作为控制的上端直接接入到电路的串行接口上,PC机的串口电平值为+12V~-12V,CPLD是 TTL电平 (0~+5V),硬件设计过程中必须用电平转换芯片进行两者电平间的转换[4]。

图2 FPGA配置控制电路图

2.2 系统软件设计

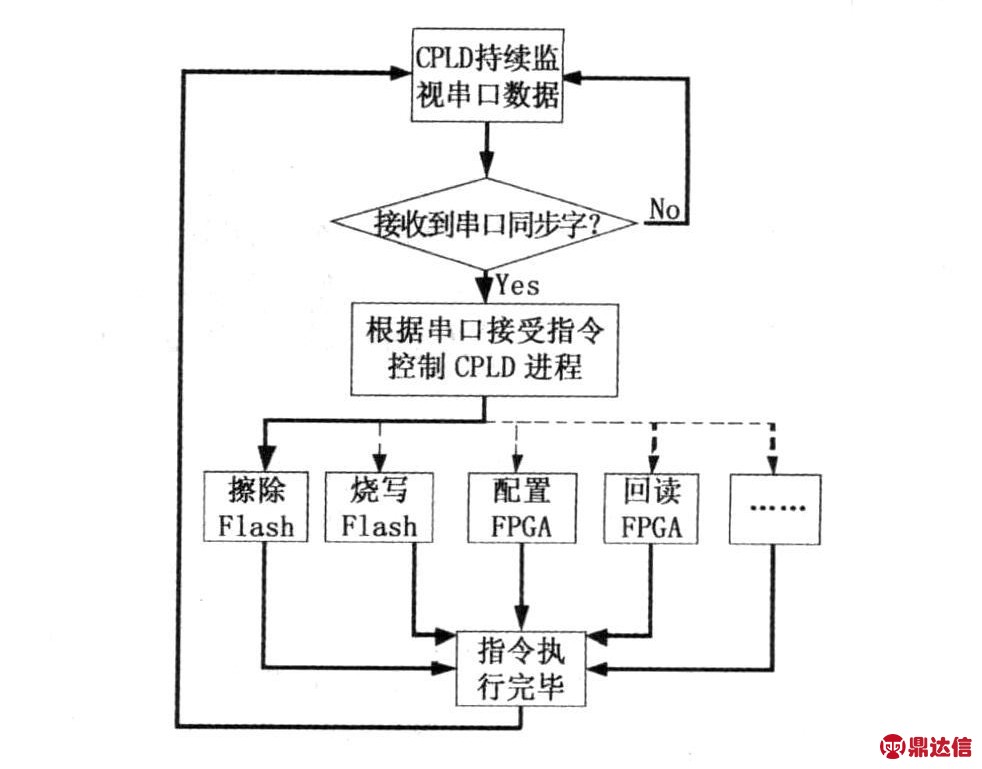

结合系统硬件结构以及配置方案设定的控制功能,文中采取图3所示的控制流程:进入正常工作状态的CPLD将持续监视串口,根据接收到的命令执行相应功能。

由于串口只有收发两根信号线,传输数据过程中双方无法就信号的性质进行交流。本设计在串口传输命令字时在前面附加同步字,CPLD在接收到同步字后,会将接下来的一个字节视为命令,本文采取表1所示的同步字和指令命名规则进行控制程序的开发。当需要开发新的控制功能时,可以在表1的基础上添加新的命令字。

图3 FPGA配置控制流程图

表1 串口指令列表

如图 3所示,根据接收指令 CPLD可实现 Flash擦除、Flash烧写、FPGA配置及FPGA回读等主要功能,以下将分别对其实现流程进行简述。

Flash擦除:对Flash特定地址对应的存储空间进行写操作之前,需要以存储块为单位对其进行擦除[5]。因此在Flash擦除命令之后要发送待擦除块的起始地址与连续擦除块个数,擦除结束后,CPLD将向上位机反馈如表1所示的成功标志。

Flash烧写:与Flash的擦除操作类似,命令发送端需要连续发送烧写命令以及待写入存储空间的起始地址,接下来发送需要向Flash烧写的定量的配置数据。

FPGA配置:在对FPGA进行全局配置时,CPLD首先拉低FPGA的PROGRAM端口以完成FPGA配置初始化,然后根据配置命令发送的起始地址,将从flash读取的数据依次写入FPGA配置数据接收端口,通过检测DOWN判断配置是否成功;若要对FPGA进行部分配置,则不需要在配置之前进行初始化[6]。

FPGA回读:在FPGA的回读指令之后,需要通过串口将回读帧的起始地址以及连续回读帧的长度发送给CPLD,在回读过程中,CPLD可以通过串口将回读数据发送给上位控制端。

基于串口传输协议中对于校验位的描述,数据接收端可以通过校验结果判断接受数据的正确性,当检测到错误的时候,可以通过实时向发送端反馈错误标志以要求数据重发。在系统调试过程中,串口收发程序选择的运行于PC机上的串口调试助手。在下一步工作中,将根据配置控制任务的要求开发专用的串口控制程序。

3 试验结果分析

为了验证文中设计的配置控制方法的可靠性,在CPLD的控制下通过串口向Flash中烧写完整的FPGA跑马灯配置码流数据,然后通过串口读取写入flash的数据,对比回读数据与原配置数据,两者的一致性表明控制系统可以可靠地实现flash读写功能。

通过串口发送全局配置指令以后,DOWN灯被点亮,四个被控指示灯轮流点亮,达到了预期的效果。接下来将跑马灯程序改为闪烁灯程序,应用ISE命令生成部分配置文件,将其写入擦除后的Flash存储空间,然后通过串口向CPLD发送部分配置指令,PC机收到串口反馈的成功标志后,观察到4个指示灯同时闪烁。预期用户功能的顺利实现表明配置控制系统可以成功实现FPGA配置以及部分配置功能。由于FPGA配置过程中内部同时在对码流进行循环冗余校验(CRC),只有配置码流通过CRC校验后才允许FPGA进入启动时序,这就说明通过串口控制的配置控制程序传输数据具有很好的可靠性。

通过PC机端串口调试助手向CPLD发送配置存储器回读指令,对上述配置后的FPGA进行回读操作,对比接收到的回读数据与原始码流中的数据,除去回读码流中可变寄存器位外两者完全一致,这一结果表明系统可以可靠地实现FPGA回读操作。以上试验结果分析表明本文设计的系统能够完成预期的各项功能,基于串口控制的配置控制方法具有比较好的可行性和可靠性。

4 结论

本文根据基于FPGA的数字系统对于配置控制以及系统在线部分重构的需求,开发了一种基于串口控制的FPGA配置控制系统,根据串口指令CPLD分别工作于不同的状态下,灵活地完成对Flash擦除、Flash烧写、FPGA配置以及回读操作。串口的简单和通用性使得本文开发的配置控制系统具有很好的可移植性,经过扩展该系统可以很方便地应用到需要对FPGA工作系统进行升级的场合。