摘 要:系统对LED全彩屏扫描控制板做了一个全新的架构设计,即采用C8051F340单片机+FPGA作为主控模块实现逐点控制和全彩画面显示。运用单片机的灵活性和多功能性特点,完成了显示屏内温湿度采集、供电电压监测、屏外环境亮度监测、与上位机通信和对FPGA的配置和控制。FPGA作为高速器件完成显示数据收发和扫描。采用恒流驱动芯片MBI5036实现LED恒流驱动。

关键词:C8051F340;FPGA;全彩显示;逐点控制;高速传输

0 引言

LED显示屏最早出现在1970年代,随着电子工业技术的发展和人民生活水平的提高,LED显示屏已被用到交通信息引导、广告传播、建筑装饰、舞台背景、广场大屏幕等方面。LED显示屏也从简单的文字信息屏发展到高清全彩的视频播放显示屏,可以直接接收DVI、VGA和有线电视视频信号。全彩LED显示屏作为节能产品一直存在成本高,自我监测能力弱,亮度不均匀的缺点。本论文就这些方面提出解决方案。

1 关键器件选择和总体结构设计

1.1 器件选择

1.1.1 CPU 选择

由于CPU要完成与上位机通信,进行温湿度、电压、亮度采集,对FPGA进行配置和控制。因此要求选用的单片机有AD模块,串行通信、I2C、和多路I/O。因此本系统选用C8051F340,C8051F340有一个10位ADC模块,ADC模块17个外部输入,64KB的闪存,一个I2C,40个I/O,最高总线时钟达48MHz,同时它的I/O为多功能复用管脚,有交叉开关可以灵活配置个个模块接口。

1.1.2 FPGA配置程序存储器选择

FPGA选择工作在被动状态,为了节省成本和充分利用单片机资源,由单片机配置FPGA,因此要一个稳定可靠的存储器存储FPGA配置程序。为此选择存储芯片M25P80,M25P80为SPI串行Flash存储器,容量为64Kbit具有先进的写保卫机制。M25P80在配置程序下装后写保护,可保证FPGA每次上电被正确配置。

1.1.3 FPGA 选择

FPGA选用Altera公司Cyclone系列EP1C3T144。EP1C3T144有2910个逻辑门、13K RAM、1个锁相环、104个用户I/O。

EP1C3T144为低端系列FPGA,因为与单片机配合工作,因此完全能满足要求。一个EP1C3T144可扫描多达12个LED显示模块。外接25MHz时钟电路通过锁相环即可为FPGA提供100MHz以上的工作频率,足够满足显示数据接收、读写外扩存储器、扫描LED显示模块。13K RAM作为各种数据输入输出的缓冲区。

1.1.4 LED 驱动芯片选择

目前市场上显示屏存在亮度不均,色彩不稳定往往是由于驱动芯片不能恒流驱动造成的,在本系统中选用MBI5036作为驱动芯片。MBI5036恒流输出范围值:3~60mA,电流输出极为精确,通道间一般差异值:<±1.5%,芯片间一般差异值:<±3%,因此可以改善显示屏的这种缺点。同时MBI5036可以具有线路开路及线路短路侦测能力,为显示屏的保护维修提供方便。

1.2 总体结构设计

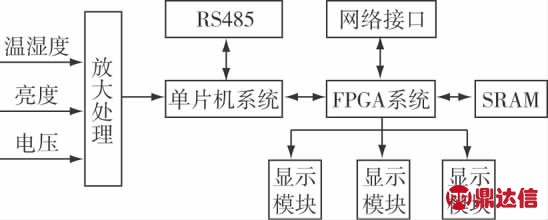

本系统电路分为两部分:扫描控制板和LED显示屏。扫描控制板主要分为两块即单片机系统和FPGA系统。单片机系统将温湿度、环境亮度、供电电压信号采集换算后传送给上位机,同时接收上位机指令控制FPGA工作。FPGA通过网络接收显示数据存入SRAM,并按显示模块布线规则将数据扫描出去。扫描控制板系统结构如图1。

图1 扫描控制板系统结构图

2 系统电路硬件设计

2.1 单片机系统电路设计

单片机系统电路处理器为C8051F340,复位芯片用TCM809SENB713,当供电电压低于1.8V是便会输出低电平复位单片机。温湿度传感器、光电池传回的电压和供电电压通过放大器LM358进行放大射随后送入单片机。RS485电平转换选用SN65HVD3082ED,这样可以省去隔离电源。SN65HVD3082ED的RO、DI接到单片机的RX、TX上,RE接到单片机I/O上使能RS485发送。24C04用来存储控制数据和显示屏大小等。SDA、SCL接到单片机I2C接口上,以便直接用单片机I2C总线读写24C04。FPGA配置程序存储器M25P80接到单片机SPI接口上。

2.2 FPGA系统电路设计

FPGA系统电路主要有网络接口、外扩SRAM、扫描驱动接口等。在锁相环输入接口上接25MHz有源晶振为FPGA提供时钟源。网络接口采用网络收发器VT6013,VT6013收发数据速度可达100M bps速率。数据接口为TTL电平,直接接到FPGA的I/O口上。在收发器与接口间采用网络隔离变压器11F-05NL。用SLVU2.8-4防护静电放电(ESD),闪电。它可满足单向路线的要求,以及双向要求无论是在一个共同的模式或差分模式配置。一幅画面的显示数据很多,EP1C3T144内部没有足够的RAM空间存储数据,因此要外扩SRAM存储显示数据。在此外扩SRAM采用IS63LV1024,将IS63LV1024的数据总线DATA、地址总线ADDR、读写和控制信号接到FPGA的I/O口上,由FPGA硬件产生控制信号读写数据。在FPGA扫描数据输出接口上加驱动器74HC244更大驱动能力和距离。

2.3 LED驱动电路设计

LED显示模块大小为16*16像素,LED驱动芯片为MBI5036,驱动芯片分为三组,驱动灯的颜色顺序为蓝绿红。每组由16个驱动芯片,数据线Do0送入Din,然后从UB0的Dout到UB1的Din,依次连接,最后从UR15的Dout输出接到接口的Di0,这样由FPGA的两个I/O口就可以完成一个显示模块数据扫描和错误侦测。驱动芯片上的数据控制端LE和输出锁存器使能端OE分别接到FPGA的LE0和OE0上FPGA的统一使能输出。MBI5036的R-RXT引脚上接1%的电阻选择芯片最大驱动电流。

3 系统软件设计

3.1 单片机系统软件设计

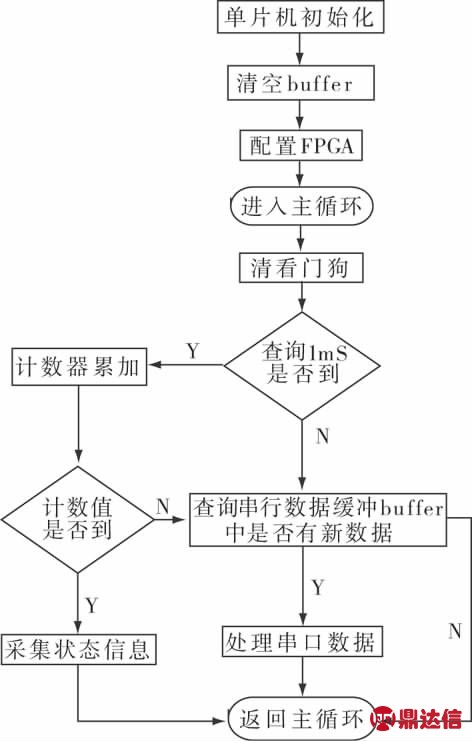

单片机由定时器2作为定时控制进行亮度、温湿度、供电电压采集,其它时间单片机不停的查询串口数据缓存区,如串口数据缓存区有新数据,则根据协议处理。定时器2定时中断时间为1mS。定时到1S时采集亮度、1.1S采集温度、1.2S采集湿度、1.2采集电压。每次采集的数据都做平均后存入buffer。串行数据接收,每次查询串口时,单片机先从串口接收环形缓冲区读数据。根据协议判断是否为协议内的数据,是则存入串口数据缓存区,每次接收到贞尾后对数据进行处理。程序流程图如图2所示。数据协议:

贞头:0x02(一个字节);

地址:0x01(一个字节);

命令:0x00(一个字节);

数据:0x04,0x05……(小于1000个字节);

校验:0x33,0x33(两个字节CRC校验);

贞尾:0x03(一个字节)。

3.2 FPGA硬件设计

FPGA中各个模块是并行工作的,每个信号好的传输和状态的转变都由时钟的上升沿或下降沿启动。

FPGA接收RGB数据,由时钟控制FPGA不断的读网络接口芯片数据到接收缓冲区(FIFO)。如果缓冲区数据不为零,则对数据进行判断,是自己的数据送入SRAM输入缓冲区,不是则送入网络发送缓冲区转发数据。

RGB数据存储,FPGA跟据IS63LV1024写时序将数据存入IS63LV1024。

4 结语

本系统主要完成了LED显示屏底层的扫描和驱动系统设计,如果使其产品化可形成一套完整的显示屏系统。因其有低成本优势和高性能在市场一定会有竞争力,同时也可满足人民生活的高要求。

图2 单片机软件流程图