摘要:针对低压配电网谐波污染问题,提出了一种具有滤波功能的磁集成式10kV箱式变电站。并且为解决空心电抗器和铁心电抗器的不足之处,设计了一种适用于箱式变电站的滤波电抗器,其集成于配电变压器之中,由匝数相等的两段线圈反向串联连接而成,具有线性度好、体积小以及噪声低等优点。首先介绍了具有滤波功能的10kV箱式变电站的详细方案设计;其次分析了滤波电抗器与变压器绕组之间以及不同滤波电抗器之间的退耦技术;另外推理证明了滤波电抗器具有漏电感特性;最后对一台300kV·A的试验样机进行测试,测试结果表明集成式滤波电抗器具有良好的线性度以及低耦合度,验证了新型10kV箱式变电站良好的滤波效果。

关键词:箱式变电站 滤波 集成化 电抗器

0 引言

近年来,在居民负荷中,变频空调、计算机和电子照明器等非线性负荷不断增加,低压配电网中电流、电压畸变增加,谐波污染现象越来越严重[1-3]。文献[4-6]对一些居民配电网的电能质量进行了现场实时测量,测量结果表明0.4kV侧谐波电流基本为3次、5次和7次等谐波,谐波电流含有量基本都在5%~30%之间,个别量测点达到50%,中性线的谐波含量均在80%以上,个别量测点高达200%。配网中的谐波危害主要体现在以下几个方面:①导致配网的线损增加,电能的传输和利用效率降低;②加剧配电变压器等电气设备的噪声与发热等问题,加速电气设备的绝缘老化,缩短使用寿命;③谐波易产生系统局部串并联谐振,引起谐波的放大现象,导致严重故障;④干扰通信系统的工作,影响继电保护和自动装置的可靠性[7-9]。

10kV箱式变电站是一种把高压开关设备、配电变压器、低压开关设备、电能计量设备和无功补偿装置等按一定的接线方案组合在一个或几个箱体内的紧凑型成套配电装置[10,11]。其广泛应用于城市居民配电网中。面对配电网谐波污染越来越严重的问题,将10kV箱式变电站中的补偿电容器改为LC滤波器是非常有必要的,从而实现对低压配网中特征次谐波治理,并对基波进行无功补偿。但是目前LC滤波器中的电抗器的选择是工程性难题。空心电抗器线性度好,但是其体积庞大,且磁场发散,对它附近的设备会产生附加漏磁损耗。另外不同电抗器需要垂直或错位布置以避免相互之间的磁场干扰,可见空心电抗器不可能适用于紧凑型箱式变电站中[12-14]。铁心电抗器体积小,但其具有噪声和振动严重、线性度差及易饱和等不足之处,也不适用于紧凑型箱式变电站中[15-18]。

本文提出了一种具有滤波功能的磁集成式10kV箱式变电站,其核心关键设计为实现滤波电抗器与配电变压器的集成一体化。集成式滤波电抗器是利用变压器的漏磁场形成电感,这既不同于空心电抗器,也不同于铁心电抗器,具有线性度好、体积小和噪声低等优点。并且滤波电抗器采用特殊的绕组排布方式,用来消除滤波电抗器与变压器绕组之间以及不同滤波电抗器之间的耦合关系。本文首先给出了系统的详细方案设计,其次分析了本方案所运用的退耦技术,另外推理证明了滤波电抗器具有漏电感特性,最后进行实验样机测试,测试结果表明磁集成式滤波电抗器具有良好的线性度以及解耦性,验证了本文提出的这种新型10kV箱式变电站良好的滤波效果。

1 接线方案

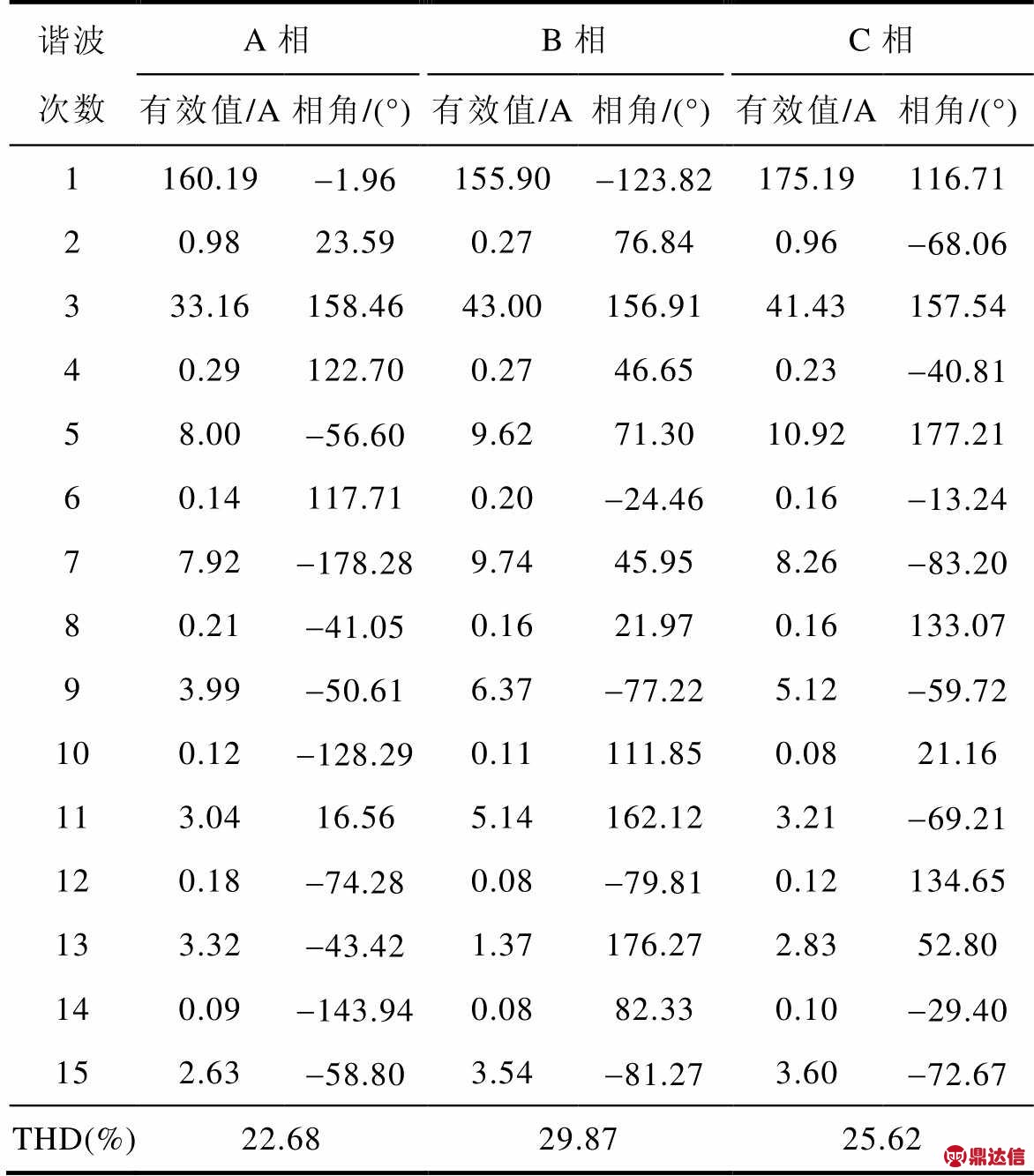

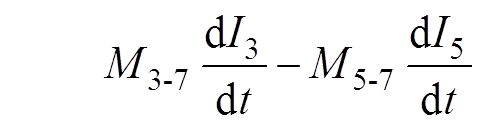

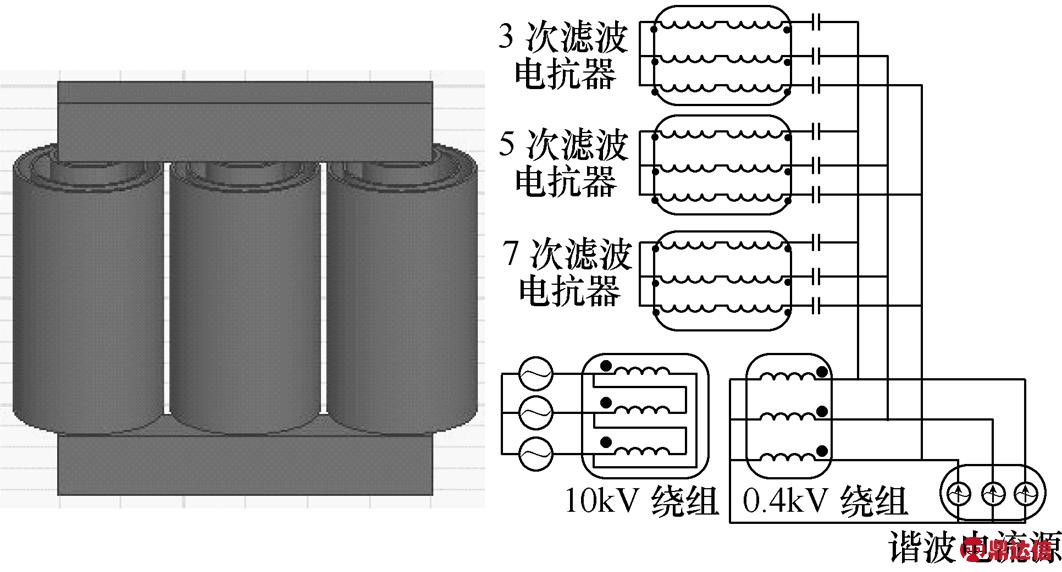

图1 具有滤波功能的磁集成式10kV箱式

变电站的拓扑结构

Fig.1 Topology of a magnetic-integrated 10kV prefabricated substation with function of filtering

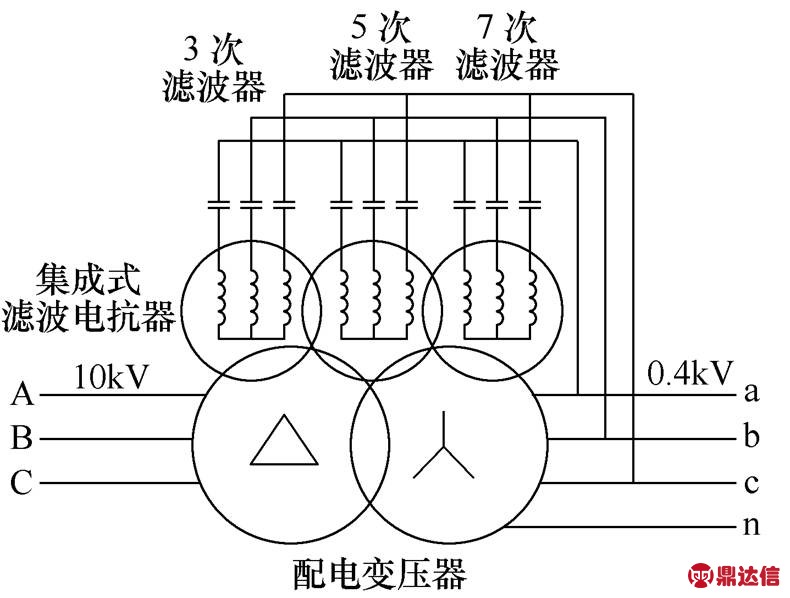

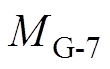

图2 集成滤波电抗器式配电变压器的绕组布置

Fig.2 Winding arrangement of distribution transformer with integrated filtering reactors

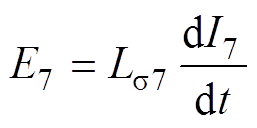

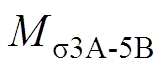

具有滤波功能的磁集成式10kV箱式变电站的主电路拓扑结构如图1所示。配电变压器的0.4kV侧接3次、5次和7次三组LC滤波器,滤除0.4kV侧主要的3次、5次和7次谐波,并对基波实现无功补偿。滤波电抗器集成于配电变压器之中。集成滤波电抗器的配电变压器具体的绕组布置如图2所示,由铁心往外依次为三组滤波电抗器绕组、低压绕组和高压绕组。每个滤波电抗器的绕组由匝数相等的两段线圈反向串联连接。滤波电抗器是利用变压器的漏磁场形成电感,具有线性度好、体积小以及噪声低等优点。滤波电抗器与变压器绕组之间以及不同滤波电抗器之间基本实现了解耦,所采用退耦技术在下文中第2节中进行具体分析。需要说明的是:

(1)滤波电抗器的绕组由匝数相等的两段线圈反向串联连接,且两段线圈上下布置,一方面是为了实现退耦,另一方面是为了获得较大电感值。

(2)可将单个滤波电抗器的两个反向串联的线圈看成是一台交错式绕组变压器的一次、二次绕组,按照交错式绕组计算的短路阻抗即为滤波电抗器的阻抗值[19]。

(3)高低压绕组短路阻抗的计算和普通双绕组变压器的短路阻抗计算相同。

(4)众所周知,配电系统中低压侧3次谐波主要为零序分量。但是由于低压侧负载的不对称特性,3次谐波仍然含有少量的正序分量和负序分量。高压侧绕组三角形联结已经隔离了主要含量的3次谐波零序分量,使高压侧只含有少量的3次谐波非零序分量。但是低压侧仍然需要配置3次滤波器,这是因为若无3次滤波器,5次、7次滤波器会导致3次谐波非零序分量的放大现象,影响高压侧谐波的治理效果。

(5)配电变压器与滤波电抗器集成一体化,使得变压器绕组较多,在一定程度上增大了变压器线圈的体积,提高了线圈之间的绝缘要求,使变压器的设计会相对比较复杂。但是由于滤波电抗器基本实现了与变压器高低压绕组的解耦,滤波电抗器的集成对变压器的运行及性能并没有明显的影响。

(6)对于滤波电抗器及滤波电容值的计算,应先根据变电站所需无功补偿总容量(一般按配变容量的20%~40%进行配置),确定所补偿的总电容值。然后根据总电容值,按照大约 的比例分配3次、5次和7次滤波器的电容值,再由3次、5次和7次滤波器的电容值按照谐波阻抗为零的原则分别计算各个滤波器电抗值,这样计算出来的各个滤波器电抗值基本相等,便于集成滤波电抗器的设计。

的比例分配3次、5次和7次滤波器的电容值,再由3次、5次和7次滤波器的电容值按照谐波阻抗为零的原则分别计算各个滤波器电抗值,这样计算出来的各个滤波器电抗值基本相等,便于集成滤波电抗器的设计。

2 退耦技术

图2中一个铁心上绕有两个变压器绕组和三组滤波电抗器,为保证良好的滤波效果,消除实现它们之间的耦合关系是关键,为此本文中采用了以下几种退耦技术。

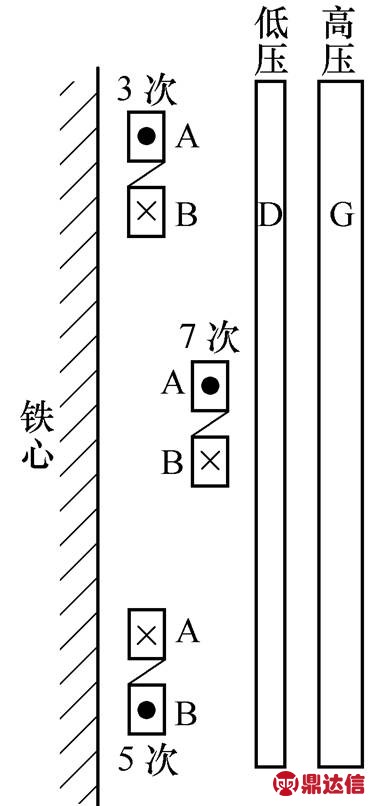

2.1 主磁通交链滤波电抗器两个线圈的磁链相抵消的退耦技术

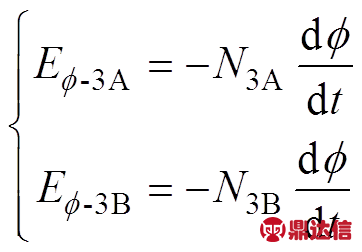

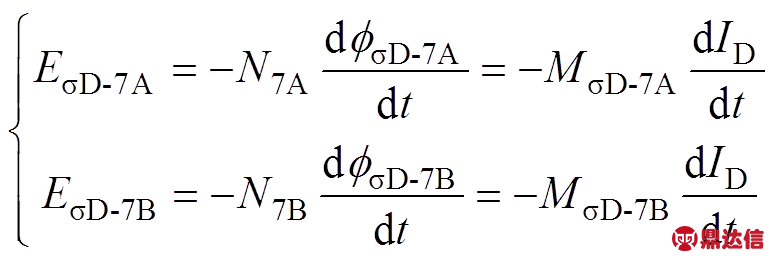

以3次滤波电抗器为例进行解释说明。主磁通在3次滤波电抗器A、B两个线圈中感应电动势可以表示为

(1)

(1)式中, 、

、 分别为A、B两个线圈的匝数;

分别为A、B两个线圈的匝数; 为铁心主磁通。

为铁心主磁通。

由于A、B两个线圈为反向串联,所以主磁通在3次滤波电抗器的总感应电动势为

(2)

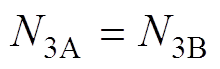

(2)又由于A、B两个线圈的匝数相等,即

(3)

(3)综合式(1)~式(3),可得

(4)

(4)综上所述可以看出,由于将每个滤波电抗器分成匝数相等的两个线圈,并将两个线圈反向串联连接。所以,两个线圈的主磁链大小相等、方向相反,他们之间相互抵消,每个滤波电抗器的总的主磁链为零。这就是主磁通交链滤波电抗器两个线圈的磁链相抵消的退耦技术,主磁通在滤波电抗器的总感应电动势为零。

2.2 变压器绕组漏磁交链滤波电抗器两个线圈的漏磁链数相近的退耦技术

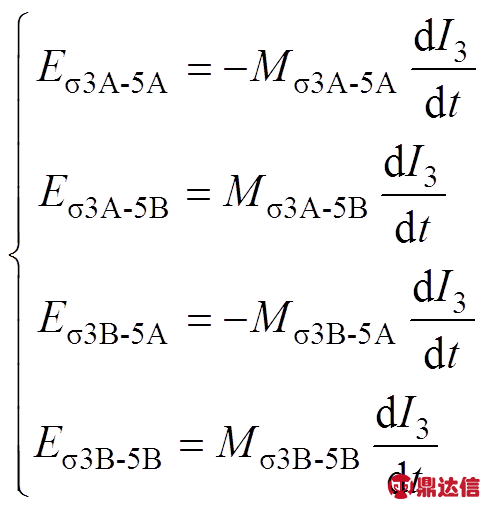

以7次滤波电抗器和低压绕组之间的漏磁链退耦为例进行解释说明。低压绕组通过漏磁链对7次滤波电抗器A、B线圈的感应电动势可以表示为

(5)

(5)式中, 、

、 分别为低压绕组在A、B两个线圈中产生的漏磁通;

分别为低压绕组在A、B两个线圈中产生的漏磁通; 、

、 分别为低压绕组与A、B两个线圈的漏互感;

分别为低压绕组与A、B两个线圈的漏互感; 为低压绕组的电流。

为低压绕组的电流。

低压绕组通过漏磁在7次滤波电抗器总感应电动势为

(6)

(6)又由于7次滤波电抗器的A、B两个线圈基本以低压绕组的中心对称布置,所以低压绕组与A、B两个线圈的漏互感基本相等,即

(7)

(7)综合式(5)~式(7),可得

(8)

(8)综上所述,变压器绕组产生的漏磁场将与滤波电抗器相交链,为了确保变压器绕组在滤波电抗器中产生的漏感感应电动势为零或者很小,必须保证变压器绕组漏磁交链电抗器两段线圈的漏磁链数相近,即绕组与两个线圈的漏互感基本相等。要实现上述目标,至少要保证3次滤波电抗器绕组上高度不超过变压器绕组的上高度,5次滤波电抗器绕组下高度不低于变压器绕组的下高度,7次滤波电抗器尽可能地以绕组中心对称布置。

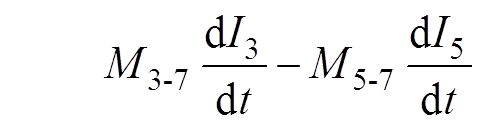

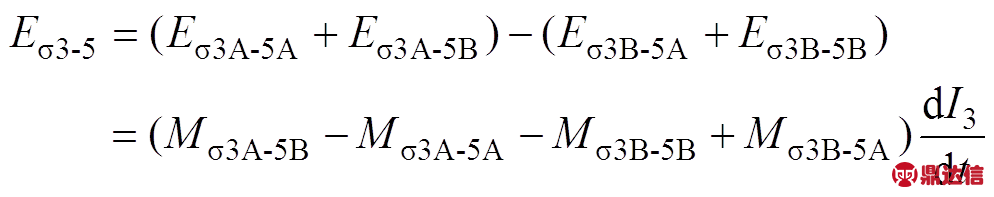

2.3 减小滤波电抗器之间漏磁交链的退耦技术

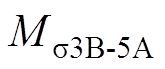

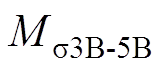

以3次滤波电抗器和5次滤波电抗器漏磁链退耦为例进行解释说明。3次滤波电抗器通过漏磁链对5次滤波电抗器感应电动势为

(9)

(9)式中, 、

、 、

、 和

和 分别为3次滤波电抗器两个线圈与5次滤波电抗器两个线圈的漏互感;

分别为3次滤波电抗器两个线圈与5次滤波电抗器两个线圈的漏互感; 为3次滤波电抗器的电流。则3次滤波电抗器通过漏磁在5次滤波电抗器中总感应电动势为

为3次滤波电抗器的电流。则3次滤波电抗器通过漏磁在5次滤波电抗器中总感应电动势为

(10)

(10)当3次滤波电抗器和5次滤波电抗器保持一定距离时,等式(11)成立。

(11)

(11)综合式(10)和式(11),可得

(12)

(12)综上所述,变压器铁心柱上集成了三个滤波电抗器,且由于漏磁场的非均匀性,既使电抗器实施了反串连接,也无法使得两反串电抗器绕组总漏感感应电动势为零,三个电抗器的漏磁耦合都将存在,因而应让三个电抗器在空间上保持适当距离,使三个电抗器的之间的交链漏磁基本为零。

变压器中绕组之间的耦合主要是通过主磁通进行耦合,漏磁通只有较小的耦合关系。由上面的分析可以看出,通过上文中的2.1节退耦技术,完全消除了绕组和滤波电抗器之间以及不同滤波电抗器之间主要的通过主磁链进行的耦合。另外,2.2节和2.3节退耦技术对于通过漏磁链的耦合也使其大大地减弱。整体装置中绕组和滤波电抗器之间以及不同滤波电抗器之间基本实现了完全解耦。

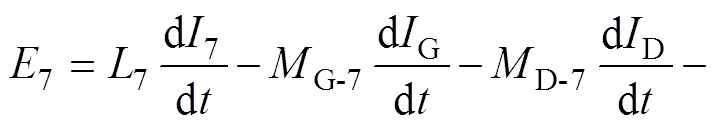

3 滤波电抗器漏电感特性分析

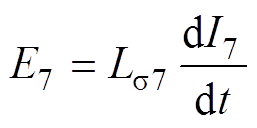

以7次滤波电抗器为例来分析滤波电抗器的电感特性,7次滤波电抗器的总感应电动势(包含通过主、漏磁通所感应的所有电动势)为

(13)

(13)式中, 为7次滤波电抗器的自感;

为7次滤波电抗器的自感; 、

、 、

、 和

和 分别为高压绕组、低压绕组、3次滤波电抗器和5次滤波电抗器与7次滤波电抗器之间的互感;

分别为高压绕组、低压绕组、3次滤波电抗器和5次滤波电抗器与7次滤波电抗器之间的互感; 、

、 、

、 、

、 和

和 分别为7次滤波电抗器、高压绕组、低压绕组、3次滤波电抗器和5次滤波电抗器的电流。

分别为7次滤波电抗器、高压绕组、低压绕组、3次滤波电抗器和5次滤波电抗器的电流。

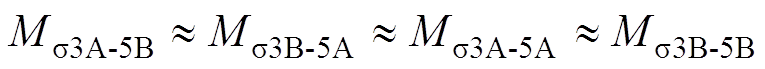

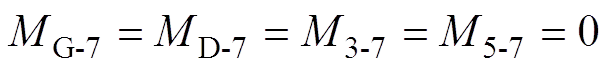

通过第2节中的三种退耦技术,保证了变压器绕组和其他滤波电抗器对7次滤波电抗器的互感(包括主互感和漏互感)基本为零,即

(14)

(14)由式(13)和式(14)可得

(15)

(15)式中, 、

、 分别为主自感和漏自感。

分别为主自感和漏自感。

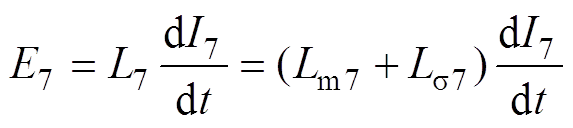

由主磁通交链滤波电抗器两个线圈的磁链相抵消的退耦技术可知,7次滤波电抗器的主自感为零,即

(16)

(16)则式(15)可以简化为

(17)

(17)可见,滤波电抗器不但实现了解耦,消除了变压器绕组及其他滤波电抗器对其的影响。而且是利用变压器的漏磁场形成电感,仅仅具有漏自感的特征,具有很好的线性度。

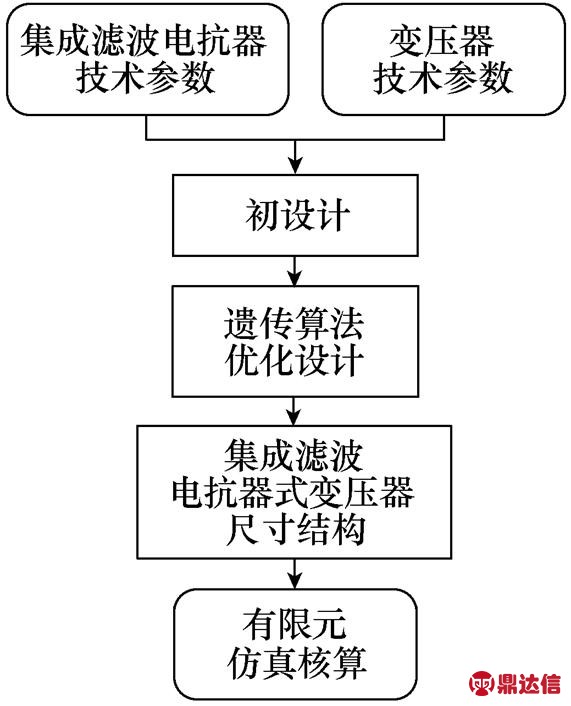

4 变压器设计流程

变压器设计的基本流程如图3所示,首先根据变压器绕组的短路阻抗、容量、电压等级和滤波电抗器电感等主要技术参数,对变压器进行初设计;其次,利用一组较为符合设计目标的初设计结构参数,以绕组结构尺寸等参数为寻优变量,以体积最小和成本最低为目标函数,以滤波电抗器电感、滤波电抗器与变压器绕组以及滤波电抗器之间的耦合度、变压器损耗与温升、变压器阻抗参数等为约束条件,或增加部分惩罚函数,通过遗传算法求得最优解;最后,根据集成滤波电抗器式变压器的最优尺寸结构,在Ansoft/Maxwell电磁场仿真软件中建立有限元仿真模型,对滤波电抗器电感值、耦合度等进行仿真核算。

图3 变压器设计的基本流程

Fig.3 The basic flow chart of transformer design

5 试验测试

本文设计制造了一台300kV·A具有滤波功能的磁集成式10kV箱式变电站试验样机,其实物如图4所示。变压器集成了三个滤波电抗器,其绕组布置和图2相同。

5.1 电感测试

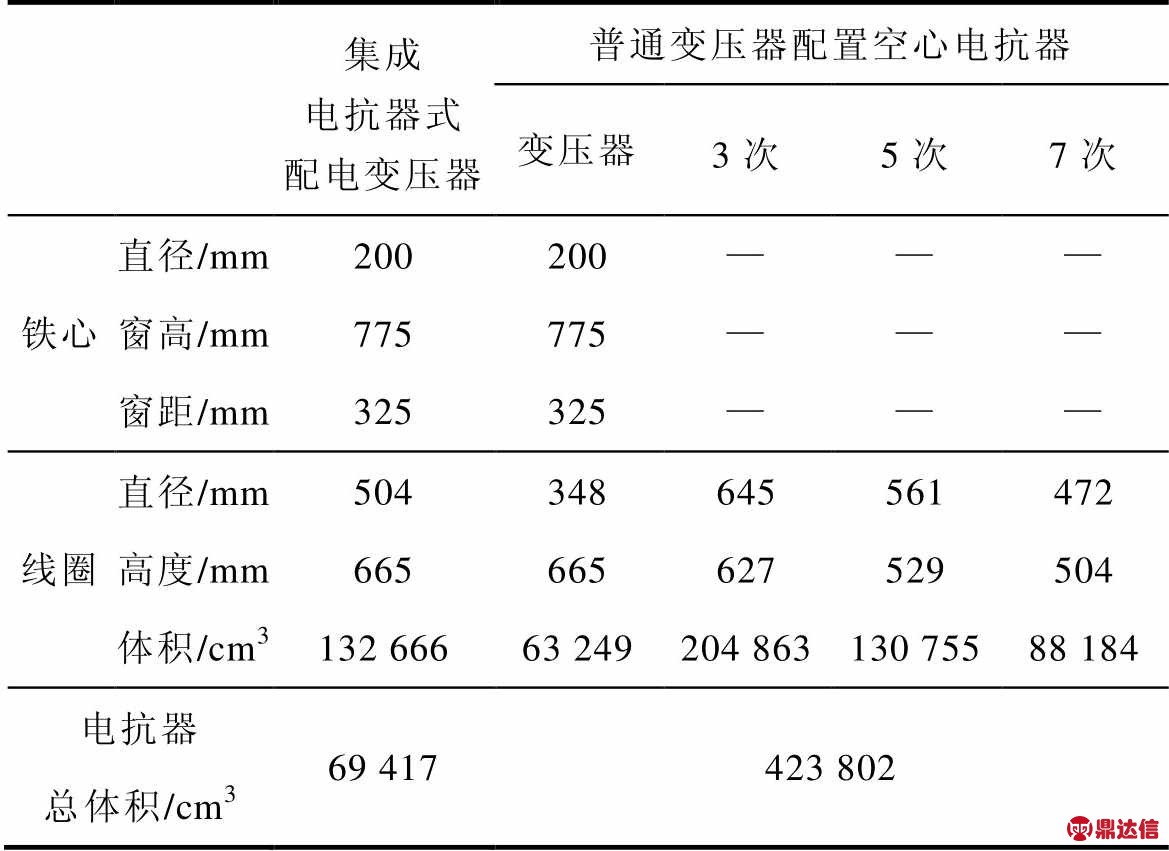

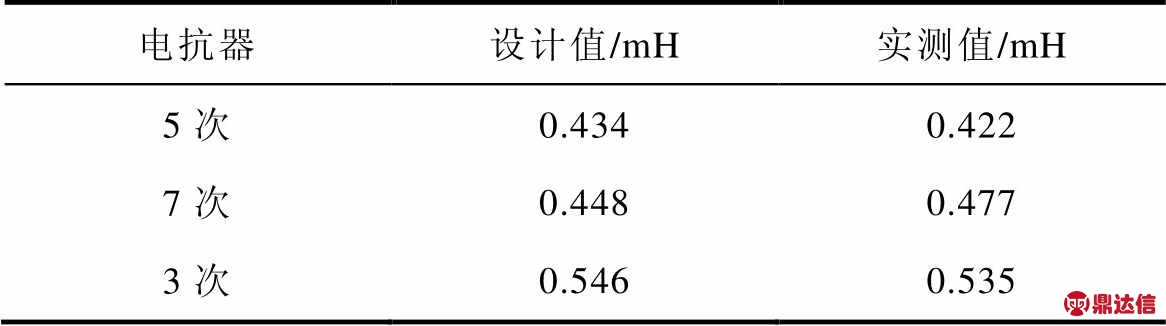

三个滤波电抗器电感的设计值与实测值见表1,可见设计值和实测值误差在5%之内,证明了本文电抗器设计方法与计算方法的正确性。

图4 试验样机实物

Fig.4 Photo of the experimental prototype

表1 滤波电抗器电感

Tab.1 Inductance value of filtering reactors

分别对三个滤波电抗器加电压,使它们电流由零到额定电流逐渐增加,实测出不同电流时刻的电感值,如图5所示。由图可以看出,不同电流下滤波电抗器的实测电感值基本不变,表明滤波电抗器呈现了良好的线性度。

图5 滤波电抗器电感测试曲线

Fig.5 The experimental curves of inductance value of filtering reactors

5.2 退耦测试

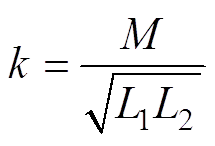

两个绕组之间的耦合度的计算公式为

(18)

(18)式中, 、

、 分别为两个绕组的自感;

分别为两个绕组的自感; 为两个绕组的互感。

为两个绕组的互感。

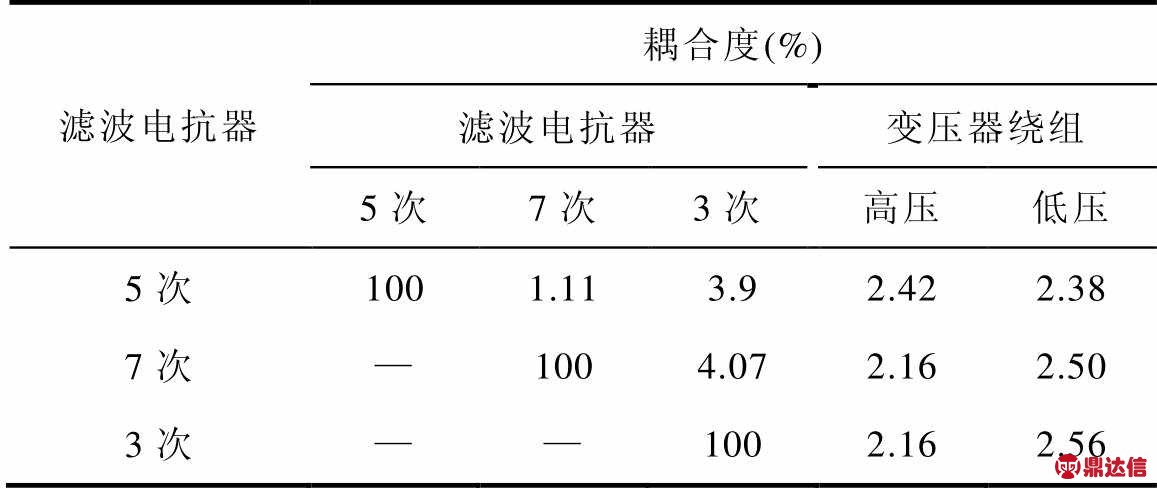

对每个绕组的自感及两两绕组的互感进行试验测试,并利用式(18)进行耦合度计算,耦合度实测结果见表2。由表2可以看出滤波电抗器与变压器绕组以及滤波电抗器之间的耦合度都小于5%,基本实现完全解耦,达到了工程应用的要求。

表2 耦合度实测结果

Tab.2 Experimental coupling degrees

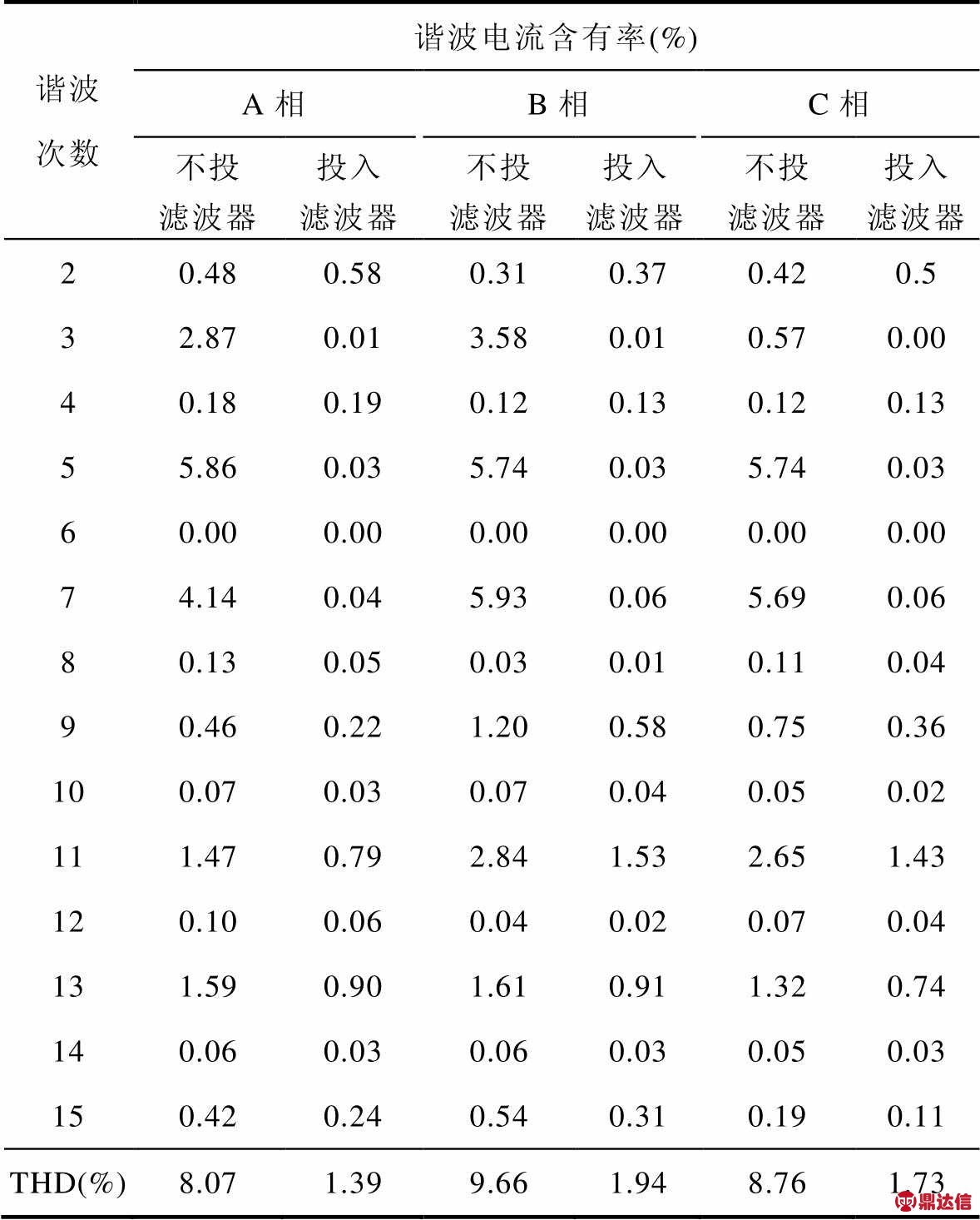

5.3 滤波效果分析

5.3.1 工程应用仿真分析

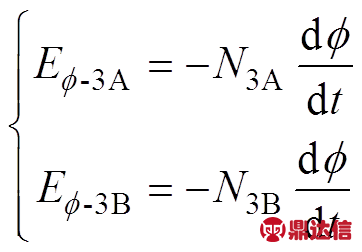

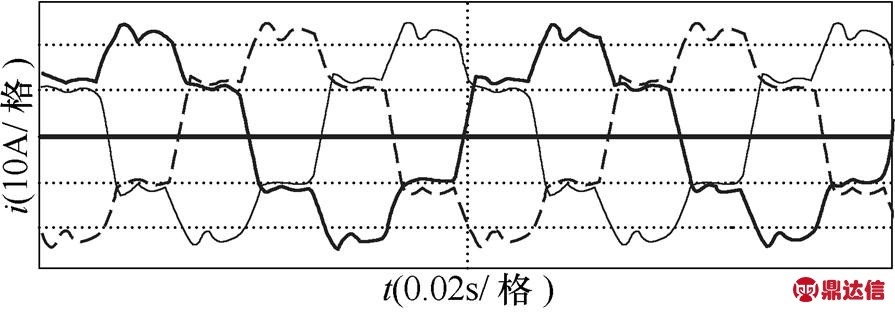

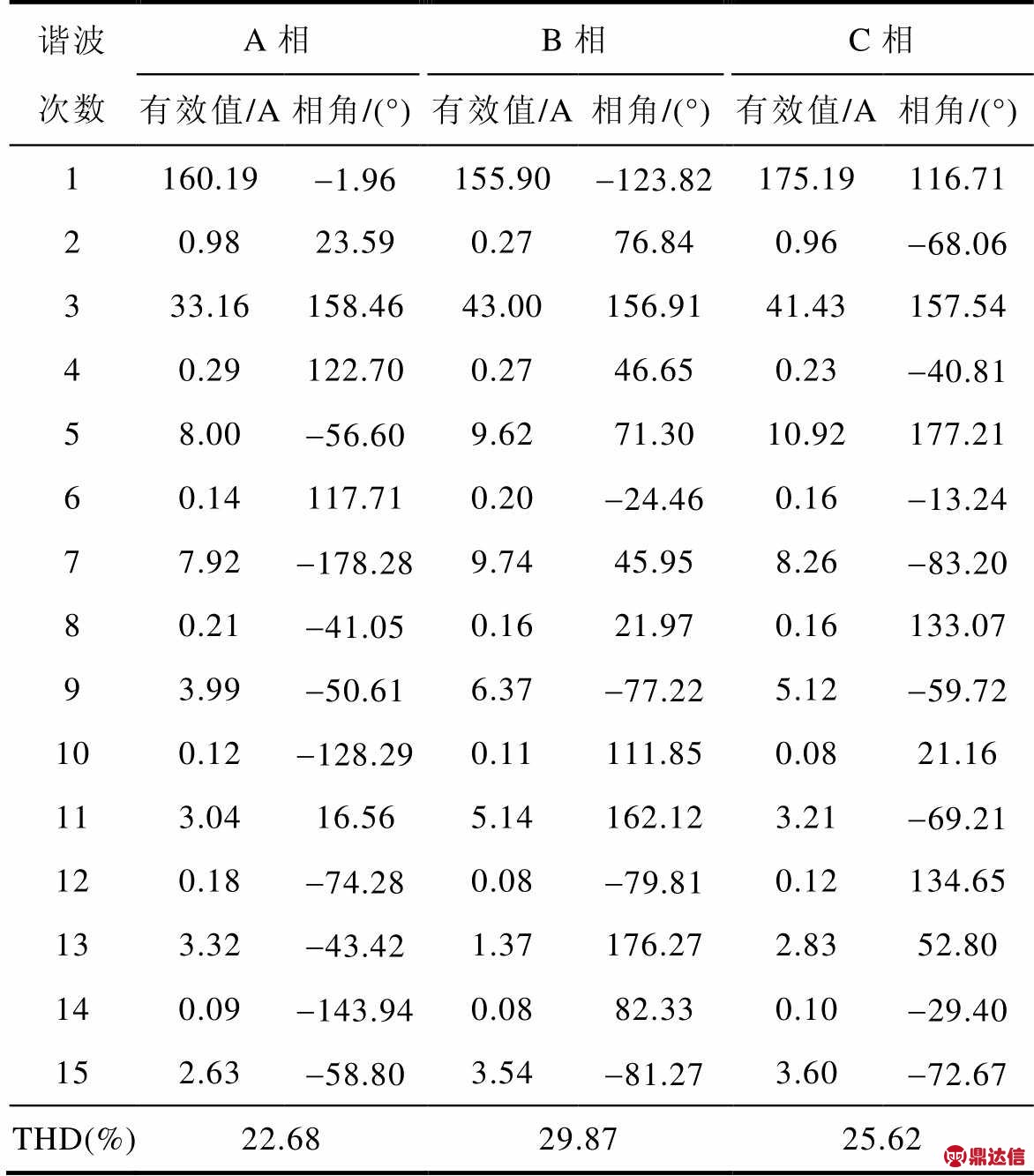

根据试验样机中变压器(包含滤波电抗器)的实际尺寸,在Ansoft/Maxwell电磁场软件中建立了有限元仿真模型,如图6a所示。图6b为磁集成式10kV箱式变电站的场路耦合仿真电路。0.4kV负载侧的基波及谐波电流数据为某一实际工程应用的配电变压器低压侧的实测电流,其波形如附图1所示,其具体谐波电流数据见附表1,其三相电流的不平衡度为11.78%。通过场路耦合仿真,得到10kV侧电流仿真波形如图7所示,具体谐波电流含量见表3。由仿真结果可以看出,集成式滤波方案具有良好的滤波效果,证明了集成式滤波方案在实际配电系统中应用的有效性。

(a)变压器有限元模型 (b)场路耦合电路

图6 仿真模型Fig.6 The simulation model

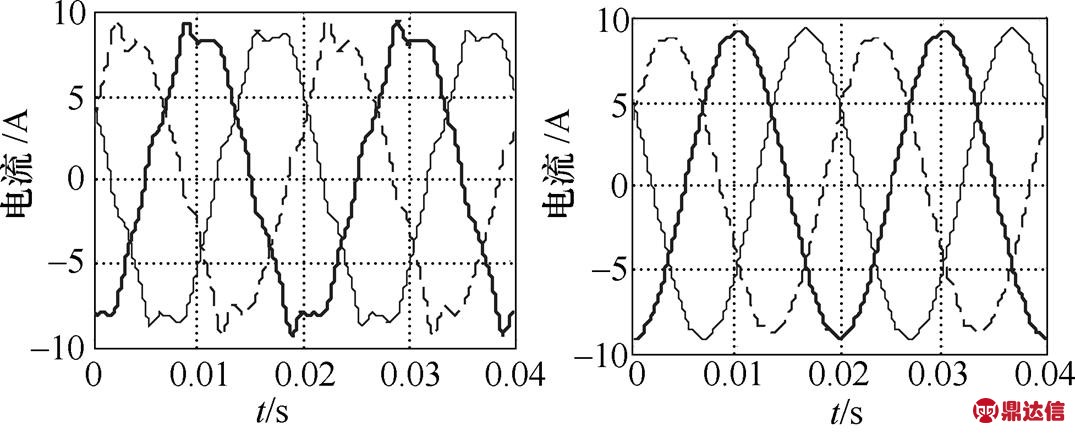

(a)不投滤波器 (b)投入滤波器

图7 10kV侧电流仿真波形Fig.7 Simulation current waveforms in 10kV side

表3 10kV侧谐波电流仿真数据

Tab.3 Simulation harmonic current data in 10kV side

5.3.2 试验测试

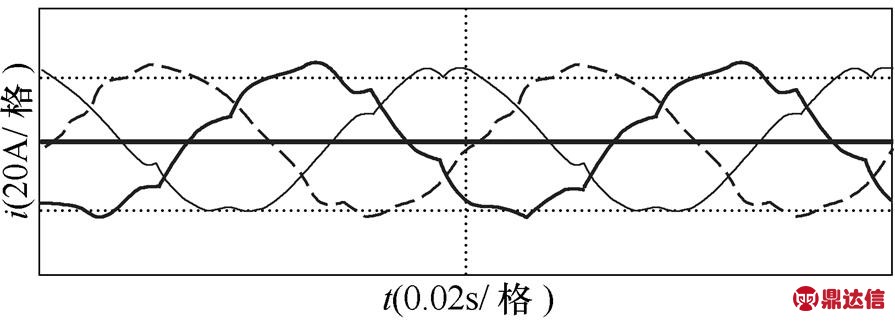

在滤波效果试验测试中,通过低压绕组接一个三相桥式整流负载来基本等效低压配网中的谐波,主要包含5次、7次、11次等谐波,虽然没有3次谐波,但是并不影响本处对集成式滤波性能的验证。本处三个电抗器分别与三个电容器构成5次、7次和11次滤波器,用来消除三相整流负载产生的5次、7次和11次谐波。10kV侧电流测试波形如图8所示,具体的谐波电流含有率见表4。由表4可以看出投入滤波器后,10kV侧的谐波电流大大降低,谐波总畸变率由24.51%降低为4.37%,试验测试验证了本文集成式滤波方案的有效性。

(a)不投滤波器

(b)投入滤波器

图8 10kV侧电流测试波形Fig.8 Experimental current waveforms in 10kV side

表4 10kV侧谐波电流实测数据

Tab.4 Experimental harmonic current data in 10kV side

5.4 噪声与体积测试

利用噪声检测设备对箱式变电站进行噪声测试。空载时,体箱内噪声为50dB,体箱外噪声为42dB;额定负载投入所有滤波支路时,体箱内部噪声为56dB,体箱外噪声为47dB,所有噪声均低于国家标准规定的60dB。

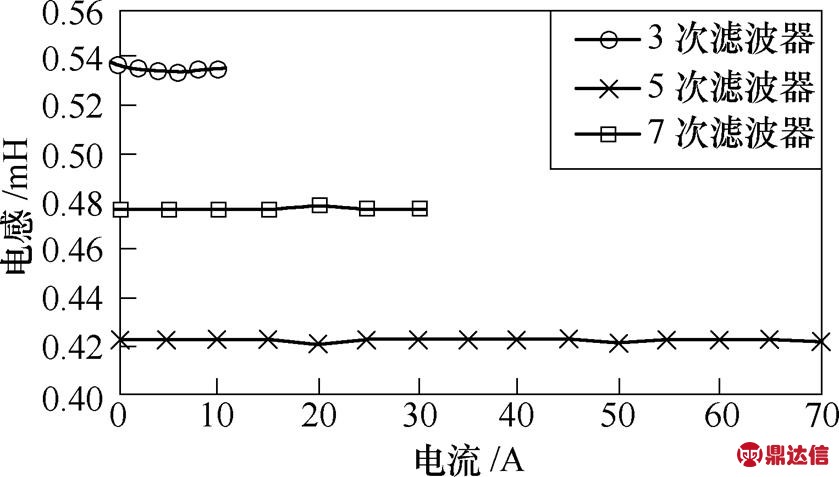

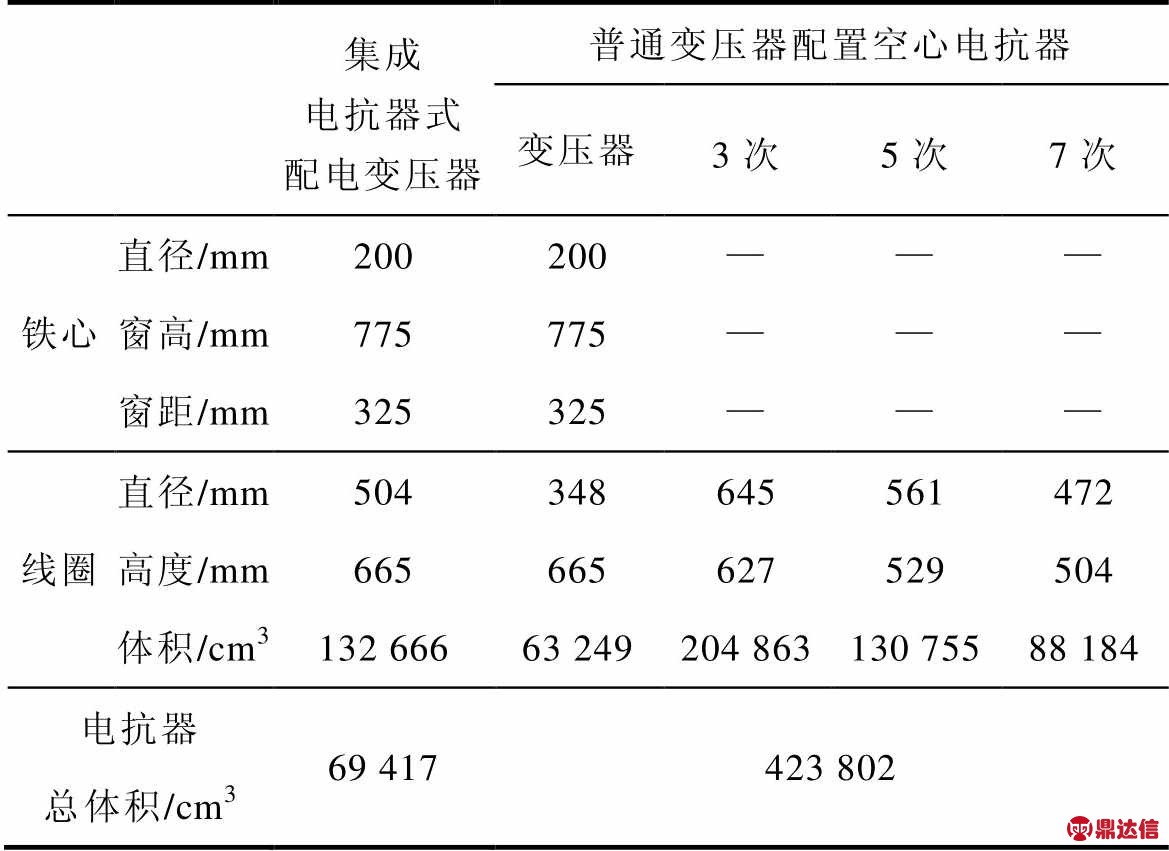

集成滤波电抗器式配电变压器与普通变压器及空心电抗器的基本尺寸对比数据见表5。由于集成滤波电抗器实现了对主磁通的完全解耦,其流过的电流不会对主磁通产生影响,所以集成滤波电抗器式变压器的铁心结构及尺寸的设计与普通配电变压器基本相同。由表5可以看出,与普通变压器相比,集成滤波电抗器式变压器线圈的体积(即图2中高压绕组的体积)有所增加,其增加的体积为滤波电抗器的体积,但是与采用三个空心电抗器相比,集成式滤波电抗器的总体积大约是空心电抗器总体积的1/6。并且,为避免磁场干扰,空心电抗器需要垂直或错位布置,这还会增加额外的布置空间,可见集成式滤波电抗器具有明显的减小体积的优势。

表5 设备尺寸及体积数据

Tab.5 Size and volume data of equipments

6 结论

针对低压配电网中谐波污染问题,本文提出了一种具有滤波功能的磁集成式10kV箱式变电站,将滤波电抗器与配电变压器集成于一体,具有线性度好、体积小和噪声低等优点。本方案采用了三种退耦技术,基本消除了滤波电抗器与变压器绕组之间以及不同滤波电抗器之间的耦合,实现了滤波电抗器的漏电感特征。对一台300kV·A的试验样机进行相关测试,试验表明磁集成式滤波电抗器具有良好的线性度以及低耦合度,验证了本文提出的这种新型10kV箱式变电站良好的滤波效果。本文的研究为具有滤波功能的磁集成式10kV箱式变电站的工程应用打下了坚实的基础,并且文中所涉及的磁集成式电抗器在对电抗器的体积、噪声等有严格要求的系统(比如舰艇推进系统)中都有重要的应用价值。

附表1 某一实际配电变压器低压侧实测

电流具体谐波数据

App.Tab. Experimertal harmonic current data in the low voltage side of a distribution transformer