摘要:针对空间应用的高速串行接口芯片易受单粒子辐照而出现误码的问题,提出了一种面向空间辐照环境的星载高速数字接口芯片设计方法。首先,针对空间辐照诱发单比特错误导致高速串行接口传输出错问题,计算辐照时的高速串行接口误码率最劣值;然后,通过误码率最劣值计算出辐照环境下高速串行接口无误码传输所需的增益;最后,采用叠加编码增益及辐照干扰的高速串行接口链路评价模型,计算出高速串行接口物理编码子层(PCS)中不同编码方式的编码增益,并评估编码增益对辐照降低高速串行接口误码率的补偿效果,根据补偿效果选择RS-8B/10B级联编码作为PCS编码。采用该高速数字接口芯片设计方法设计了一款速率为3.125 Gb/s的抗辐照高速串行接口芯片,其面积为4.84 mm2,典型功耗为207 mW。单粒子辐照试验结果表明,对比传统设计方法,新的设计方法将芯片的单比特错误阈值提升了9 MeV·cm2/mg。

关键词:单粒子辐照;抗辐照加固;高速串行接口;RS编码;8B/10B编码

高速串行接口通常也称为SerDes接口,已逐步取代传统并行接口而成为当前数字传输的主流接口技术[1-2]。在空间应用中,SerDes接口由于体积小的优势,已成为星载计算机和通信设备间重要接口[3-4]。然而,由于SerDes接口传输速度快,外层空间电离辐照在接口芯片内部产生的单粒子翻转(SEU)或单粒子瞬态(SET)效应很容易引起接口芯片的物理编码子层(PCS)模块及物理介质接入子层(PMA)模块出错,从而出现显著的误码,因此为了保证可靠性,星载设备必须采用经过抗辐照加固的高速接口芯片[5-7]。

在判断辐照加固成效方面,高速SerDes接口等新一代的抗辐照高速元器件在轨翻转主要采用绘制饱和翻转截面值的方法,拟合出器件的在轨翻转率。在轨翻转率可以评价器件在轨道空间中的翻转发生概率,但无法直接评价电路在空间中无错误传输的安全阈值。采用在轨翻转率曲线上首次发生传输错误事件的入射粒子能量作为辐照的单比特错误阈值(On SET),用来评价接口类电路能够保证的无错误传输的粒子线性能量转移(LET)阈值能量大小[8-9]。

经典的低速数字接口芯片采用全局三模冗余(GTMR)及增大节点电容的设计加固方法牺牲了电路的工作速率[10-11],因此不适合用于高速SerDes接口的设计加固。主要的SerDes加固方式包括工艺加固及编码部分三模冗余(TMR)设计加固,或者二者结合方法。文献[12]中的SerDes接口采用抗辐照加固的绝缘体上硅(SOI)工艺进行设计,其出现单比特错误的LET阈值约为2 MeV·cm2/mg,连续错误比特致复位的辐照阈值约为20 MeV·cm2/mg,单位器件饱和翻转截面值约10-5 cm2。文献[13]中的SerDes芯片采用抗辐照加固的体硅CMOS工艺,并对数字编码进行TMR设计加固,其单比特错误辐照阈值为1 MeV·cm2/mg,连续性错误辐照阈值为10 MeV·cm2/mg,单位器件饱和翻转截面值约为10-4 cm2。文献[14]中的高速串行接口采用外延工艺结合设计加固,发生发送和接收的单比特错误辐照阈值分别为1 MeV·cm2/mg和2 MeV·cm2/mg,单位器件饱和翻转截面值约为10-4 cm2[15]。前述文献说明,业界采用的高速SerDes的辐照加固方法中,工艺加固法效果明显,TMR加固法对单比特错误辐照阈值的改善成效偏弱。

本文基于SerDes传输的链路评价模型,提出了一种通过辐照时误码率变化计算SerDes以维持正确传输所需增益大小的方法,并通过叠加了编码增益及辐照干扰的链路模型,分析了SerDes的PCS中不同编码方式对辐照导致传输误码的补偿效果,根据补偿效果提出了RS-8B/10B级联编码方案,并将该级连编码应用在一款用0.13 μm SOI CMOS工艺设计的速率为3.125 Gb/s的抗辐照加固SerDes接口芯片中。试验结果表明,该设计加固方法能够显著提升该抗辐照接口芯片的单比特错误LET阈值。

1 SerDes接口芯片的PCS编码增益分析

1.1 典型SerDes接口芯片结构

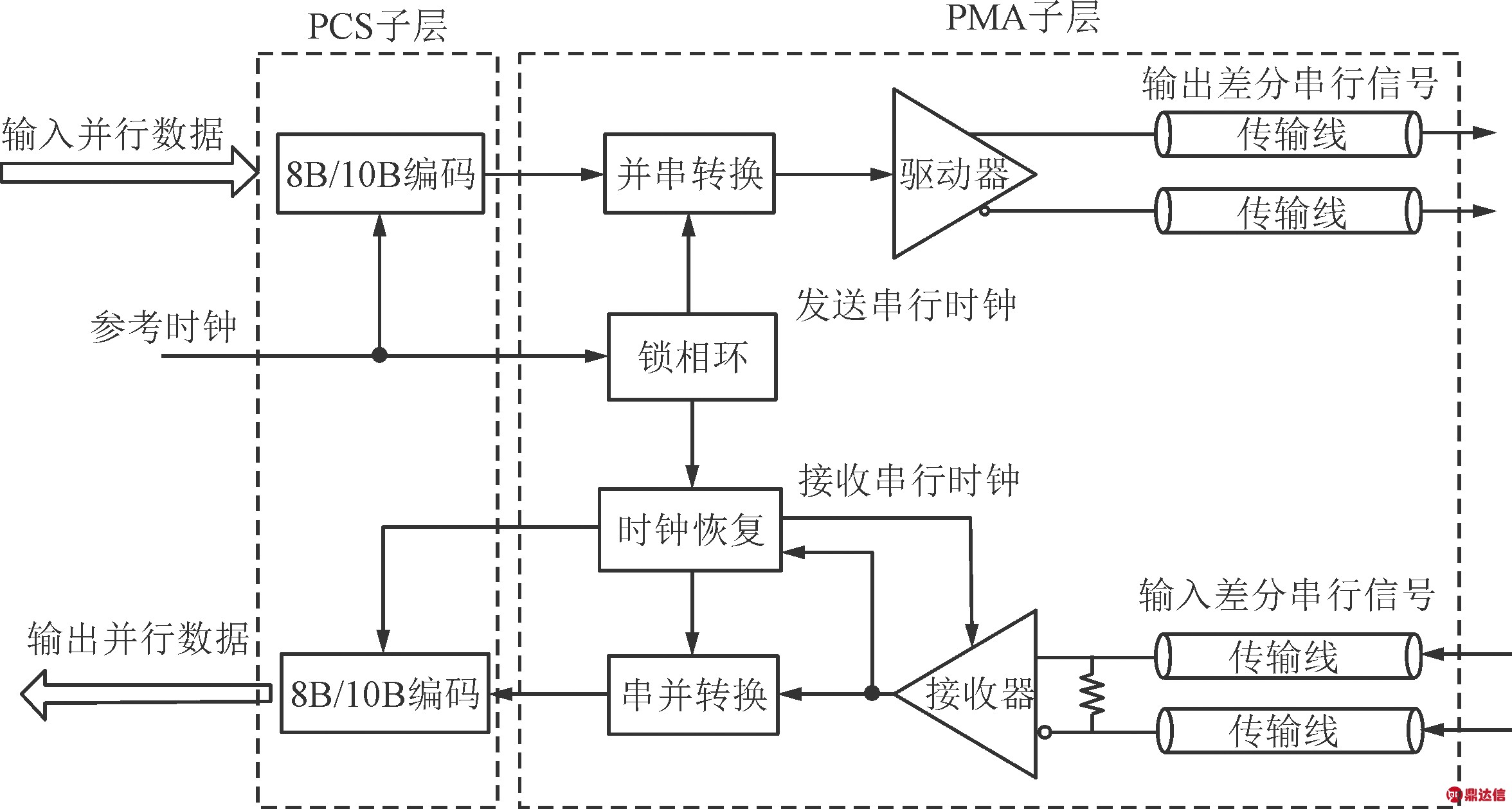

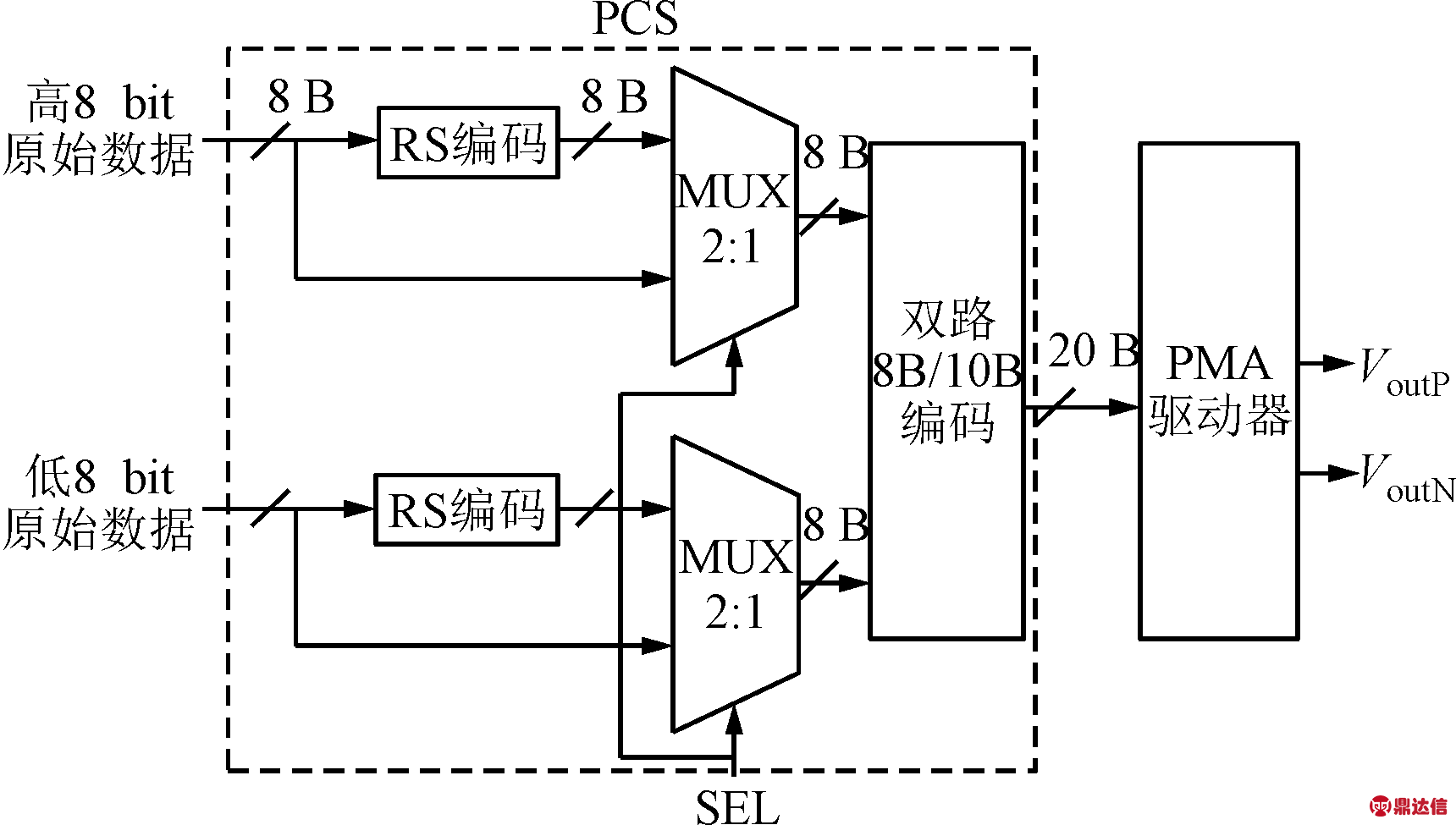

高速SerDes芯片通常由PMA层和PCS层组成,如图1所示。PMA主要实现数据的串行化以及发送或接收功能,具体包括:并行数据的串行化及串行数据的解串化、参考时钟的倍频、时钟数据恢复、串行数据低摆幅差分信号的发送和接收等[16]。

PCS子层主要实现并行数据的编码。传统的PCS编码大多采用了8B/10B编码,即将每8 bit为1组的并行数据按照一定的编码规则映射为10 bit一组的并行数据。8B/10B编码的主要目的是实现编码后数据的直流平衡,避免串行化后的数据出现连续5个以上的“1”或“0”,从而保证SerDes接收端能够有效地实现时钟数据恢复[16]。目前业界主要加固是对PCS编解码进行TMR设计加固,并未考虑改进PCS的编码方法。

图1 典型SerDes接口芯片结构

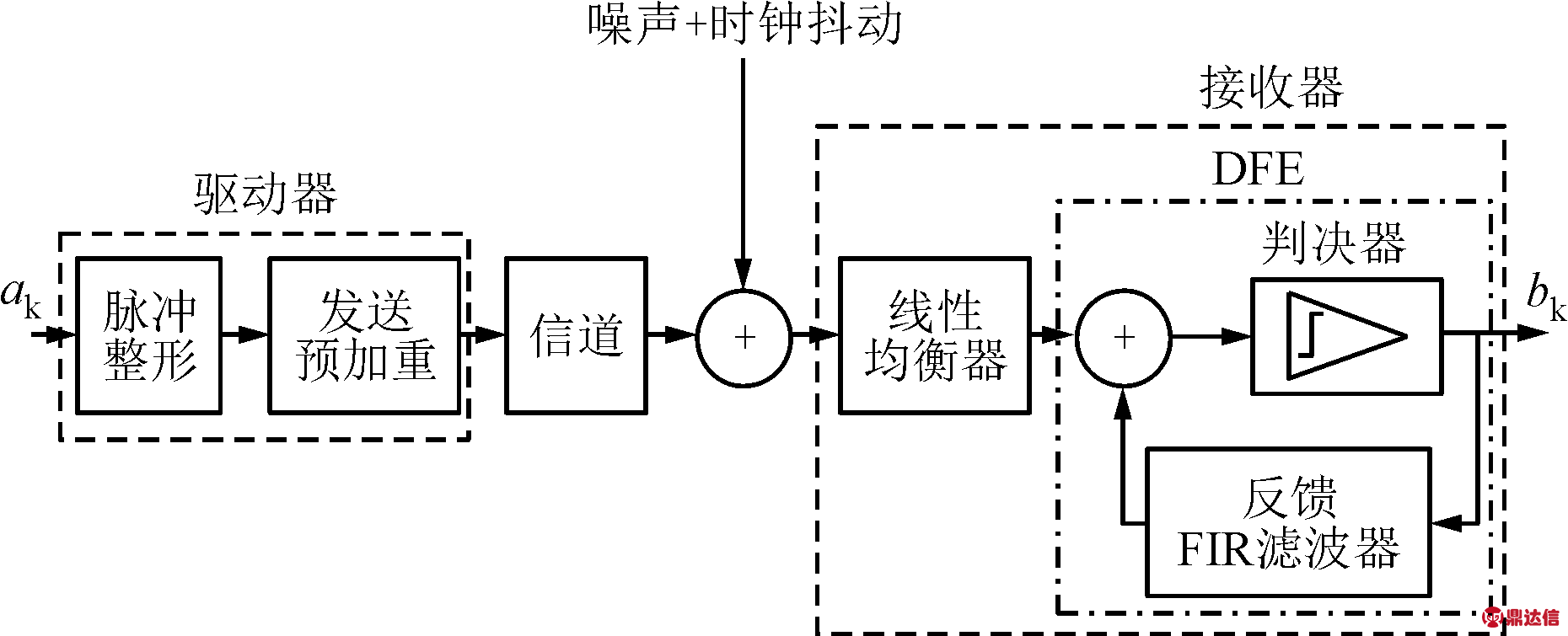

1.2 经典SerDes接口信道评价模型

为了从理论上说明不同的PCS编码方案的抗辐照能力,引入SerDes链路的系统评价模型[17],如图2所示。假定经过PCS处理并完成串行化后的输入信号ak是不相关且均值为0的随机序列,首先经过一个脉冲整形滤波器,再经过一个预加重处理器。预加重也可以看作是一个有限冲激响应(FIR)滤波器。发送器与接收器之间的通信介质通常可用一个低通模型来代表,而发送器和接收器电路的噪声,空间辐照的干扰以及时钟抖动等非理想因素都建模为一个加性噪声。在接收机一侧,信号会经过不同形式的均衡处理,可以是线性均衡、判决反馈均衡(DFE)或是二者的结合,图2采用了线性均衡与DFE相结合的形式。

图2 经典SerDes的链路评价模型[17]

根据文献[17],对图2中的各模块进行线性化建模,可以在行为级对不同的信号处理方式和均衡实现方式进行评估。文献[17]模型中,采用接收器在最佳采样点处获得信号的信噪比RSN来评价链路性能

(1)

式中:dmin为接收器不同输出码值的最小电压差;σ2为接收器输出端的等效噪声功率。不同信号调制方式下,dmin具有不同的值,对于非归零二进制(NRZ)码,dmin=VDD,VDD为电源电压。式(1)所示的RSN可以轻易地映射为SerDes接口接收数据的误码率Pber,表达式如下

(2)

式中:erfc(·)代表互补误差函数。根据式(2)可以轻易得出:对于10-12的误码率,需要在接收器输出端的信噪比为23 dB[17]。

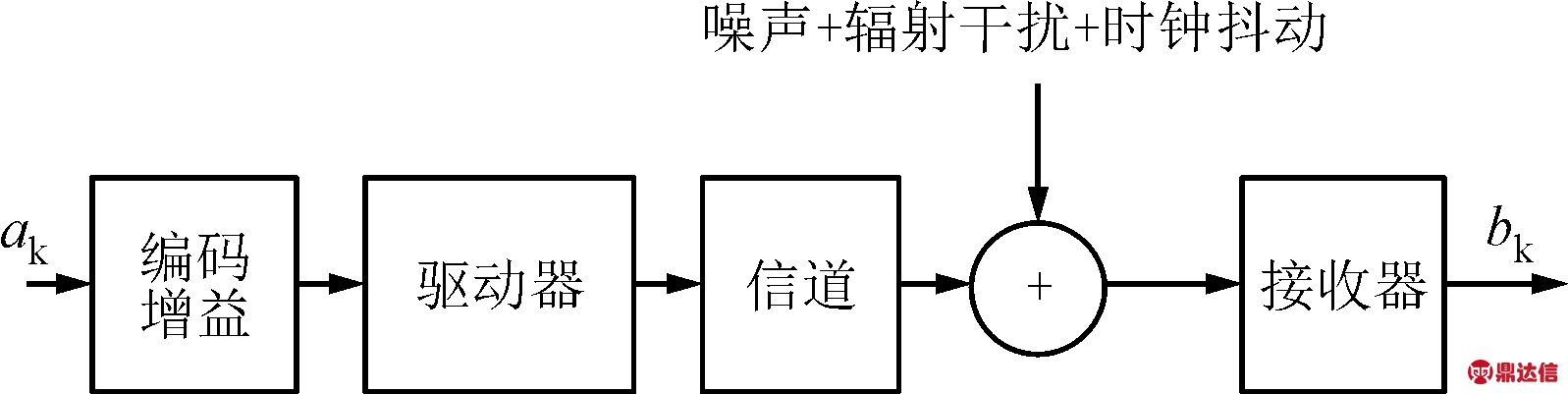

1.3 叠加编码增益及辐照干扰的接口链路评价模型

采用经典的SerDes的链路评价模型对辐照环境下的抗辐照SerDes的表现进行评价,存在两个问题:①无法评价辐照环境对高速SerDes的影响;②未考虑编码对辐照SerDes链路传输过程的影响。因此,本文在经典SerDes链路评价模型基础上引入了编码增益及单粒子干扰,如图3所示。因此,辐照条件下的误码率表达式改写为

(3)

式中:RSN为接收机获得最佳采样的信噪比;Gen为编码增益;GSEE为单粒子干扰对信噪比的衰减。

图3 叠加编码增益及辐照干扰的抗辐照SerDes的链路评价模型

由于直接表征单粒子辐照干扰造成信噪比衰减比较困难,因此本文通过单粒子造成的误码率升高来反映单粒子导致的信噪比降低。单粒子翻转试验时,总的粒子注入量要求CNT,SEE=107 cm-2[18],单个粒子造成的扰动时间tSEE≈2 ns[19]。每次粒子注入不发生多位同时翻转,且传输速率BRATE=3.125 Gb/s,则整个注入过程最大错误二进制码元数NSEE=CNT,SEEtSEEBRATE+2≈6.25×107。

对于传统只采用8B/10B作为PCS编码的抗辐照高速串行接口,它将8 bit的数据拆分成3 bit和5 bit两个分段,再分别进行3B/4B及5B/6B的线性分组编码,并作极性编码换算,因此每个二进制码元错误,有可能导致3个8 bit的原始码错误。对于原始码的误码数NSEE,8B=NSEE×24。设原始码的误码率在无单粒子辐照环境能够达到Pber,8B=10-12,则在单粒子翻转试验环境下只能到Pber,SEE8B=NSEE,8BPber,8B≈2.2×10-3。

根据文献[20],信道增益对串行接口输入误码率、输出误码率的影响关系可以表示如下

(4)

由上述分析可知,Pber,in=Pber,8B,而Pber,out=Pber,SEE8B,所以由式(4)可以算得GSEE≈8 dB。即在单粒子辐照试验环境下,单粒子造成的干扰使得信噪比衰减了-8 dB。

考虑编码增益,由于8B/10B编码的本质是二进制线性分组码,其纠错能力r8B10B=0。二进制线性分组码编码后的误码率可以表示为

(5)

式中:PS为误符号率;n为码长;r为编码可纠错的比特数。对于传统的8B/10B编码,n=10,r=0,因此可由式(5)计算得Pber,out≈PS。借鉴式(4),编码前的误码率可表示为Pber,in=PS,因此可以根据式(4)计算得到编码增益Gen,8B10B≈0 dB。根据式(3),要达到10-12的误码率,需要接收端的信噪比达到30 dB以上,显然是难以实现的。

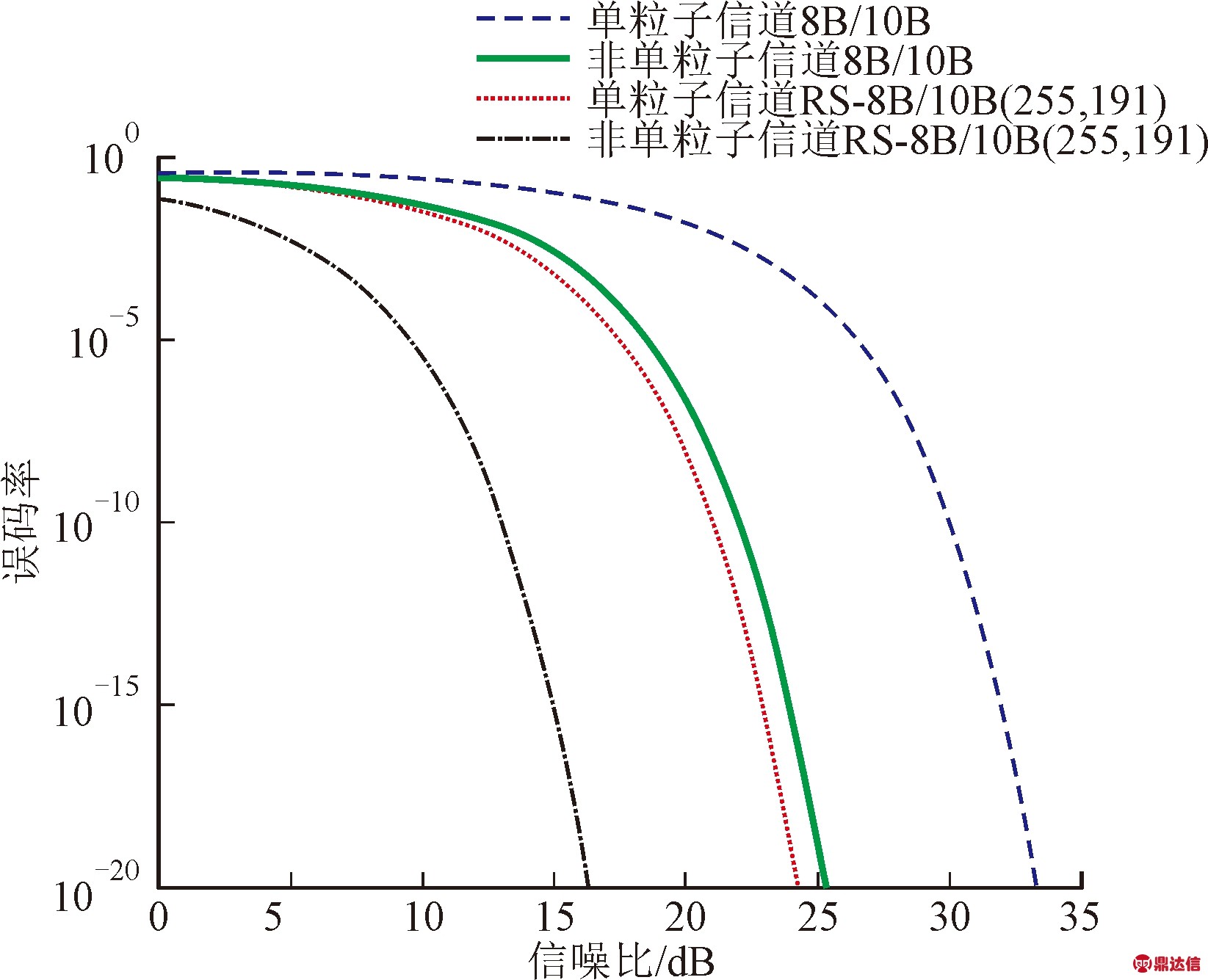

图4 RS(255,191)-8B/10B增益模型与经典非增益模型编码的误码率对比

通过改进的链路评价模型可知,通过增加编码增益Gen,可以抵消单粒子干扰带来的信噪比恶化GSEE。由于8B/10B模型要求8 bit的输入,因此考虑采用RS(255,k)编码级联8B/10B组成RS-8B/10B(255,k)编码方案。由于8B/10B的编码增益为0 dB,所以主要的编码增益由RS(255,k)提供,即Gen,rs-8B10B≈Gen,rs。RS(255,k)的纠错能力rrs=(255-k)/2,属于非2进制线性分组码。根据式(5)可知,由于rrs≥1,所以编码后的误码率一定低于编码前的误码率。假设PS=3×10-3,对于RS(255,239),代入式(4)和式(5),可知编码增益Gen,rs≈3 dB。对于RS(255,223),编码增益Gen,rs≈6 dB。对于RS(255,191),编码增益Gen,rs≈9 dB。因此,采用RS(255,191)的编码增益满足显著提高单比特错误阈值要求。

采用新的评价模型仿真对RS-8B/10B(255,191)和8B/10B两种编码方案,在单粒子辐照及非单粒子辐照条件下,仿真得到的信噪比与误码率的曲线如图4所示。由图可见,采用RS-8B/10B(255,191)编码方案后,即使单粒子环境造成了-8 dB的信噪比衰减,编码提供的增益依然可以保证整个接口的误码率约10-12。

2 SerDes接口芯片电路设计

2.1 PCS编码器结构

本文SerDes接口芯片中PCS编码器的RS-8B/10级联编码如图5所示,将两路并行RS(255,191)编码器通过多路选择器与两路8B/10B编码器连接实现,使输入数据可以选择性地经过RS-8B/10B级联编码,或仅经过8B/10B编码,便于在辐照试验下对比级联编码与仅采用8B/10B编码的效果。编码后的数据进入PMA驱动器转换为高速差分信号VoutP。

图5 级联PCS编码器结构

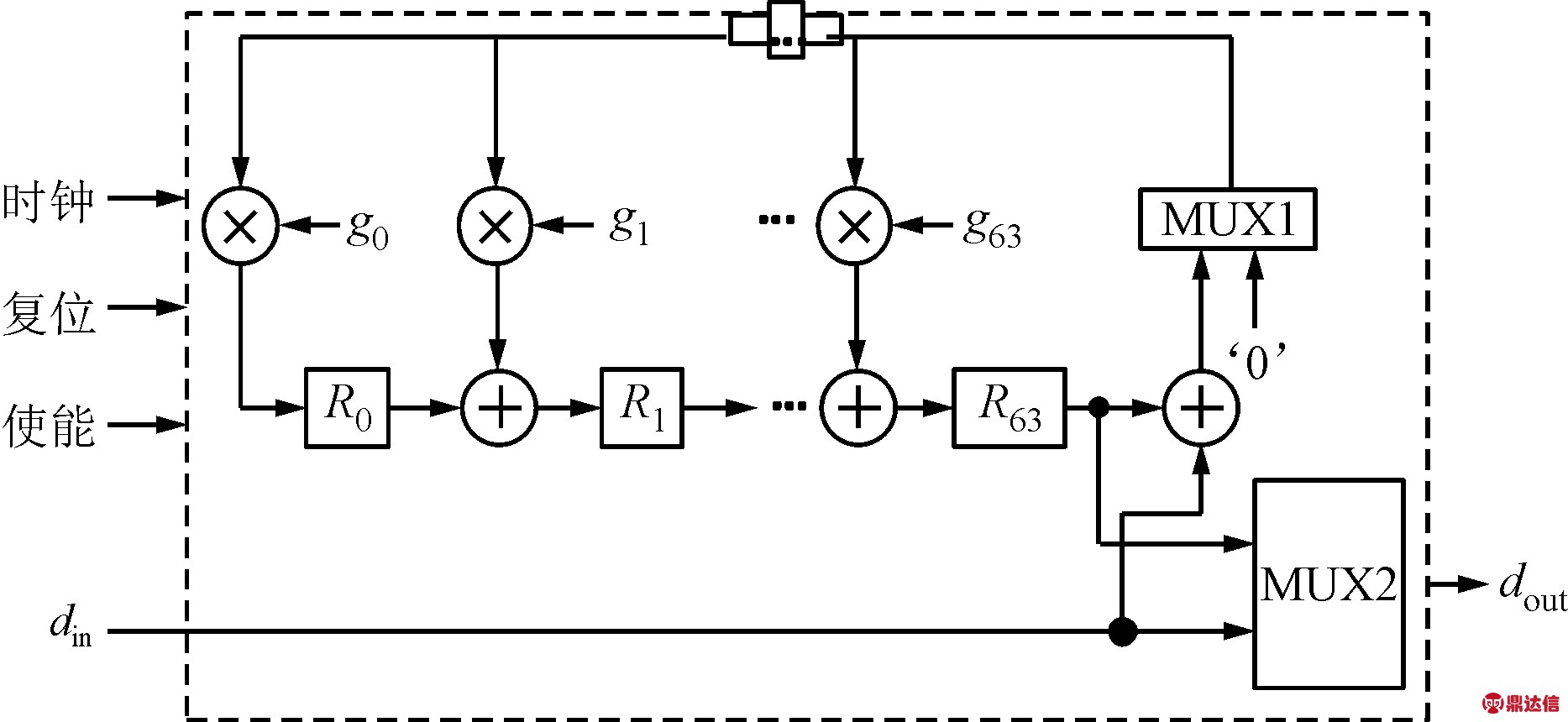

并行RS(255,191)编码采用基于多项式的除法结构,G(x)的各个分量(g0,g1,…,g64)通过查找表的方式固化在芯片内[21]。RS编码器的具体实现方式如图6所示。

图6 RS(255,191)编码器结构示意图

图6中,din和dout分别为RS编码器的输入和输出数据。RS编码器在编码开始的前191个周期,数据din一方面通过MUX2直接输出,另一方面则通过乘除法器、加和移位操作不断更新64个校验寄存器的值。191个数据输入完成后,MUX2选择R63的输出作为输入,MUX1则选择‘0’作为输入。接下来的64个周期里,R63不断更新数据,得到64 B的校验数据。经过RS编码后的2组255 B数据接着送入双路8B/10B编码器,按8B/10B编码的规则进行编码,最终获得2组并行10比特数据流。RS-8B/10B(255,191)级联编码不计校验位的净载荷效率频率为0.6,单独8B/10B编码的净载荷效率效率为0.8。整个级联编码器的工作频率为156.25 MHz,输出并行的20 B编码后数据。经过编码后的20 B并行数据由PMA驱动器转换成差分串行信号(VoutP/VoutN),传输速率为3.125 Gb/s。采用RS-8B/10B编码时的有效载荷码速率1.875 Gb/s,未采用级联编码的有效载荷码速率2.5 Gb/s。

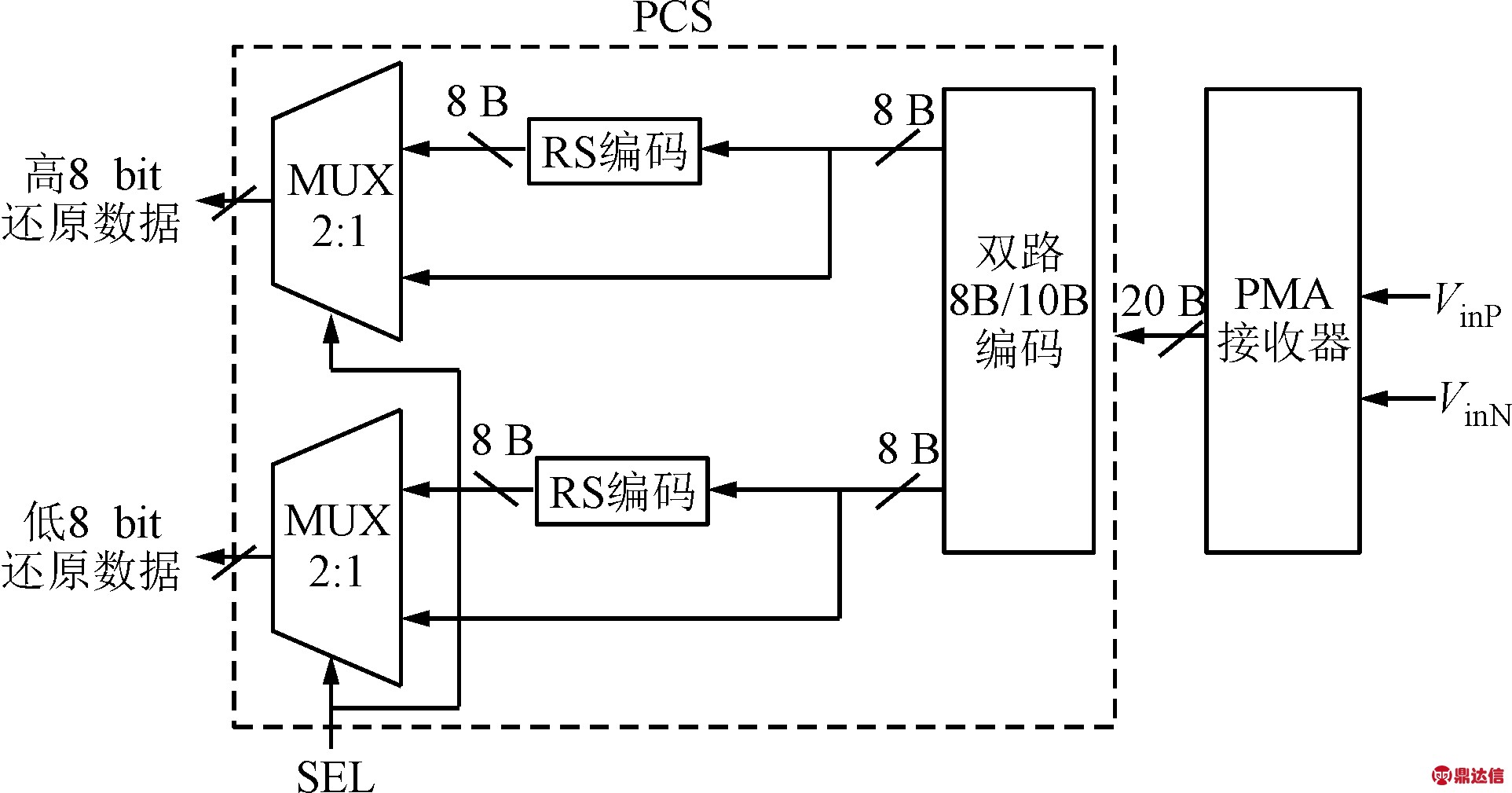

2.2 PCS解码器结构

在接收器一端,数据的处理方式和流向与发送器相反。图7给出了接收器一侧的PCS级联解码器结构,其中PMA接收器对差动输入的高速串行信号VinP和VinN进行均衡处理以补偿信道引起的损耗,之后再通过时钟数据恢复得到同步时钟,并完成数据的串并转换,恢复出20 bit的并行数据。

图7 级联PCS解码器结构

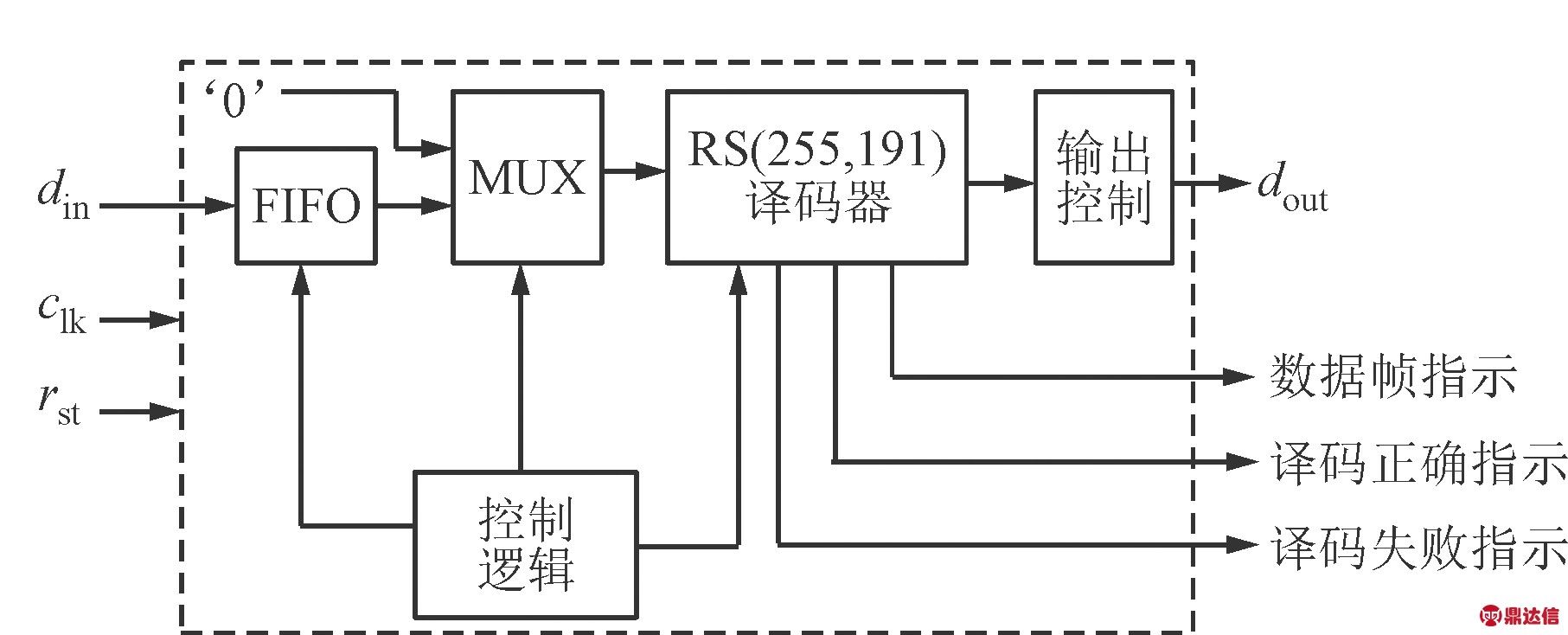

数据首先经过双路8B/10B解码,得到两组8位的并行数据。在发送端数据采用了RS编码的情况下,接收端进行逆向的RS解码,并完成可能的纠错。RS解码器采用iBM(inversionless Berlekamp-Massey)算法,解码器中的主要模块为RS(255,191)译码器,它实现伴随式计算、关键方程求解以及钱搜索3大功能[22]。解码器如图8所示,为并行流水结构,输入din为255 B数据流,包含191 B原始数据以及64 B的校验码数据,译码之后的输出dout也为255 B数据,若传输过程无错发生,或错误字节数量小于或等于可纠正的最大错误字节数,则译码器发出译码正确指示,并输出纠错后的255 B正确数据。若错误字节数超过允许的最大值,则译码器发出译码失败指示信号。

图8 RS解码器结构示意图

2.3 PMA模块主要电路结构

发送端一侧的PMA子层主要实现并行信号的并串及串并转换和传输线驱动接收。为了实现辐照环境下高速传输,本文在发送端采用的密勒补偿的互补电流源差分驱动器(CCMD)[23]。PMA子层的均衡采用了线性均衡器,通过源极负反馈差动对级联来实现信号的均衡。均衡后的信号经过相位插值型的时钟数据恢复电路提取出串并转换和编解码所需的时钟信号[24]。接收电路和发送电路的时钟产生依赖于一个锁相环电路,为抑制辐照下器件特性变化,采用了带有自适应快速锁定的自偏置锁相环结构[25],跟随器件阈值变化自适应地调节电荷泵的偏置电流,使锁相环能够较好地抑制辐照导致器件特性变化。

3 测试结果

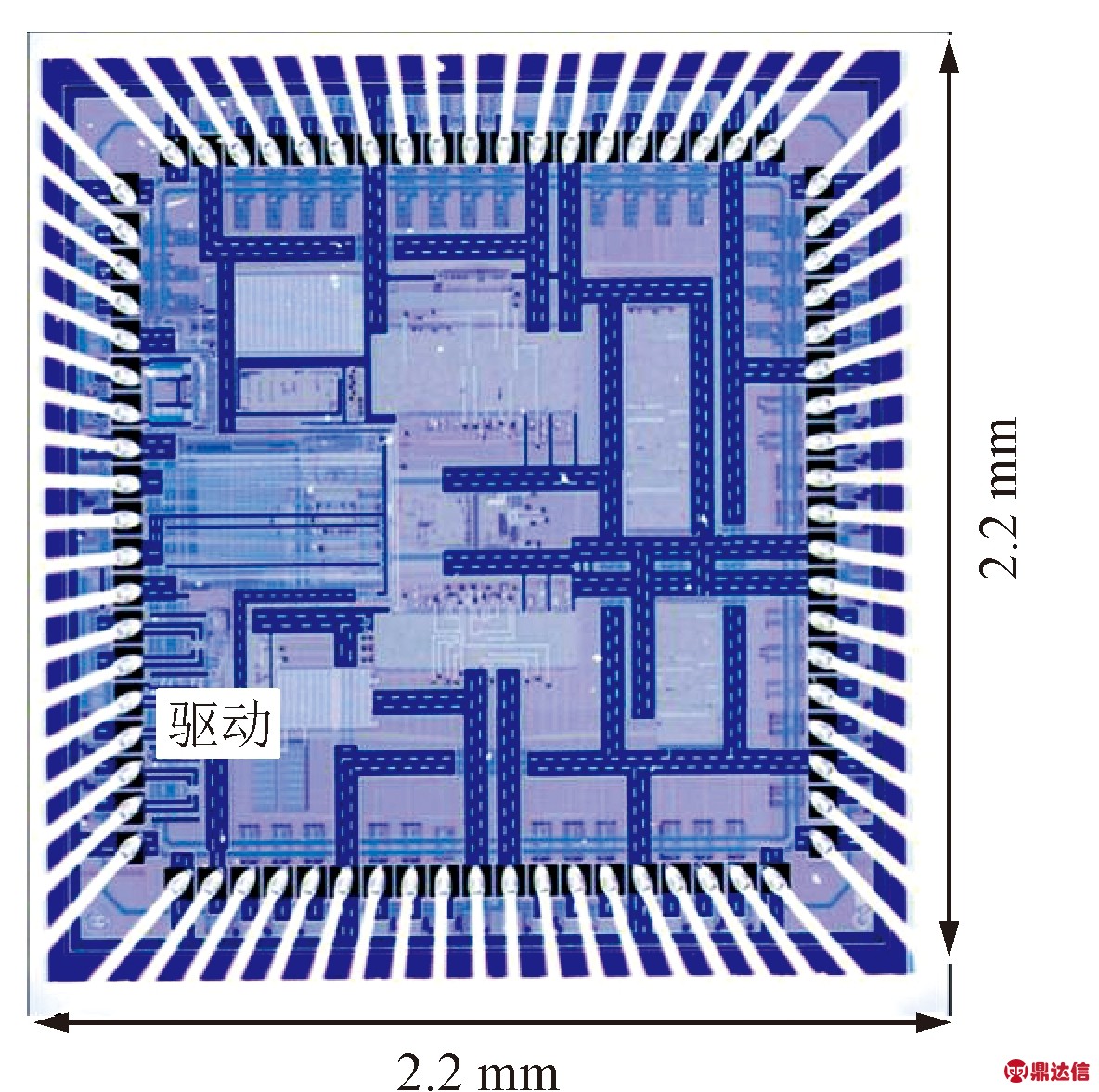

本文级联编码加固的SerDes接口芯片采用0.13 μm SOI CMOS工艺设计,电路中所有器件都用工艺中的3.3 V高阈值器件,以保证电路能够在3.3电源下工作。芯片的显微照片如图9所示,试验电路尺寸为2.2 mm×2.2 mm,全电路功耗约200 mW。

图9 抗辐照SerDes芯片照片

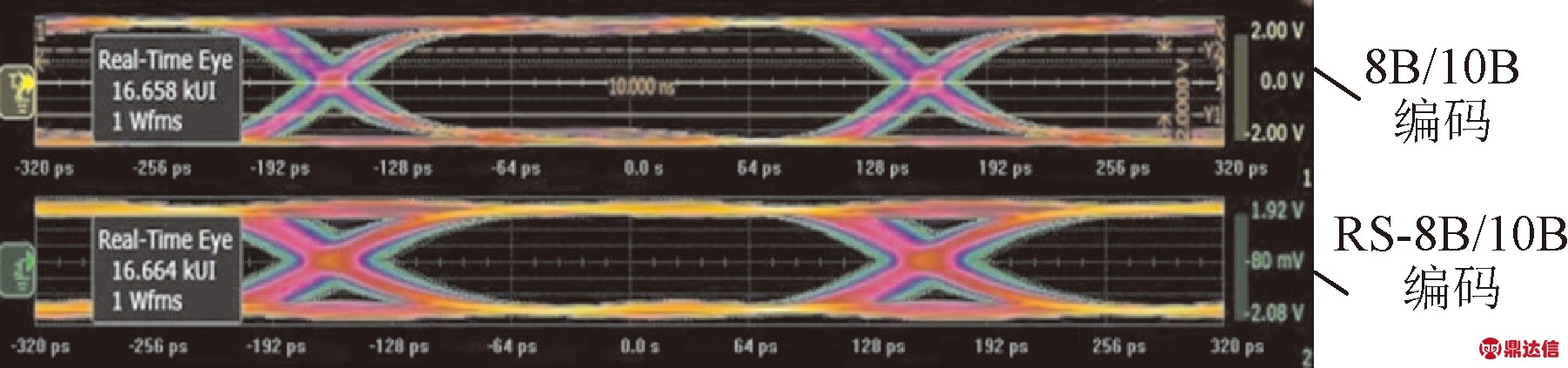

为了评估本文抗辐照SerDes芯片的性能,用5.6 m长的同轴电缆连接2颗芯片搭建了测试系统。在3.125 Gb/s的通信速率、无辐照条件下分别测试了采用8B/10B编解码或采用RS-8B/10B(255,191)级联编码眼图(CCMD接口)的芯片,如图10所示,因为两种模式下的PMA电路是相同的,因此两种编码模式在常规工作条件下的眼图无实质性差别。

图10 芯片采用8B/10B编码和RS-8B/10B级联编码时的眼图测试结果

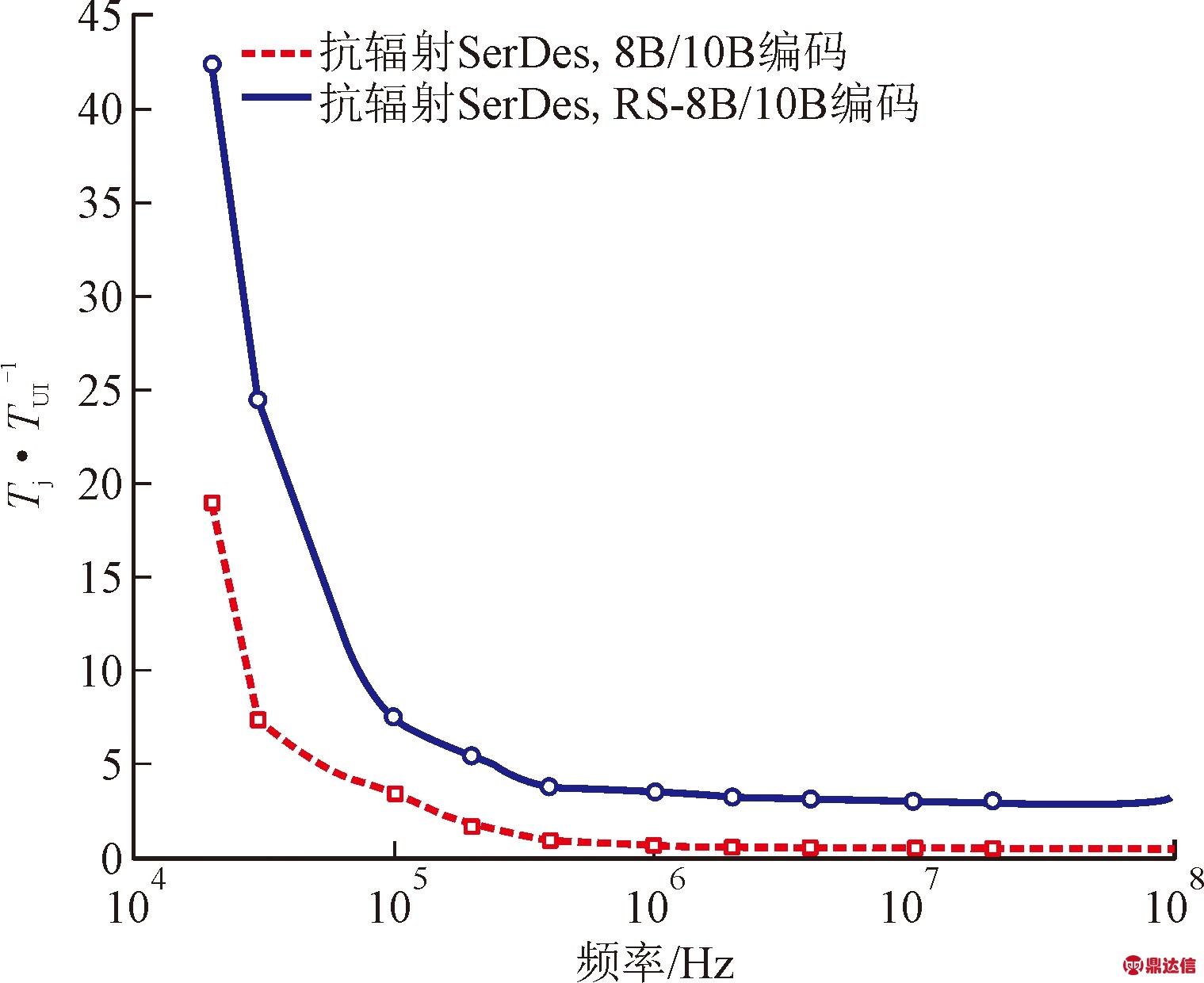

为了验证本文级联编码的抗干扰能力,在常规条件下通过仪器引入周期性正弦抖动,测试芯片在误码率为10-12条件下的抖动容限。

图11 10-12误码率条件下抗辐射SerDes芯片采用两种编码方式的抖动容限与注入频率的关系

图11给出了两种编码方式下注入抖动信号频率与抖动容限(Tj)的关系。图11结果显示:若仅采用8B/10B编码,注入频率分别为100 kHz、500 kHz、1 MHz~10 MHz时,测试抖动容限(Tj)分别为3.1TUI、0.98TUI和0.4TUI(TUI为通信速率的倒数,即单比特数据时长);采用本文提出的RS-8B/10B(255,191)级联编码,注入频率为100 kHz、500 kHz、1 MHz~10MH时,测试抖动容限分别为7.8TUI、3.79TUI和3.5TUI。以上结果说明,RS-8B/10B(255,191)级联编码提高了GEN,增大了SerDes的抗抖动容限。

为测试芯片抗空间粒子辐照能力,对本文的SerDes芯片及辐照试验系统在北京串列加速器核物理国家重点试验室分别采用F粒子、CL粒子、Ti粒子、Ga粒子、Ge粒子、I粒子在垂直射入条件下进行了单粒子诱发电离干扰试验;在兰州重离子加速器国家试验室采用Bi粒子,也进行了相同试验。

以辐照试验系统检测到的试验电路受到不同能量粒子束照射时发生的传输错误数作为基点,拟合绘制了单粒子翻转错误的截面值和粒子LET阈值关系的曲线,如图12所示。将首次观察到单粒子翻转导致的传输错误事件作为单比特错误LET阈值,用来评价电路无错误传输能够忍受的粒子LET能量大小。试验结果显示,在20 MeV·cm2/mg能量以下单粒子对该抗辐照SerDes电路造成的干扰以单比特错误为主,级联RS-8B/10B(255,191)编码增益补偿了单粒子翻转错误导致的信噪比损失。随着入射粒子能量的增加,对于37 MeV·cm2/mg以上的高能粒子,错误数显著增加。主要是由于更高能量的粒子造成了较多的多比特连续错误,因此使用RS-8B/10B(255,191)及使用8B/10B两种情况的翻转截面值随着辐照能量的增长逐渐趋于一致。

图12 单粒子辐照条件下单比特错误测试结果

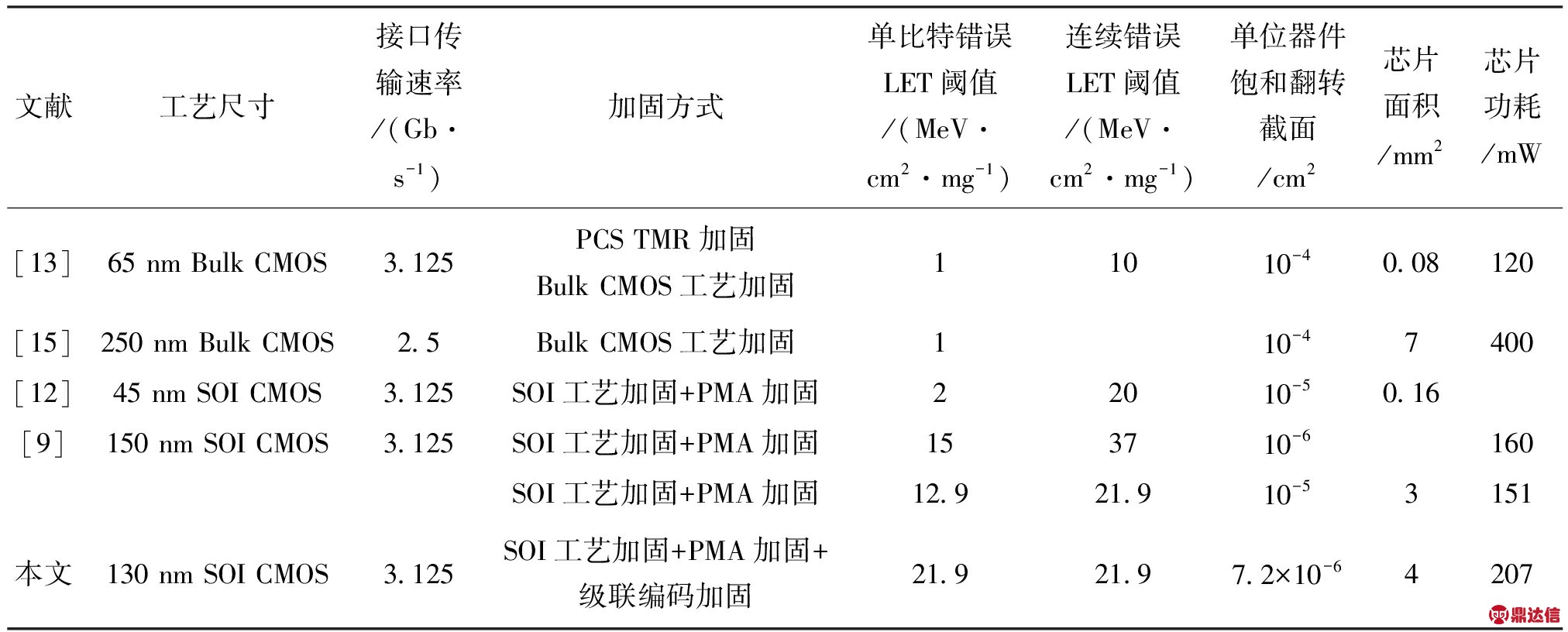

将本文抗辐照SerDes芯片的性能与相关文献进行了对比,结果如表1所示。由表1可见:文献[13]及文献[15]采用的体硅CMOS工艺,由于工艺差异,加固效果都远低于采用SOI工艺加固的文献[12]和文献[9]方法;文献[12]采用SOI工艺,因其内核器件特征尺寸为45 nm且器件电压阈值为1.0 V,比本文采用SOI工艺的130 nm的3.3 V器件特征尺寸要小、电压阈值要低,也未采用级联编码加固,因此更容易受到低能量的粒子导致发生单比特错误;文献[9]与本文采用工艺相近,由于国内外辐照加固工艺技术的差距,不采用级联编码加固时,文献[9]的单比特错误LET阈值及连续错误LET阈值都优于本文;采用级联编码加固后,本文的单比特错误LET阈值优于文献[9],连续错误LET阈值低于文献[9],说明级联编码可显著抑制较低粒子能量导致的单比特错误,但由于工艺加固的差距更高能量粒子造成的连续错误改善有限,在饱和翻转截面方面仍与文献[9]存在差距。对比同类文献,本文在功耗和面积方面付出了较大的设计代价,但对于星载应用,相关代价可以承受。在地球中低轨道,高能粒子分布通量主要在15 MeV·cm2/mg以下。本文的RS-8B/10B级联编码加固方法可显著改善近地轨道的粒子能量导致的错误,以保证SerDes接口芯片在中低轨道星载设备上的可靠工作。

表1 抗单粒子致电离干扰高速SerDes接口芯片性能对比

4 结 论

本文针对空间应用的SerDes芯片的抗单粒子辐照的需求,改进了SerDes链路评价模型,提出了基于信噪比与衰减的辐照SerDes链路评价模型。通过该模型,分析了编码增益对SerDes链路在辐照环境下的信噪比的补偿,并选择RS-8B/10B(255,191)作为抗辐照SerDes芯片的PCS编码方案,并将其编码应用于一款0.13 μm SOI CMOS工艺的速率为3.125 Gb/s的抗辐照SerDes接口芯片中。试验结果表明,采用本文加固设计方法设计的电路能够有效纠正能量在21.9 MeV·cm2/mg以下的单粒子辐照引起的误码,从而保证接口芯片在中低轨道星载设备中的可靠工作。