基于PUF的Logistic混沌序列发生器

黄春光, 程海, 丁群

| 【作者机构】 | 黑龙江大学电子工程学院 |

| 【来 源】 | 《通信学报》 2019年第3期 P182-189页 |

| 【分 类 号】 | O415.5;|TP309 |

| 【分类导航】 | 数理科学和化学->物理学->理论物理学->非线性物理学 |

| 【关 键 词】 | Logistic混沌系统 物理不可克隆函数 序列发生器 流密码 |

| 【基 金】 | 国家自然科学基金资助项目(No.61471158,No.61571181) |

| 【摘 要】 | 由于Logistic非线性混沌系统在一定的参数下,具有初值敏感性和拓扑复杂性等特点,因此Logistic混沌系统可以作为随机序列信号发生器。同时由于集成电路在生产、制作的过程中,即使采用完全相同的设计方法和制造工艺,也会在器件上产生不可控的微小差异,这些微小差异便成为集成电路不可克隆的基础。基于此特点,提出了一种基于可编程逻辑阵列(FPGA)的双输出查找表(LUT)结构的物理不可克隆函数(PUF)的Logistic随机混沌序列信号发生器,该混沌序列发生器具有物理的唯一性,能够有效地抵抗对于系统的复制和攻击。将该系统在Xilinx公司的FPGA开发板上进行测试和验证,结果表明,同样的电路结构和配置文件在不同的FPGA开发板上能够产生不同的随机序列,提高了混沌序列的随机性。 |

| 【全文获取】 |  pdf下载 pdf下载 |

基于PUF的Logistic混沌序列发生器

摘 要:由于Logistic非线性混沌系统在一定的参数下,具有初值敏感性和拓扑复杂性等特点,因此Logistic混沌系统可以作为随机序列信号发生器。同时由于集成电路在生产、制作的过程中,即使采用完全相同的设计方法和制造工艺,也会在器件上产生不可控的微小差异,这些微小差异便成为集成电路不可克隆的基础。基于此特点,提出了一种基于可编程逻辑阵列(FPGA)的双输出查找表(LUT)结构的物理不可克隆函数(PUF)的Logistic随机混沌序列信号发生器,该混沌序列发生器具有物理的唯一性,能够有效地抵抗对于系统的复制和攻击。将该系统在Xilinx公司的FPGA开发板上进行测试和验证,结果表明,同样的电路结构和配置文件在不同的FPGA开发板上能够产生不同的随机序列,提高了混沌序列的随机性。

关键词:Logistic混沌系统;物理不可克隆函数;序列发生器;流密码

1 引言

随着通信技术的飞速发展及互联网络和移动网络的广泛使用,人们越来越关注信息的安全。混沌系统由于具有初值敏感性和拓扑复杂性等特点,得到了广大研究人员的关注[1]。

混沌系统是指在一个确定性的系统中,存在着随机的不规则运动,这种运动具有不确定性、不可重复性以及不可预测性,是非线性动力系统的固有特性。Logistic混沌映射是一种一维混沌系统,当该系统的参数在一定的范围内时,系统会进入混沌状态。由于混沌特性的存在,Logistic混沌映射系统可以应用在随机信号发生器上。为了便于数字电路和FPGA应用Logistic混沌系统,通常采用离散的Logistic混沌映射系统进行设计和开发[2-3]。由于离散混沌系统具有状态随机性和初值敏感性等特点,因此可以将其应用到数字图像加密[4]、随机数发生器[5]以及数字认证等相关领域。

物理不可克隆函数(PUF, physical unclonable function)是一种对集成电路芯片在制造过程中产生的细微差异进行放大并使其产生独一无二的物理不可克隆特征的函数。大多数物理不可克隆函数的实现是通过计算和分析电路的时延信息的差异进行设计的。想要对物理不可克隆函数模块进行复制,需要复制相同的逻辑单元、相同的布局布线,同时在物理电路上进行精确的设计,才能得到相同的结果。但是对于具体的物理电路而言,电路结构和布局布线的差异是由电路自身的物理参数决定的,无法进行克隆复制,因此物理不可克隆函数提供了一种可以在相同的电路结构上产生不同的差异的模块。由于PUF具有基于器件特征的固有随机性,很多研究人员将PUF应用到设备的认证环节[6]和通信环节[7]。

可编程逻辑阵列(FPGA, field-programmable gate array)是一种可编程的芯片,能够根据用户的需求通过软件手段进行更改、配置内部连接结构和逻辑单元、完成指定设计功能的数字电路。由于可编程逻辑阵列具有开发简单方便、实现效率高等优点,已广泛应用到电路设计、嵌入式系统等各个领域。在进行可编程逻辑阵列应用开发的过程中,可以使用芯片提供商提供的开发软件进行逻辑电路的设计和仿真,然后下载到可编程逻辑阵列中。在使用过程中,可以将生成的比特流数据下载到相应的逻辑电路中,完成对于系统的配置。由于电路结构相同,可以将相同的比特流下载到不同的FPGA逻辑电路中,得到相同的功能。由于物理不可克隆函数的存在,即使相同的配置文件,也会产生不同的结果,因此可以对设备进行识别和身份确认。

FPGA具有配置灵活、设计方便等特点,非常适合电路设计。Dabal等[8]利用Xilinx公司的FPGA设计了基于Logistic混沌系统的随机序列,作为流密码发生器。Wang等[9]利用Simulink工具设计了基于FPGA的混沌序列信号发生器,并对相关性进行分析。但是,由于数字Logistic混沌系统产生的序列和器件结构无关,因此容易被复制、攻击和探测。基于此,本文设计了一种基于物理不可克隆函数的Logistic混沌序列发生器,利用FPGA硬件结构的细微差异产生基于器件特征的混沌随机序列,并利用FPGA中的基本单元——查找表(LUT, look-up-table)在不同器件上传输时延的细微差异进行设计,所产生的混沌序列与物理器件相关,相同的电路在不同的FPGA器件上可以产生完全不同的结果。该系统可以作为安全设备的终端,利用在服务器上存储的硬件特征完成设备的验证或数据的加密传输。

2 相关工作

2.1 国内外发展

目前,在通信领域、视频传输、网络通信和个人消费电子产品等相关领域都需要基于FPGA加密技术的数字认证环节[10]。Wang等[11]提出了一种基于FPGA公钥与私钥对的知识产品保护方案。Guajardo等[12]设计了一种基于PUF的加密认证系统。Tuncer等[13]利用Logistic混沌系统作为PUF的初始随机向量,然后对Logistic混沌系统的输出进行判断,产生“0”和“1”的随机序列。该系统采用Logistic信号发生器作为PUF的随机输入。由于PUF的状态有限,没有充分利用混沌系统的状态随机性和初值敏感性,而且该系统的PUF模块在四输入单输出的LUT模块上实现,利用率低,因此只对该系统在单个开发板上进行了测试,没有将其应用到其他开发板,以测试PUF的特性。Liu等[14]给出了一种基于碳纳米管的物理不可克隆函数,采用的混沌方程为Lorenz混沌方程,利用碳纳米管工艺的不确定性,生成PUF。但是由于碳纳米管生成的序列位数有限,而且采用模拟电路进行设计,不利于大规模开发和使用。

2.2 物理不可克隆函数

自2002年以来,人们对基于硅电路的PUF电路进行了深入的研究。到目前,研究人员已经提出了各种物理不可克隆的方法,例如,基于随机存储器的PUF、基于触发器的PUF、基于蝴蝶类型的PUF、基于仲裁器的PUF、基于环形振荡器的PUF[15]、基于电路毛刺的PUF[16]等。产生PUF的方法,大体上可以分为2种,介绍如下。

一种为采用随机存储的方式设计的PUF电路。由于存储电路是由一种状态可以改变的双稳态电路组成的,因此存储电路在通电之前会处于一种随机状态。存储电路在通电之后,寄存器上的状态是一种随机状态,此时存储电路上的高低电平可以作为PUF使用。但是对于芯片设计厂商来说,为了避免这种状态的出现,在电路通电之后,会进行强制复位。只有在设计电路时进行单独设计,才能够使用。

另一种为采用时延的方式设计的PUF,利用物理器件上门电路的时延和布线的时延差异进行设计。在实现方式上,主要分为2种,一种是仲裁型PUF,另一种是环形振荡器PUF。

1) 仲裁型PUF

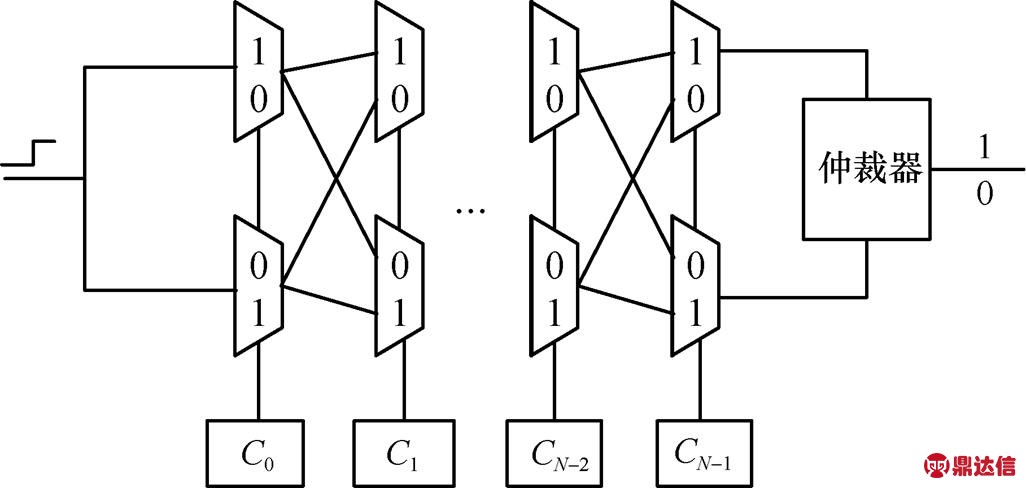

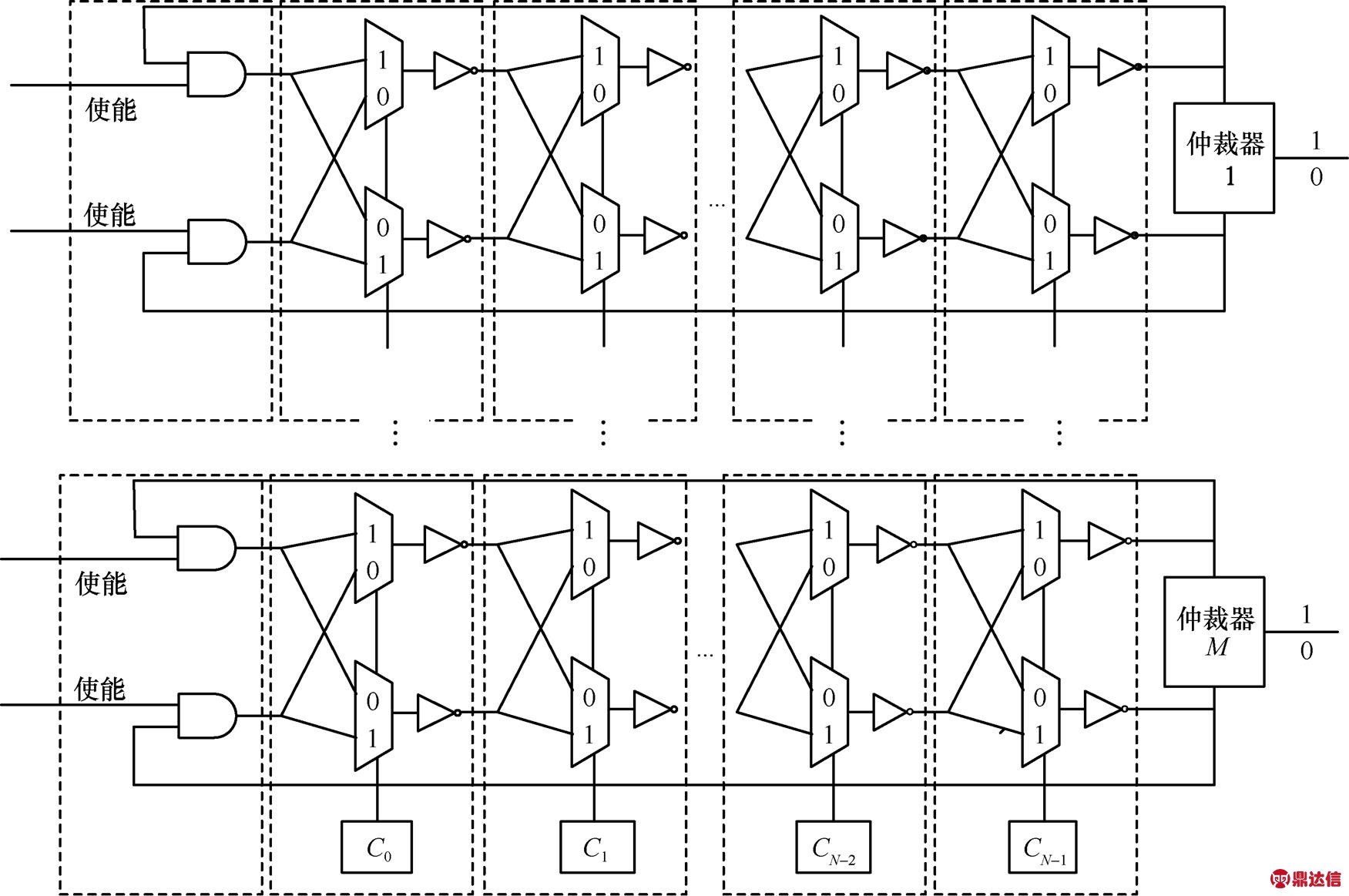

采用2路相同的传输路径,由于集成电路制造工艺的细微差异会产生不同的时延,判决器根据2路传输路径到达时间的差异决定输出是“0”还是“1”,从而产生基于器件自身特点的随机信号。仲裁型PUF的控制端控制信号传输的路径,系统输入端输入同一个脉冲信号,利用控制信号进行路径选择,使信号经过不同的传输路径,根据信号到达仲裁器的先后顺序进行判决。

在PUF设计过程中,需要尽量保证传输路径的长度一致,但是由于物理元件的差异,最终会导致同一个脉冲到达仲裁器的时间不尽相同。如图1所示,仲裁类型PUF利用控制信号(C0,C1,…)选择信号传输的路径,输入的是同一个脉冲信号,经过不同的路径到达仲裁器,仲裁器根据脉冲信号到达的先后顺序进行判决,决定输出是“0”还是“1”。这类PUF需要的多路选择器级别多、路径长,否则无法分辨到达的先后顺序,即使能够判决,也容易被外界环境干扰。

图1 仲裁型PUF

2)环形振荡器PUF

利用反相器级联形成振荡电路,通过计数器进行计数。由于物理电路结构的微小差异,经过多次计数,2个计数器的结果不尽相同,然后通过比较器,得到最终的结果。

图2中与门作为控制端,控制环形振荡器PUF的起振和停止。与门和后面的多个反相器相连接,构成一个连续反向的环。该环形振荡器产生的脉冲信号作为计数器的时钟,进行计数。计数器设定计数的截止上限,当其中任意一个计数器计数达到上限,则环形振荡器停止工作。在进行布局布线过程中,要求保证路径长度一致。比较器通过比较2个计数器数值的大小,输出“0”或“1”。

图2 环形振荡器PUF

在环形振荡器PUF中,如果反相器的个数为奇数,需要使用与门作为控制模块,控制环形振荡器的工作状态;如果环形振荡器中反相器的个数为偶数,则采用与非门作为控制模块。

环形振荡器PUF所需的与非门的个数少,相对仲裁型PUF来说占用资源少,外界环境影响小。

2.3 Logistic混沌方程

Logistic方程为混沌系统的经典实例,系统结构简单,便于FPGA设计、实现和验证,同时便于推广到其他混沌系统。

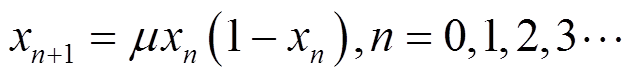

Logistic函数的数学表达式为

(1)

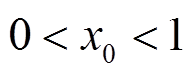

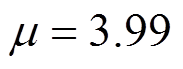

(1)其中, 是Logistic方程的系统参数,系统的初值设为

是Logistic方程的系统参数,系统的初值设为 (

( )。当

)。当 时,系统进入混沌状态。

时,系统进入混沌状态。

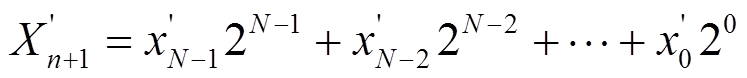

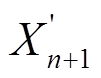

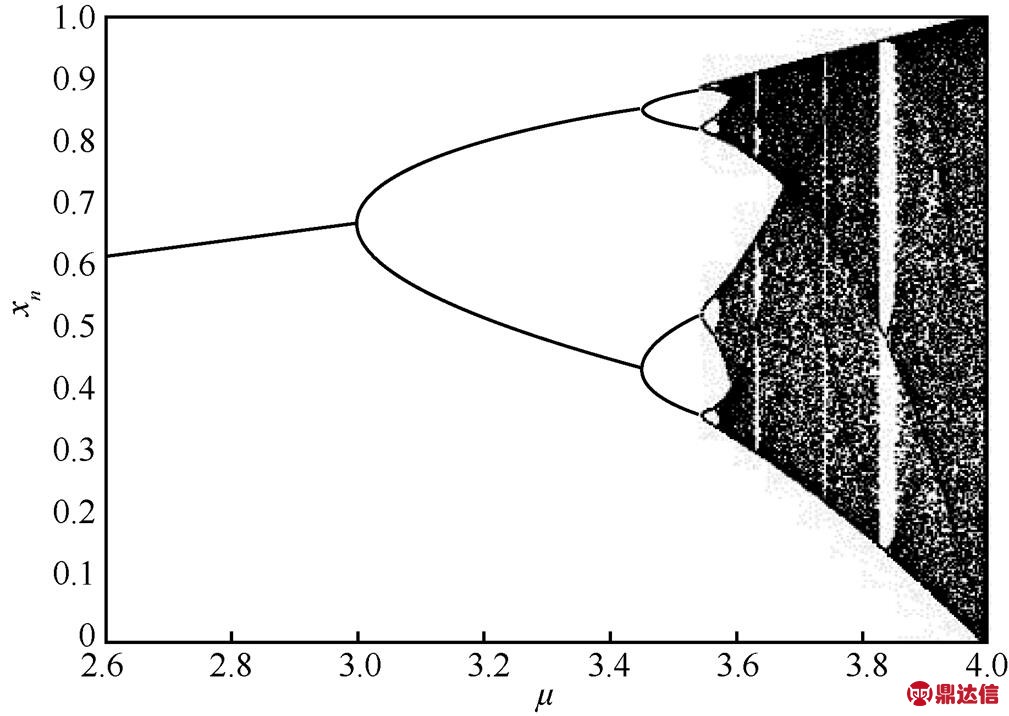

如图3所示,随着 的增加,Logistic混沌系统分岔越来越多,系统逐渐进入混沌状态。如果在FPGA上实现Logistic混沌电路,则需要对Logistic方程进行离散化,Logistic方程的每次迭代结果采用

的增加,Logistic混沌系统分岔越来越多,系统逐渐进入混沌状态。如果在FPGA上实现Logistic混沌电路,则需要对Logistic方程进行离散化,Logistic方程的每次迭代结果采用 位二进制数表示,即

位二进制数表示,即

(2)

(2)式(2)是Logistic方程的二进制表现形式。其中, 为二进制的表现形式,

为二进制的表现形式, 是二进制每一位的值。

是二进制每一位的值。 的位数越大,Logistic方程的精度越好,同时需要的运算量就越大。

的位数越大,Logistic方程的精度越好,同时需要的运算量就越大。

图3 Logistic分岔图

3 系统设计

基于环形振荡器的PUF,利用有限个数的反相器,构建一个反馈链。基于仲裁型的PUF,可以利用控制位选择相应的路径,根据判决器的结果产生“0”或“1”。本文提出基于混合型PUF的Logistic序列发生器,同时利用环形振荡器PUF与仲裁型PUF的特点,产生基于物理器件特征的随机数。利用Logistic混沌方程对系统初值的敏感性(如图3所示),初值的细微差异会产生完全不同的变化轨迹。利用Logistic方程的特点,将PUF与Logistic迭代方程相结合,既利用PUF的硬件唯一性,又利用Logistic函数的敏感性,产生与硬件相关的混沌序列,同时在Xilinx公司的7-series FPGA上进行设计和验证。

3.1 基本单元模块

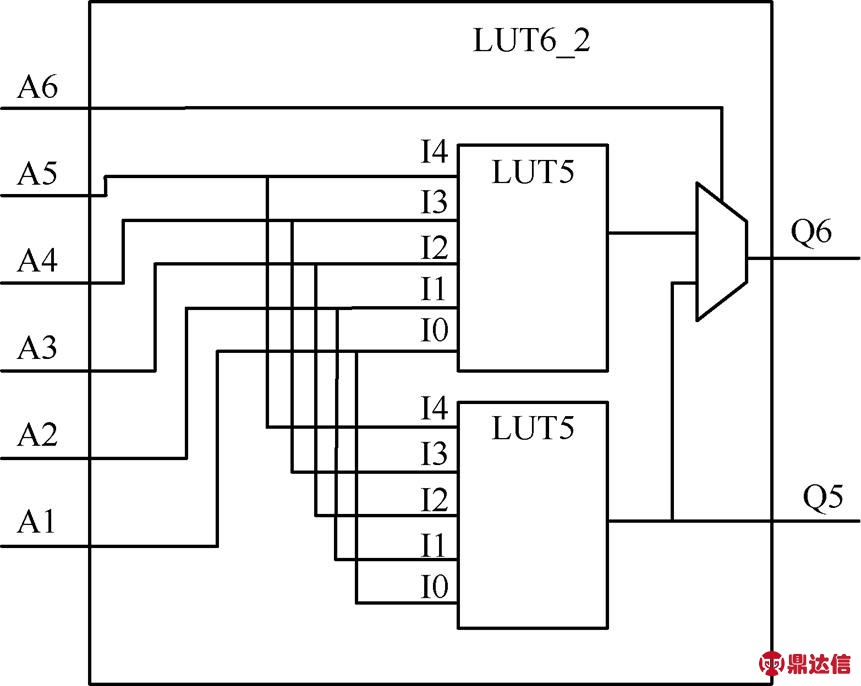

本文采用FPGA进行设计和开发。由于FPGA具有大量的可编程资源,为系统的实现提供了相应的功能模块,既解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。Xilinx公司的FPGA具有6输入2输出的LUT模块,有利于多输入多输出的应用模块设计。

Xilinx公司的7-series FPGA的基本单元为CLB,每个CLB由2个SLICE组成,每个SLICE由4个5输入的LUT、3个MUX、一个CARRY和8个FF组成。

如图4所示,Xilinx公司7-series FPGA的每个LUT有6个输入端口,当A6设置为高电平时,可以作为2个5输入的LUT使用,可以有2个输出。在设计过程中,需要对LUT6_2模块进行配置,将其配置为2输入2输出的与门电路和2输入2输出的非门电路。

图4 FPGA的基本单元LUT6_2

对于图5中的2输入2输出非门电路,即图中虚线内部的模块,可以用一个LUT6_2进行设计。可以充分利用LUT6_2的2个输出的特性,将A6设置为高电平,而A5和A4输入没有使用,可以配置高电平或低电平,不能悬空使用。在本设计中,A4和A5设置为低电平,这样就可以使用Q5和Q6这2个输出,则电路等效如图5所示。

图5 基于LUT6_2的双路非门电路

每个模块有3个输入,其中,A3作为选择信号,A2和A1作为数据的2个输入端口,此时,该电路模块为3输入2输出的功能模块。根据真值表进行计算,可以得到LUT6_2的配置码为0x0000c0a0_0000a0c0,此时LUT可实现双路非门和路径选择的功能。

同理,将LUT6_2设计为2输入2输出的与门时,每个模块有4个输入,其中,A6为高电平,A5为低电平,A4作为使能信号,A3作为选择信号,A2和A1作为数据的2个输入端口,则根据电路的功能设置相应LUT的数值。根据真值表进行计算,可以得到LUT6_2的配置码为0x00000035_ 00000053,此时LUT可以实现双路与门及路径选择的功能,如图6所示。

图6 基于LUT6_2的双路与门电路

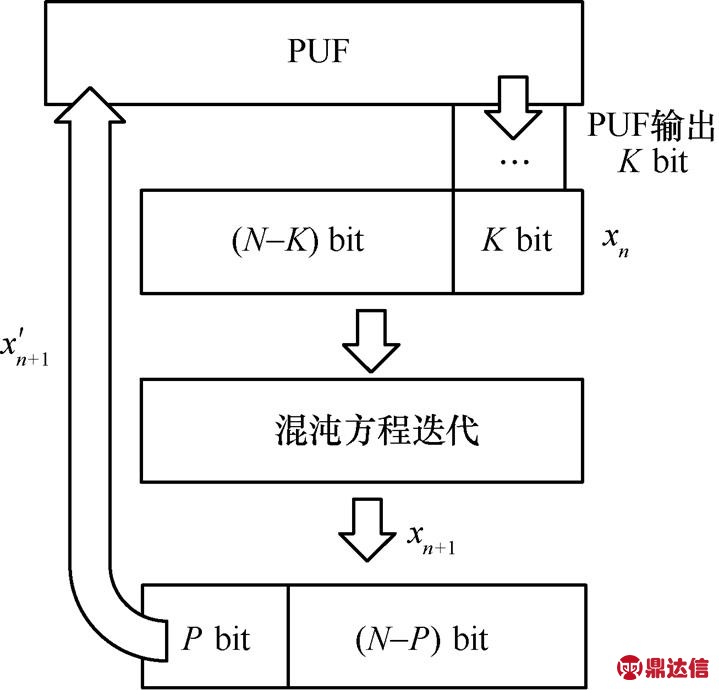

3.2 系统框图

本文设计一种基于Logistic方程的PUF,系统框图如图7所示。利用LUT6_2进行配置生成与门和非门,利用控制端口选择信号传输的路径,形成环形振荡器PUF,通过改变控制端口信号的状态,可以改变信号传输的路径,得到不同的随机数。如果一个系统有 级选择电路,则可以产生

级选择电路,则可以产生 种状态。

种状态。

系统工作流程如图8所示。序列发生器首先利用PUF产生的随机数作为Logistic每次迭代运算的初值 所对应的二值序列的低位,然后代入混沌方程进行迭代,产生

所对应的二值序列的低位,然后代入混沌方程进行迭代,产生 ,再将

,再将 的二值序列的高位作为PUF控制信号,最后利用PUF生成的随机序列构建Logistic方程的初值

的二值序列的高位作为PUF控制信号,最后利用PUF生成的随机序列构建Logistic方程的初值 ,并进行迭代运算。

,并进行迭代运算。

图8 系统工作流程

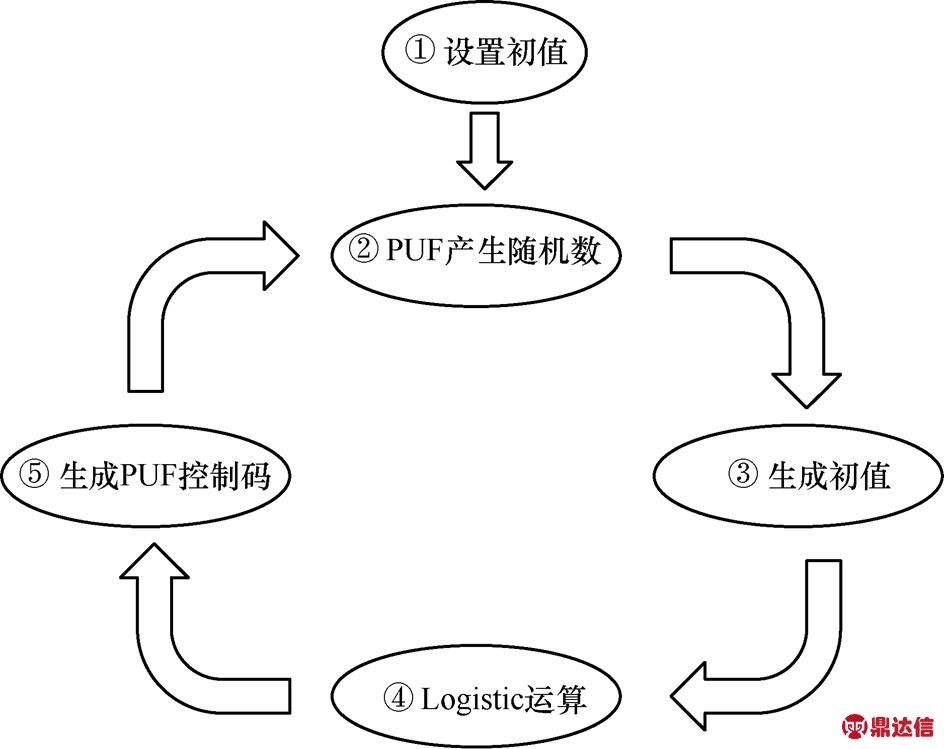

系统工作状态机如图9所示,分为5个步骤。

图9 系统工作状态机

图7 系统框图

步骤1 设置系统的初值,PUF的结构有P个控制端,用来选择PUF的不同路径。由于PUF的特点,不同的PUF所产生的结果不完全一样。

步骤2 利用PUF模块生成K bit,将K bit传递给Logistic混沌系统。

步骤3利用PUF传递过来的K bit和原有的N bit的后K bit进行异或处理,得到 。

。

步骤4 将生成的N bit的数据输入Logistic混沌系统进行迭代运算,生成 。

。

步骤5 将 的前P bit作为PUF的控制信号,生成下一轮迭代运算的初值

的前P bit作为PUF的控制信号,生成下一轮迭代运算的初值 。

。

4 系统分析与测试

在本文系统中,由于PUF的存在,使原来混沌系统无法迭代到的点重新成为系统的初值,破坏了离散混沌系统的周期性,为了测试基于PUF的Logistic混沌序列发生器的特性,采用Xilinx公司的7-series FPGA开发板进行测试,并对序列发生器的相关特性进行了分析和讨论。

4.1 实验环境

本文在Xilinx公司的7-series FPGA上设计了基于物理不可克隆函数的Logistic混沌序列发生器,设计软件采用Xilinx公司的vivado 2017.4版本进行设计开发,并利用vivado自带逻辑分析仪进行数据测试和分析。在实验过程中,对4块同样的FPGA开发板进行测试,通过XDC文件对模块的具体位置和走线利用约束条件进行限定,同时将PUF布置到FPGA的不同位置进行测试。

本系统利用LUT6_2设计了32路PUF,通过对32路PUF的计数器输出的数值进行比较,得到32 bit的输出。

4.2 实验数据

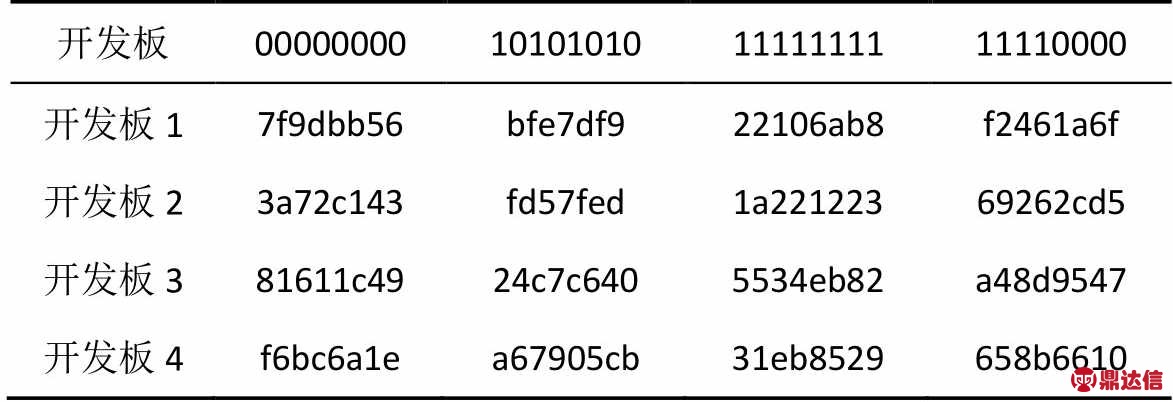

在实验过程中,同样的配置代码在不同的FPGA开发板上的结果并不相同。首先,相同的Logistic初始向量作用到PUF上,不同的开发板得到的结果如表1所示,结果呈现出随机性。

表1 不同开发板在相同配置下的输出结果

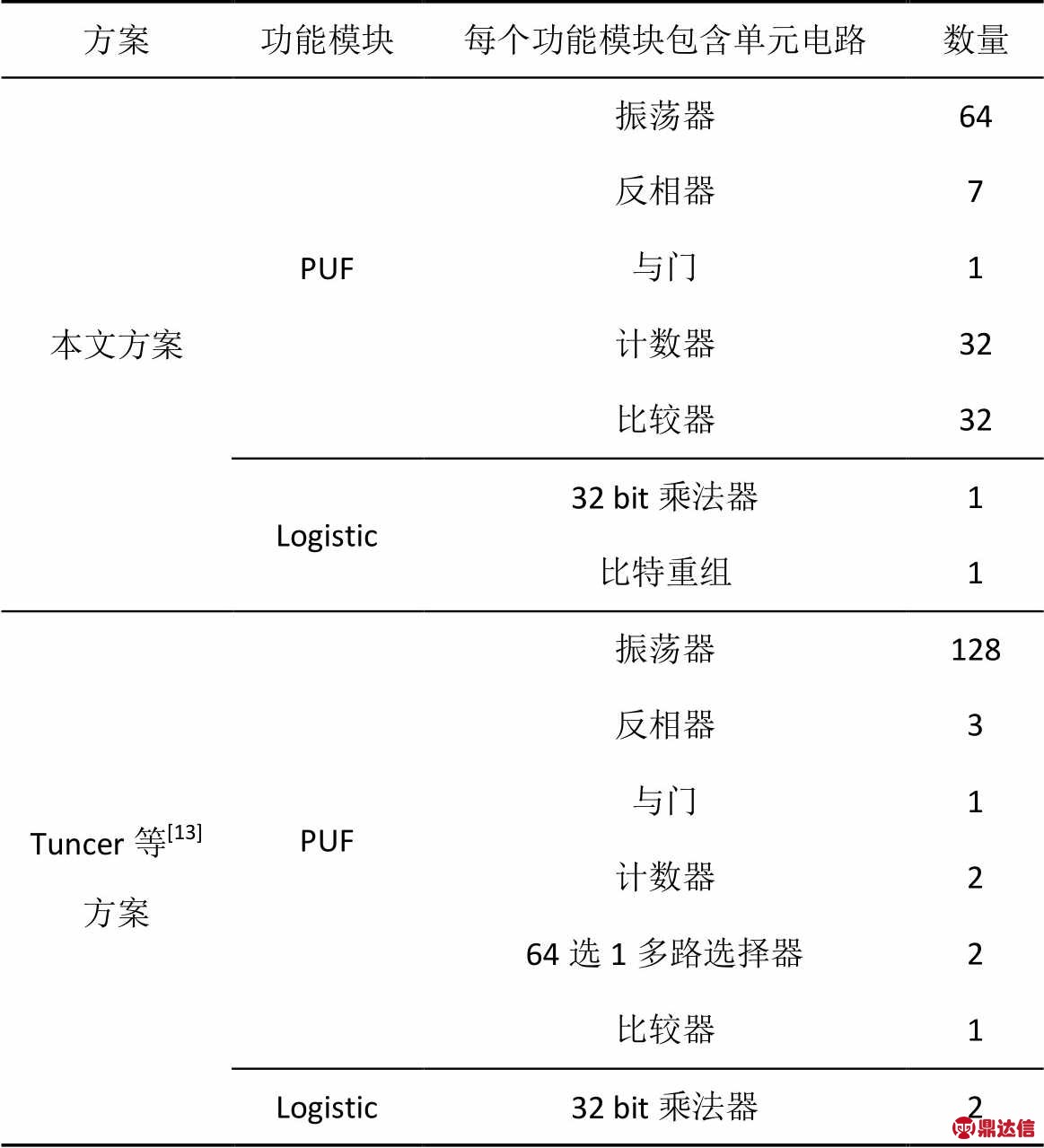

系统的硬件开销如表2所示。由于系统采用LUT6_2的单元电路,每个单元模块包括6个输入和2个输出,因此每个LUT模块可以实现2路PUF电路,由于LUT模块具有6个输入端口,可以选择其中一个端口作为控制端口,使得硬件的利用率得到提升。Tuncer等[13]使用LUT4_1模块,每个模块可以实现一路PUF电路,利用率低。

表2 硬件开销说明

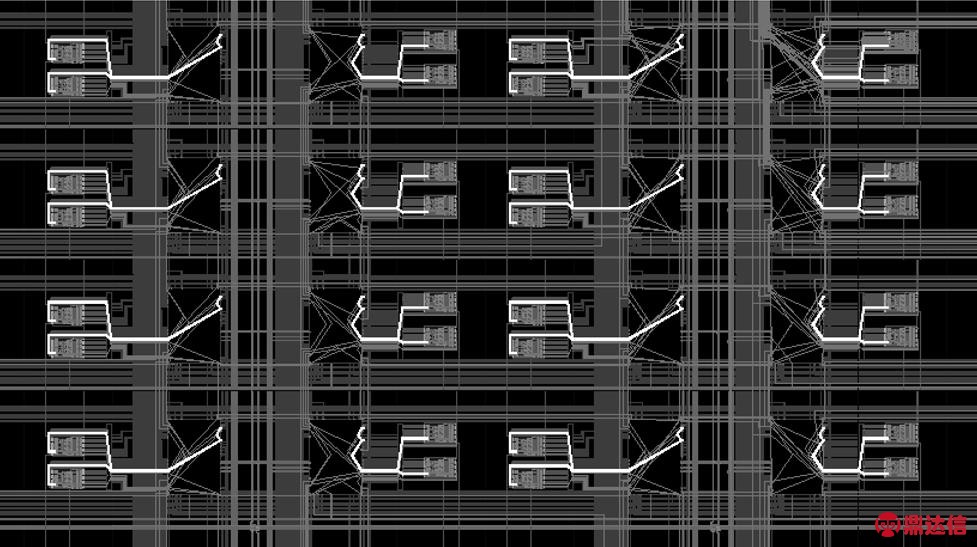

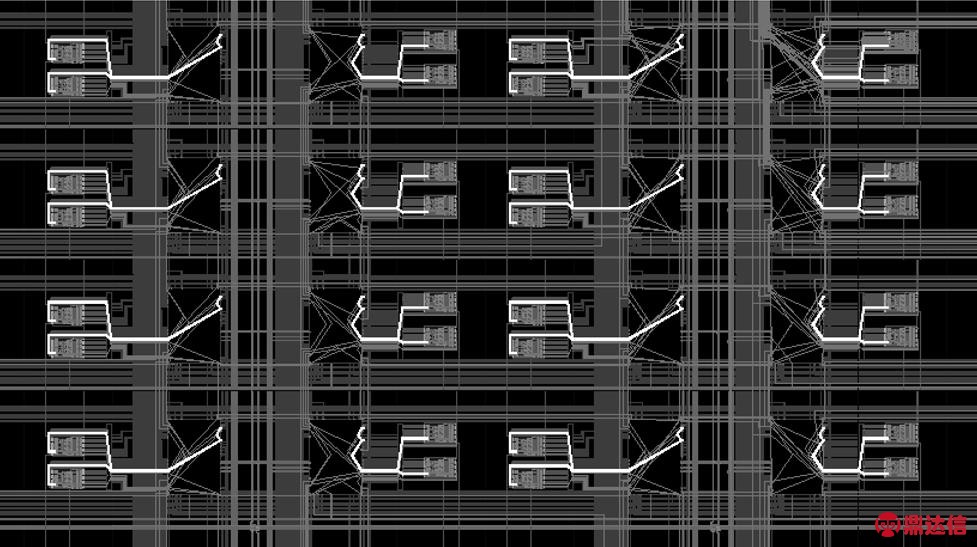

在设计过程中,Logistic混沌方程采用64 bit精度进行计算。PUF单元的布局布线如图10所示,K=32,N=64。利用PUF的输出序列构建混沌系统的 ,利用vivado 2017.4中Multiplier模块进行乘法器设计,然后产生64 bit的

,利用vivado 2017.4中Multiplier模块进行乘法器设计,然后产生64 bit的 。设计模块采用32位PUF,选取32 bit的数值作为PUF的控制码进行下一轮迭代运算。每个模块的布局布线要求对称,以保证传输路径长度一致。

。设计模块采用32位PUF,选取32 bit的数值作为PUF的控制码进行下一轮迭代运算。每个模块的布局布线要求对称,以保证传输路径长度一致。

图10 PUF单元的布局布线

4.3 数据分析

4.3.1 相关性分析

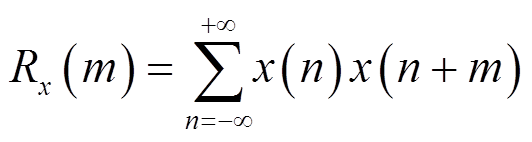

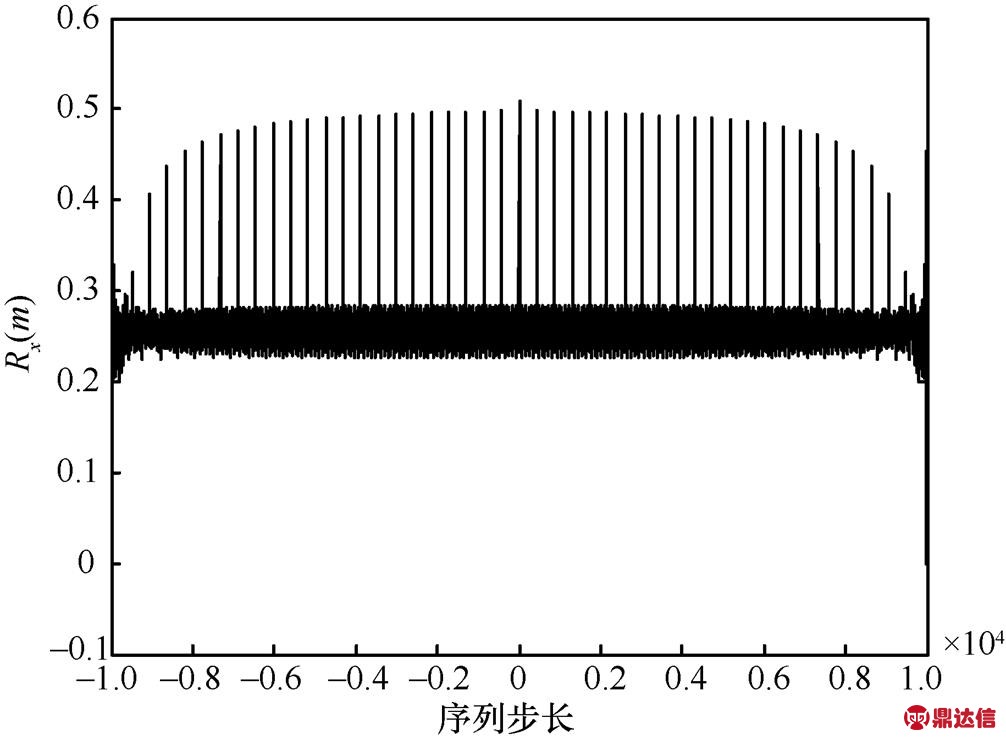

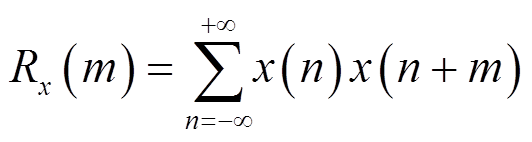

为了验证本文改进算法对于Logistic混沌输出序列的影响,对FPGA输出的序列进行了测试。由于在FPGA上运行Logistic混沌方程,必然要对混沌系统进行离散化处理,混沌系统由于系统的离散化而发生性能的改变[17]。自相关性是衡量一个信号在不同时间的相互依赖关系,即系统的随机性是否相互独立。设 是“0”或“1”的二值序列信号,

是“0”或“1”的二值序列信号, 表示此信号的自相关函数,可以表示为

表示此信号的自相关函数,可以表示为

(3)

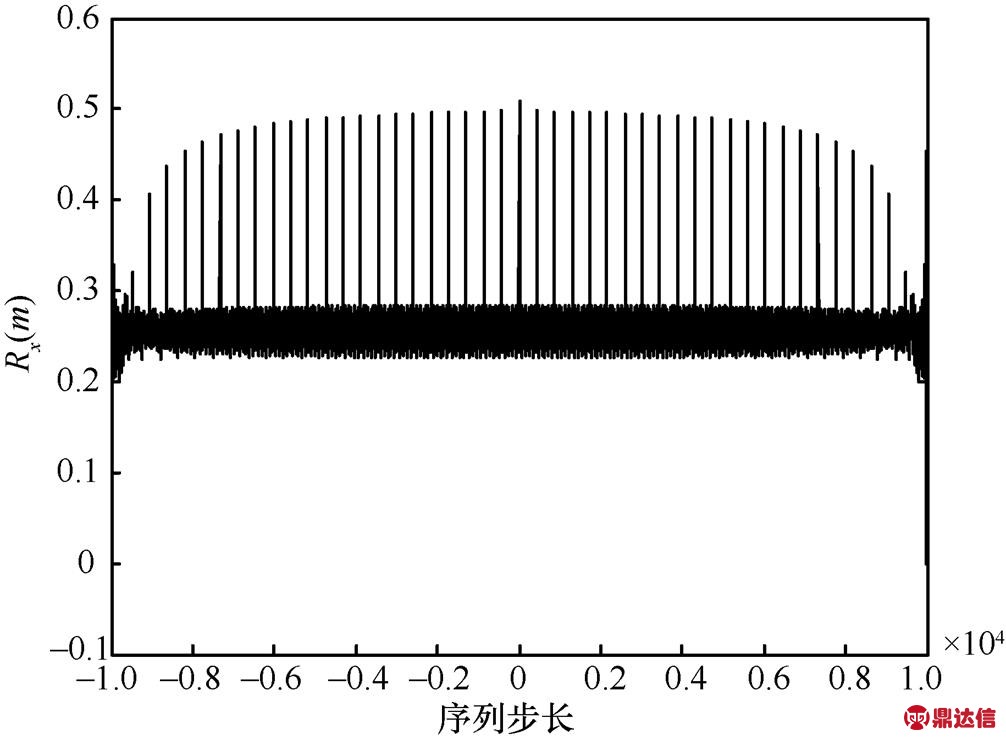

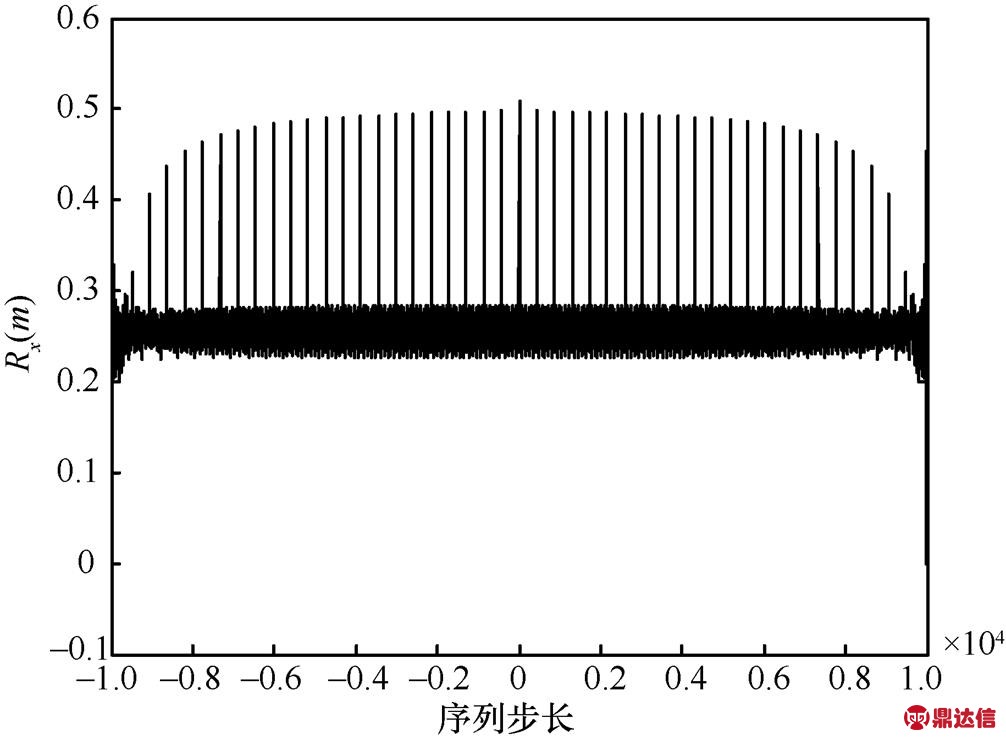

(3)通过对混沌序列发生器的输出进行分析和设计,对于原始的Logistic混沌系统,采用32 bit的精度进行计算,自相关函数如图11所示,对于不同的Logistic初值,系统会出现一些周期现象。

图11 32 bit的Logistic混沌方程自相关结果

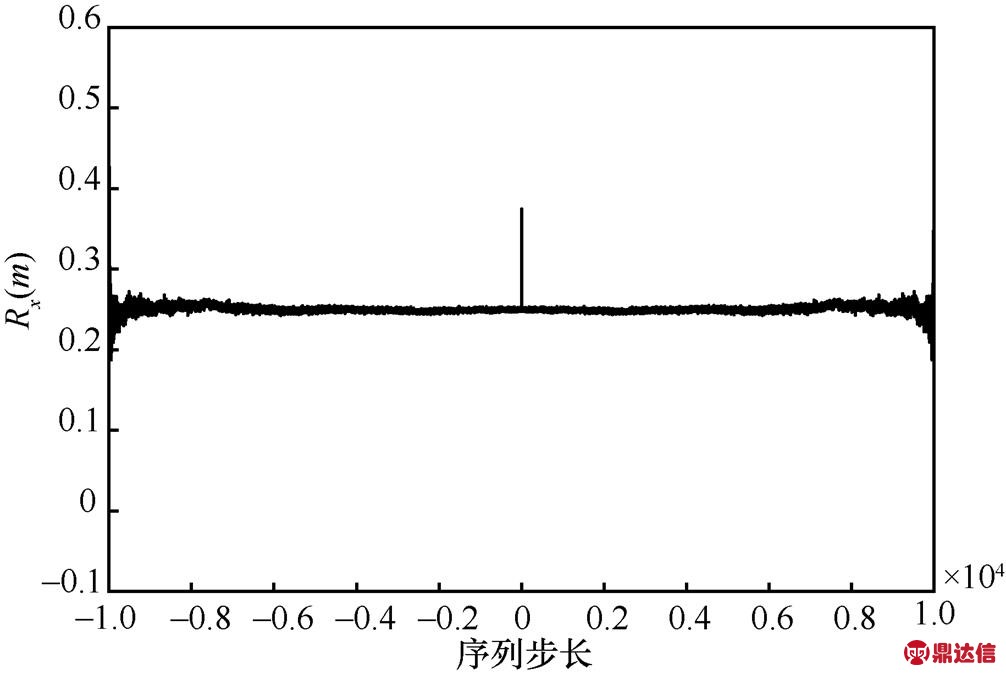

如果采用基于PUF的Logistic混沌系统进行设计,可以阻止Logistic混沌系统周期现象的出现。同时,由于PUF系统的存在,使Logistic混沌轨道上无法迭代到的点可以成为系统的初值进行计算,改善了系统的周期性,如图12所示,系统不存在明显的周期性现象。

4.3.2 随机性分析

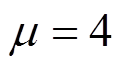

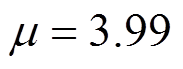

为了验证序列的随机性,本文采用美国国家标准与技术研究院(NIST, National Institute of Standard and Technology)提供的15种随机数检测方法NIST SP 800-22进行检验,评价指标P值的对比结果如表3所示,通过全部测试表明,基于PUF的混沌序列信号发生器产生的数据是满足随机性的要求的。在本文的方案中, ,而在Tuncer等[13]的方案中,Logistic参数

,而在Tuncer等[13]的方案中,Logistic参数 ,相应地会增加一个乘法器来计算Logistic方程,带来硬件资源的消耗。

,相应地会增加一个乘法器来计算Logistic方程,带来硬件资源的消耗。

图12 基于PUF的Logistic序列自相关函数

表3 评价指标P值的对比结果

5 结束语

本文提出了一种基于物理不可克隆函数(PUF)的Logistic混沌序列发生器,利用FPGA器件的LUT以及传输路径在生产过程中的工艺差异进行设计,所以即使同样配置码下载到不同的FPGA开发板上,产生的结果也不同。首先利用Xilinx的FPGA中的LUT6_2设计了2路PUF结构,相对于传统的FPGA而言,节省了一半的资源;然后利用PUF产生的随机数对Logistic混沌系统进行优化,设计了Logistic混沌序列信号发生器。该序列发生器产生的序列与物理器件的特性相关,利用物理器件的特征参数作为序列发生器的原始密钥,保证了序列发生器的唯一性。NIST检验表明,混沌序列信号发生器产生的序列满足随机性的要求。