摘要: 随着网络传输数据流量的爆炸性增长,传统电交换由于其有限的带宽和高功耗将很难满足网络带宽发展需求。光交换能直接在光域上完成光信道间信息的交换,具有高速、宽带、透明、低功耗以及潜在的低成本等诸多优点,能满足下一代全光交换网络、数据中心和高性能计算机光互连网络建设的迫切需求。文章介绍了集成光开关的发展现状及核心技术,包括采用氧化硅、III-V族半导体材料和硅材料来制作光开关的进展以及各种技术的特点。其中硅基集成光开关具有结构紧凑、功耗小、成本低以及与互补型金属-氧化物-半导体(CMOS)工艺兼容的优势,适合大规模光开关制作和量产,具有潜在的巨大市场商用价值。文章重点介绍了实现硅基光开关的核心单元器件以及几种代表性光开关阵列,并对光开关状态监控和调节以及光电封装做了阐述。

关键词: 硅基光电子;光开关;光波导;集成光子学

0 引 言

在现如今这个数字时代,网络传输数据流量的增长速度日益加剧。受到各种大数据应用诸如云计算和高清晰视频传输等的推动,数据中心内部机柜之间的数据传输量将会激增。随着对数据流量的进一步需求,未来数据中心的规模势必将继续扩大,服务器机柜的数量将会进一步增长。数据中心内部流量估计约为全球互联网流量的4倍,且继续以每年27%的速度增长[1]。数据在数据中心内的服务器/存储器之间的流量超过了出入站流量。在数据交换节点处采用光-电-光的交换方式,势必将会受困于电子交换技术的发展瓶颈。光-电-光的信号交换模式有能耗高和体积庞大的缺点,而采用全光交换的光互连技术直接在光域完成光信道间信息的交换,则具有高速、宽带、透明、低功耗以及潜在的低成本等诸多优点,一直被看作是克服传统的电子交换技术瓶颈的方法。光互连技术目前仅以点对点光学链路的形式使用。不断增长的数据流量和指导集成电路发展的摩尔定律逐渐失效,将使数据中心发展受限于数据传输带宽和功耗问题。解决这些问题最可行的方案是将目前电开关所承载的大流量部分转移到光路交换上来。用于数据中心内部网络的光交换机必须具有大端口数以及快速交换能力,以从电开关卸载尽可能多的流量到光开关并减小数据交换成本[2-3]。光交换机的数据格式应透明,以适应未来数据速率和调制格式的多样化。此外,目前超级计算机采用并行多核处理器结构,其计算性能取决于处理器性能和处理器之间的数据交互能力这两个因素。由于电子技术在传输和交换上面临的瓶颈,采用光互连和光交换以提升处理器之间的数据交互能力是超级计算机的发展趋势。因此,在计算机通信网系统中,也需要实现快速光交换。

高速光开关芯片和模块是光交换系统中最基本和最核心的部件,其重要性等同于电子设备中的处理器。未来全光交换要满足高速大容量和低时延交换的要求,大端口和快速切换的光开关芯片必不可少。采用分立光开关器件实现光交换的方式在插损、体积、功耗和可靠性等方面存在诸多问题,不具备商用化应用的前景。光子集成技术能够大幅度减小系统体积、降低耗能和节约成本,因此全光交换网络中使用的大规模光开关非常适合采用光子集成技术来实现。研究结果表明,采用光子集成芯片的光子路由器,其功耗、体积和重量均可以降至分立光开关器件的1‰以下。

硅基光电子技术因其独特优势,具备实现大容量、低延时、多端口、低功耗以及快速切换的大规模开关芯片的前景。首先,硅基光波导结构具有高折射率差,这意味着波导弯曲半径更小,器件能做得更紧凑,有利于实现大规模集成;其次,尽管硅材料不具有线性电光效应,但通过载流子色散效应,可实现高速的电光调制,使得纳秒量级的快速光路切换成为可能;最后,硅基光电子技术因为其与互补型金属-氧化物-半导体(Complementary metal-Oxide-Semiconductor, CMOS)工艺的兼容性,具有实现低功耗和低成本光开关芯片的技术前景。

1 光开关集成平台

光开关阵列是光交换的核心,其基本功能是实现光信号在不同光路上的快速交换。对光开关的基本要求是插入损耗小、串扰低、扩展性好、结构紧凑、适于批量生产、操作方便、可靠性好和寿命长。不同的应用场合对各种参数的要求有所不同。

光开关最常用的实现方式包括采用微机电系统(Micro-Electro-Mechanical System , MEMS)、二氧化硅(SiO2)平面光路(Planar Lightwave Circuit, PLC)、III-V族材料以及硅基光电子集成等。MEMS光开关阵列通常利用静电力作用产生机械运动改变镜子的方向,从而改变光路。MEMS光交换具有低损耗、低串扰、偏振无关等优点[4-6]。目前实验室报道的基于MEMS技术的光开关最大端口数超过了1 100个,平均光纤到光纤插入损耗为2.1 dB,所有可能的连接最大插入损耗为4.0 dB[6]。MEMS光开关的主要缺点是芯片尺寸大,交换速度慢(毫秒量级),系统庞大稳定性差,需要复杂的控制反馈系统来保持镜子的角度。SiO2 PLC平面波导技术广泛应用于各种无源器件,具有工艺简单和损耗低等优点。SiO2 PLC光开关的缺点是芯片尺寸较大,不太可能继续增大端口数;同时由于SiO2的热光系数较小,交换的功耗较大,交换速度仅为毫秒量级。III-V族半导体材料也是良好的集成光电子材料,可用于实现光开关。III-V族材料的一个优点是可以实现纳秒量级的开关速度。此外,III-V族材料是直接带隙材料,可以实现有源器件(激光器和放大器等),可用于波长转换或补偿光路损耗。但是,基于III-V族材料的光开关功耗都较大,也无法加工大于4英寸的晶圆,不适于大端口数光开关阵列芯片的低成本和规模化生产。由于硅基光电子器件具有尺寸小、集成度高和制作工艺与传统微电子CMOS工艺相兼容的特点,因此可以大幅度降低基于硅基光电子技术的光开关芯片成本。硅基光开关是近年来国际上的热门研究领域。铌酸锂材料是一种用于制作高速调制器的常见材料,它也能用于制作光开关,但是尺寸过大,不能高密度集成[7-8]。聚合物材料能制作柔性光开关,可用于可穿戴设备上,但同样由于波导尺寸过大,大规模扩展性较差[9-10]。

光开关的种类和实现方式很多,下面就简单介绍几种基于常见材料的光开关芯片的技术进展。

1.1 SiO2材料

SiO2 PLC平面波导技术主要应用场景是在无源器件方面,该技术在光分路器、光合路器[11- 12]以及阵列波导光栅(Arrayed Waveguide Grating, AWG)[13]中广泛应用。PLC集成光子技术具有制作简单、插入损耗低、偏振不敏感、稳定性好、易于连接光纤和适宜批量生产等优点。作为光开关的实现技术,它依赖于热光效应,可通过马赫-增德尔干涉仪(Mach-Zehnder Interferometer, MZI)结构实现多端口光开关[14-19]。

用于制作SiO2 PLC光开关的波导折射率对比度通常为0.75%或1.5%,其中0.75%折射率对比度波导具有低传播损耗和低光纤耦合损耗,而1.5%折射率对比度波导具有更小的弯曲半径(2 mm),能实现更紧凑和更大规模的PLC光开关。

构建大容量光交换系统时,低成本和大规模开发光开关的一个关键问题是降低功耗。PLC波导热光移相器所消耗的功耗最终限制了开关规模。降低功耗的一个办法是在波导周围制作空气隔热槽,使波导芯层可以有效地被加热同时又抑制热量向周围传播。对于折射率对比度为1.5%的SiO2波导,当下包层厚度为50 μm,包层脊宽度为20 μm时,MZI开关切换功耗为45 mW,仅为使用常规SiO2波导开关切换功耗的1/10左右[18],响应时间也能<3 ms。

当光开关达到一定规模后,需要单独控制的开关单元数目非常庞大。为了实现简单的开光调控,可以将热光移相器驱动电芯片、光开关芯片以及控制和电源终端封装在一起[20]。将集成电路芯片安装在PLC芯片表面,不需要将电路布线延伸到PLC芯片端面,因而减少了电路走线所需要的空间,同时PLC芯片端面焊盘数量可以减少,使封装变得更简化,降低了模块组装成本。

至今报道的基于SiO2 PLC光开关的最大端口数为32×32[16]。该光开关采用压缩路径无关插损(Path-Independent-Insertion-Loss, PILOSS)拓扑结构和柔性印刷电路板技术,大大减少了光波导区域和所需的布线空间,并且容易将光开关芯片和热调驱动电路封装在一个模块内。该光开关芯片插入损耗为6.6 dB,消光比为55 dB,响应时间为0.7 ms,能用于可重构光分插复用器和波长粒度的光路交换系统中。

早期SiO2 PLC波导具有较小的折射率对比度,因而PLC芯片尺寸较大。Furukawa公司近年来开发了一种基于二氧化锆-二氧化硅(ZrO2-SiO2)的高折射率波导材料的PLC技术[21],利用这种技术实现的波导具有5%以上的折射率对比度,远远超过了传统PLC,因而芯片具有更小的尺寸。ZrO2-SiO2 PLC的基本光学特性与传统PLC相当,利用热光效应可以实现多种光开关[22-24]。

SiO2 PLC技术经过二十多年发展,已经非常成熟,它具有损耗低和串扰小的优点,但是芯片尺寸相比于其他材料制作的芯片仍然过大,功耗也很高,响应比较慢。虽然SiO2 PLC光开关还在不断发展,但受限于材料属性,很难满足未来对小型化光开关芯片的需求。

1.2 III-V族材料

Ⅲ-Ⅴ族半导体材料(如磷化铟(InP)基材料)也是良好的集成光电子材料,可以用来实现具有纳秒量级切换时间的电光开关[25-29]。Ⅲ-Ⅴ材料是直接带隙材料,可以实现多种有源器件,如激光器、放大器和探测器等,是良好的集成光子材料。采用Ⅲ-Ⅴ族材料可以实现波长变换或补偿光传输过程中的损耗,能给光开关芯片提供额外功能,而且Ⅲ-Ⅴ族材料具有良好的线性电光效应,能实现高速的电光调制,这意味着其可以实现纳秒量级以下的光交换。但是,基于Ⅲ-Ⅴ族材料的光开关功耗都比较大,而且Ⅲ-Ⅴ族工艺加工大于4寸的晶圆比较困难,不容易实现大规模低成本集成。

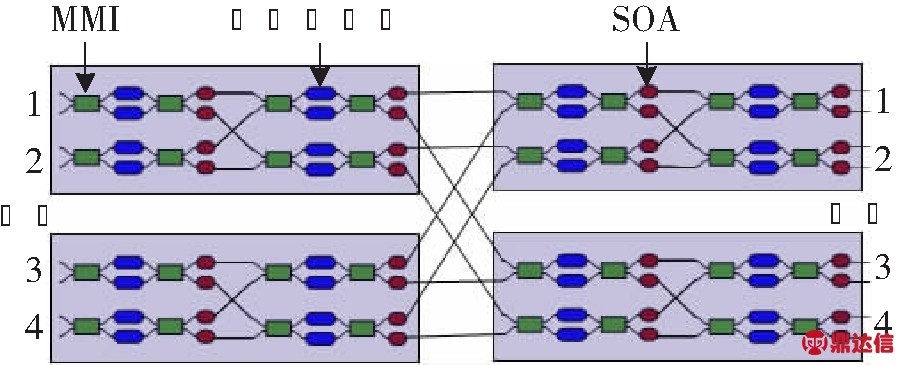

基于III-V族半导体光放大器(Semiconductor Optical Amplifier, SOA)的光开关通常基于广播和选择(Broadcast-and-Select, B&S)或者切换和选择(Switch-and-Select,S&S)拓扑结构[29-30]。光路S&S部分可以通过级联MZI实现。SOA放置于MZI之后用于提供增益或衰减。SOA在关闭状态下具有很大损耗,能吸收串扰光信号,提高光开关的消光比;而它在开启状态下能提供增益,可用于补偿分路/合路器以及无源波导的损耗。随着光开关阵列规模增大,每条光路上分路/合路器的数量和无源波导的总长度不断增加,这就需要更大增益量的SOA来补偿增长的损耗。但是,这会引入放大器自发辐射噪声(Amplifier Spontaneous Emission noise,ASE),引起信号失真,并增加光开关功率预算。如图1所示为一个基于MZI-SOA的2×2光开关单元结构[28],MZI的两个输出都连接到SOA,信号输出端口SOA打开以补偿无源器件损耗,另一个输出端口的SOA处于关闭状态以抑制串扰。基于该MZI光开关并采用扩展Benes拓扑结构可以进一步减少串扰[25]。图2所示为一个采用扩展Benes结构的4×4光开关,它包括4个2×2扩展Benes开关单元,每个单元由4个MZI和8个SOA构成。虽然该2×2开关单元具有4个输入和4个输出,但外部输入和输出只用到了两个端口。MZI两臂上的相位调制器采用量子限制斯塔克效应(Quantum-Confined Stark Effect, QCSE),与载流子注入移相器相比,QCSE移相器通过改变施加的电压来实现开关切换,因而无静态功耗。

图1 基于MZI-SOA的2×2光开关单元[28]

图2 采用扩展Benes结构的4×4光开关[25]

除了MZI结构之外,基于有源-无源集成的InP平台也可以采用微环谐振器(Microring Resonator, MRR)来形成开关矩阵[31]。 由于单微环开关存在带宽和消光比之间的权衡,一般采用多个微环级联来提高带宽和开关消光比。为了补偿损耗,在微环开关阵列前面或者后面可集成SOA。

由于InP基SOA可以用作波长变换器,利用它再结合AWG能实现波长路由光开关[32]。加州大学圣芭芭拉分校实现了8×8单片集成可调光路由器芯片,它包括了1个无源AWG和8个基于SOA的波长变换器。该开关的原理是利用波长变换将信号光波长转变为AWG路由波长,然后经过无源AWG传输到特定端口。该开关芯片的尺寸为4.25 mm×14.5 mm,能对40 Gbit/s数据进行路由,每一路的功耗为2 W。

基于III-V材料的集成光子技术能有效地实现纳秒量级的开关芯片。由于III-V材料可以实现增益能有效补偿无源损耗,因而开关阵列的总体插损可以做到很低。但由于III-V材料加工工艺比较复杂昂贵,光开关成本较高,对于大规模集成多端口开关芯片,成品率也是潜在问题。

1.3 绝缘体上硅材料

硅基光电子器件能采用CMOS兼容工艺制备,具备能与微电子器件单片集成的潜力,保证了硅基光子器件具有相对低廉的价格和广阔的市场。如今,硅基光子学已经成为集成光子学领域诸如高性能计算、光通信(电信∕数据)、光学传感器、片上光互连、微波光子和激光雷达等领域的领先技术解决方案[33-37]。而近几年重要的硅光子学公司的收购事件也表明了在未来几年商业化的良好前景。国内外均有许多研究团队着手开展关于硅基光开关器件及应用方面的研究,推动了集成光开关朝实用化方向的发展。

哥伦比亚大学一直致力于硅基微环光开关的研究和系统应用。2014年他们实现了一个基于硅基MRR的4×4热光开关[38],该光开关尺寸为0.07 mm2,芯片带宽>38.5 GHz,消光比高于20 dB;2016年他们又用MRR实现了1×8光开关,通过光纤连接搭建了8×8无阻塞光交换[39];2017年他们通过软件定义的控制方式使用1×8 微环光开关分别实现了波长选择性的单播与多播数据传输[40],以及基于空间和波长路由的超通道光交换[41]。

IBM的研究团队也一直致力于开发基于MZI的电光开关[42]工艺,实现基于IBM的90 nm CMOS工艺线。2×2 MZI光开关采用推挽式驱动,在O波段的45 nm光学带宽内,插入损耗约为1 dB,光学串扰<-23 dB,单元响应时间为4 ns,电光移相器平均功耗为1 mW[43]。单片无阻塞4×4 MZI光开关也采用了同样的90 nm工艺,将CMOS逻辑、开关驱动以及光器件都集成在了同一芯片上[44]。光开关片上插入损耗为1.5~3.0 dB,串扰<-23 dB。CMOS开关和驱动均集成在了同一芯片上,简化了组装并降低了系统成本。

加州大学伯克利分校研究小组在硅基光开关的研究上另辟蹊径,提出了一种将硅基光电子技术和MEMS技术相结合的新型光开关,开关状态可以通过MEMS操控波导的微小移动来实现。2015年他们报道了一种基于50×50交叉开关矩阵的光开关[45],在9 mm × 9 mm的芯片上集成了2 500个开关单元。在每一个开关单元内都有一对单臂波导可移动的定向耦合器(Directional Coupler, DC),通过MEMS技术控制DC两根波导的垂直距离来控制光路,进而决定开关单元的状态。开关单元在状态切换时的电压为14 V,消光比为26 dB,开关时间为2.5 μs。器件的传输损耗主要来自于波导交叉,最长路径的片上损耗为27.5 dB。2016年他们又报道了另外一种具有更高性能的64×64光开关[46],图3所示为采用MEMS驱动的硅基大规模光开关。开关单元的响应时间为0.91 μs,消光比超过了60 dB;而整个芯片尺寸为8.6 mm×8.6 mm,在300 nm带宽(1 400~1 700 nm)范围的片上损耗仅为3.7 dB。该开关的最大问题是驱动电压非常高,开启和关闭对应的电压分别为42 V和24 V。

图3 采用MEMS驱动的硅基大规模光开关[46]

日本先进工业科技研究所(The National Institute of Advanced Industrial Science and Technology,AIST)实现了基于PILOSS拓扑结构的8×8 热光光开关[47],共有64个开关单元和49个波导交叉节点。开关单元基于热光效应,采用双臂集成了氮化钛(TiN)的MZI结构,器件的平均片上损耗为6.5 dB,在以1 550 nm波长为中心的7.5 nm 带宽范围串扰均<-20 dB,并成功传输了43 Gbit/s 的正交相移键控(Quadrature Phase Shift Keying,QPSK)信号。随后利用同样的拓扑结构和优化的MZI单元结构又设计了32×32的光开关芯片[48],芯片大小为11 mm×25 mm,共有1 024个开关单元和961个交叉节点。为了保持工艺的均衡性,芯片的制作采用先进的氟化氩(ArF)沉浸式光刻,同时芯片通过倒装焊的方式进行封装。器件的平均片上损耗为15.8 dB,在以1 545 nm波长为中心的1.8 nm带宽范围内串扰均< -20 dB,平均功耗为2.93 W,开关时间<30 μs。

中科院半导体研究所近年来也致力于大规模光开关的研究,在2015年报道了基于MZI单元结构的8×8电光开关[49],开关单元集成了一对PIN结,开关时间为1 ns。器件采用Benes的拓扑结构,在全直通状态下的消光比为13.3 ~ 19.0 dB。在2016年报道了同样基于MZI的16×16电光开关[50],并对MZI单元结构采用push-pull的电压驱动方式来降低驱动电压,借此来降低串扰使得开关性能得到提高。器件采用180 nm 的CMOS工艺,尺寸为8.35 mm×2.46 mm,光开关的消光比为17.9 dB。之后他们将电光开关芯片扩展到了32×32规模[51]。为了方便找到开关状态并测试,分别在第5级和第6级增加了功率检测点。开关的串扰为 -15.1 ~ -24.8 dB,片上插入损耗为 12.9~18.5 dB。光开关在片上光网络路由方面也有较大进展,利用微环和MZI结构实现了多种片上光路由芯片[52-55]。

我们课题组在硅基光开关单元和集成芯片方面也做了大量研究,采用了多种不同设计方案,它们各有优缺点,需要考虑实际应用场合来做选择[56-65]。

以MMI为基础的广义马赫-曾德尔干涉仪(General Mach-Zehnder Interferometer, GMZI)结构可以用于构建大规模光开关。N×N GMZI结构通常由两个N×N耦合器通过中间N条波导连接构成。2×2 MZI是最简单的GMZI结构。GMZI可以用于实现1×N、N×N光开关。相比于2×2 MZI通过不同拓扑结构级联实现N×N光开关阵列芯片,基于GMZI结构的光开关具有结构简单和尺寸较小的优点。对于由两个N×N MMI级联构成的N×N GMZI光开关,一共只有N种不同的开关状态。因此,单个N×N GMZI光开关都是阻塞型光开关。通过几个N×N GMZI以一定的方式级联就可以实现无阻塞开关。该结构的优点是结构简单、开关单元数目少和不需要波导交叉结。一种对称型4×4无阻塞光开关结构可以由1个4×4 GMZI光开关在输入和输出端再各级联两个2×2 MZI光开关单元构成[64]。实现上述4×4无阻塞开关只需要4个有源的开关单元。4×4无阻塞光开关中每条开关路径都通过两个4×4 MMI耦合器和4个2×2 MMI耦合器,因此插入损耗与路径无关。另外一种拓展结构是在4×4 GMZI之后顺序级联1个3×3 GMZI和1个2×2 GMZI构成一个插损与路径有关的非对称结构[60]。

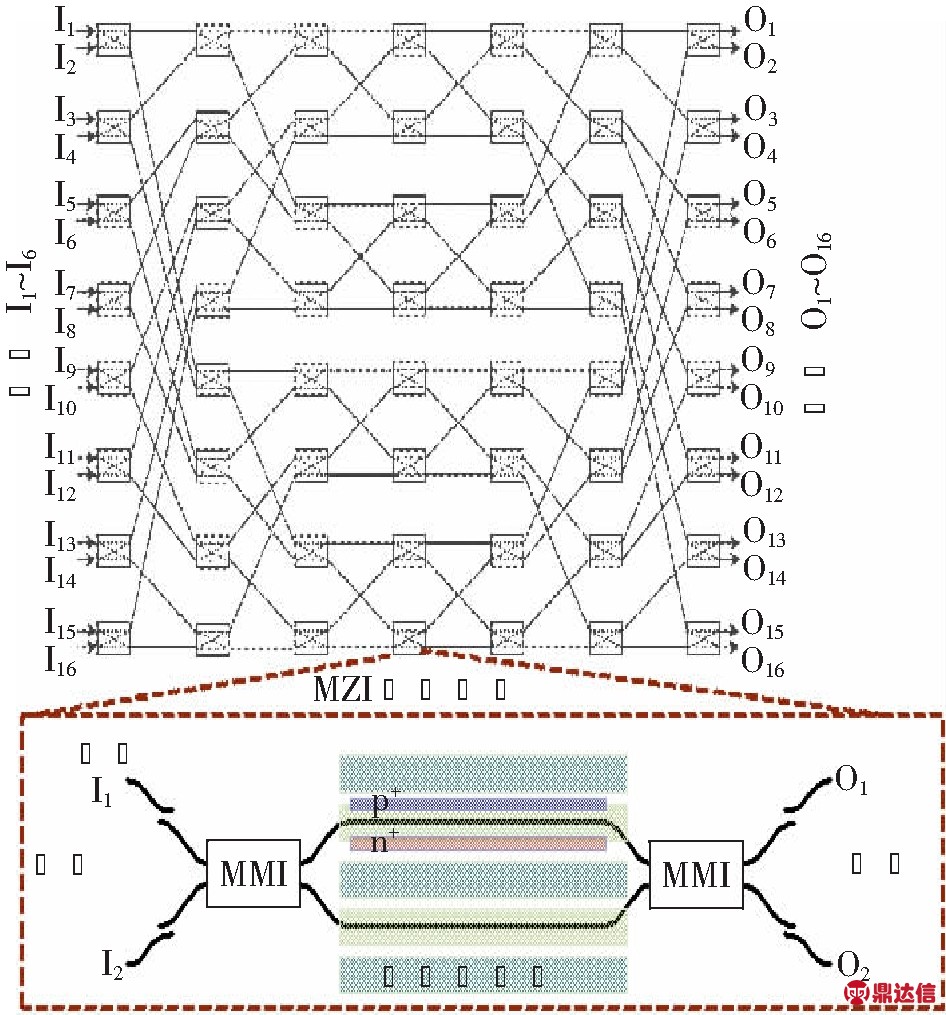

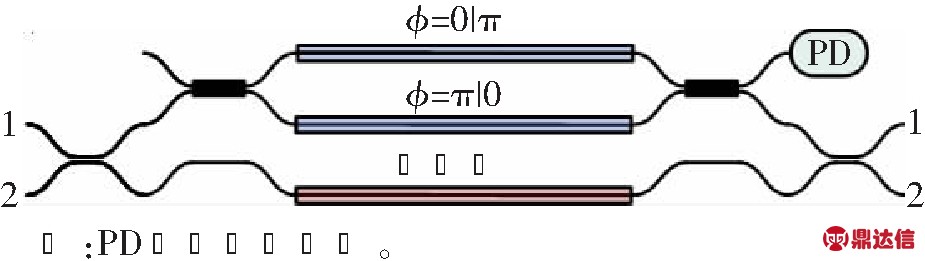

虽然Benes拓扑结构不是严格无阻塞,但Benes是实现无阻塞交换所需开关单元最少的拓扑结构。开关单元少意味着较小的片上插入损耗、较小的芯片尺寸以及较少的驱动电极。实现16×16无阻塞光开关一共需要7级开关,每一级上都有8个2×2开关单元,因此,一共需要56个2×2 开关单元来实现16×16无阻塞开关阵列,图4所示为16×16 MZI电光开关整体及单元结构示意图[59]。2×2 MZI开关单元由两个2×2 MMI耦合器和两个等长的波导臂构成。上臂集成了PIN二极管,用于实现开关状态的高速调节,同时两个臂上还分别集成了TiN热电阻,用于补偿工艺误差导致的初始相位偏差。开关单元前后光路中都通过DC分出一小部分光(分光损耗为0.4 dB),用于监控每一个开关单元的状态。在全交叉状态,片上平均插入损耗为6.7 dB,所有16个输出端口的串扰都<-30 dB,在30 nm波长范围内,串扰也都<-20 dB。在全直通状态下,由于自由载流子吸收引入了额外的损耗,平均片上插入损耗相比于全交叉状态增加到了13.9 dB。MZI开关动态路由响应测试表明光路切换时间可以达到纳秒量级。

图4 16×16 MZI电光开关整体及单元结构示意图

硅基高速光开关采用载流子注入技术,但载流子注入后也伴随产生热光效应。为了减小热光效应影响,MZI光开关可以采取同步驱动方案,即当载流子注入到MZI的一个臂的同时将调制电压施加到另一个臂上的热光移相器,以此抵消热光效应的影响[66]。

开关单元中如采用双微环辅助MZI电光开关来替代MZI电光开关,可以大幅减小开关调节功耗[56]。由于微环是谐振结构,对环境温度变化很敏感,因此在实际应用中可以采用片上光功率监控,通过控制电路来跟踪和锁定微环的谐振波长[67-69]。

除了学术界,企业界也积极开展硅基光开关研究。华为公司在2016年报道了32×32光开关[70],拓扑结构采用扩展Benes结构。由于常规Benes结构不可避免会产生一级串扰,因此他们在Benes结构的基础上增加更多的开关单元来消除一级串扰,从而降低开关整体串扰值。该芯片共有448个2×2 热光MZI单元,在每个单元上都增加了监控光电二极管来确定单元的状态。

2 硅基光开关关键技术

2.1 基本元件

2.1.1 硅波导

大规模光开关包含了大量比较长的连接波导,为了减小开关插入损耗,首先需要减小波导的传输损耗。硅波导由于其高折射率对比度,损耗主要来自于波导侧壁粗糙度引入的散射损耗。使用多模宽波导可以减小波导侧壁处的模场强度,从而减小散射损耗。采用这种方法在没有经过后端工艺的无源器件上可以实现非常低的损耗,但经过后端工艺(包括离子注入掺杂、探测器制作和金属化工艺等)会增加波导额外损耗[71]。此外,采用超薄60 nm厚度硅波导,可以将损耗降低至0.6 dB/cm,与常规硅波导相比提高了5倍[72]。浅刻蚀脊型硅波导由于其光学模式和侧壁交叠较少,因而具有较低的传输损耗。横截面为0.25 μm(高度)×2 μm(宽度)和0.05 μm蚀刻深度的硅波导在C波段中具有0.27 dB/cm的传输损耗[73]。

2.1.2 光开关单元

(1) MZI结构

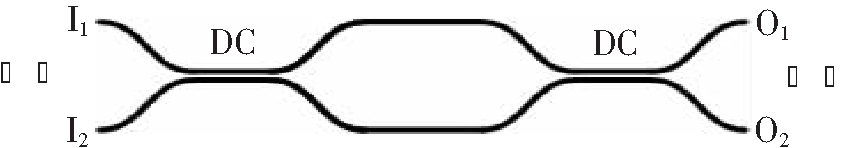

MZI是一种广泛应用于硅基光电子芯片的单元结构,也是一种常见的光开关单元结构[58-59, 62]。用于光开关基本单元的MZI通常为2×2的4端口MZI。如图5和6所示,2×2 MZI结构由3个部分组成,分别为位于左右两侧的两个3 dB耦合器和位于中间的两段长直波导(相位调制臂)。3 dB耦合器可以是2×2 MMI,也可以是DC。相对于DC,MMI具有高带宽和工艺容差大等优点,因此MZI更多地采用MMI结构作为3 dB耦合器。

图5 以MMI为3 dB耦合器的MZI结构示意图

图6 以DC为3 dB耦合器的MZI结构示意图

在理想情况下,因为光场在MZI两臂中经过的路径相同,在直波导中传播而引入的相位变化相同,则上下两臂之间的相位差为0。当两臂之间相位差为0时,MZI开关单元的工作状态为交叉状态,光的路由路径为I1-O2和I2-O1。若通过移相器来改变两臂之间的相位差使其为π,则MZI开关单元的工作状态从交叉状态切换为直通状态。在直通状态下,光的路由路径为I1-O1和I2-O2。

对于2×2 MZI开关单元,如果3 dB耦合器不能很好地实现均匀分光,则会导致在两输出端口产生较大的串扰。此外,上下两臂之间损耗的不均匀性也会导致串扰增加。上下两臂之间损耗的不均匀性主要来源于两个方面:一个是器件加工工艺本身可能会导致两臂有差异;另一个是单臂电光调制的MZI其调制臂会有自由载流子吸收损耗。MZI开关单元的优点在于其频谱响应较宽,缺点在于调制臂较长,通常需要数百微米以获得π相移。

(2) 波长不敏感MZI结构

降低3 dB耦合器的波长灵敏度可以进一步提高MZI光开关的光学带宽。这可以通过减小DC中波导间距来实现,然而波导间距减小则要求更精确的制备工艺。采用MMI来替代DC也可以减小波长灵敏度,但是MMI中波导与多模干涉区域的过渡无法避免会引起额外损耗。

图7所示为一种波长不敏感的MZI光开关结构,它的3 dB耦合器由具有中间相位延迟的两段式DC构成[74]。两段式耦合器实质上就是一个小型MZI结构,包括一个功率耦合系数为κ1的输入DC,两个相位差为δφ的干涉臂以及1个功率耦合系数为κ2的输出DC。该两段式DC结构可以采用对称式设计,让前后耦合器耦合系数相同,即κ1= κ2= 0.5,同时两个臂的光程差为1/4波长。与使用不同耦合系数的不对称设计相比,这种对称性设计具有更高的工艺容差[43]。

图7 波长不敏感MZI光开关结构示意图[74]

(3) 单臂嵌套型MZI结构

硅材料中的自由载流子色散(Free Carrier Dispersion, FCD)效应通常用于实现高速、低功耗和小型化电光移相器。对于光开关应用,移相器的结构通常是基于载流子注入的PIN二极管。这种移相器虽然相位调节效率非常高,但由于自由载流子吸收(Free Carrier Absorption, FCA)效应,载流子注入后会增加光学损耗。对于2×2 MZI光开关,PIN二极管打开后的直通状态下光学损耗问题比较严重,因为FCA引起的损耗使得MZI两臂之间出现了功率不平衡,导致光泄漏到交叉端,同时还增加了光开关的插入损耗。采用推挽式驱动可以减小FCA的影响,但能获得的最佳串扰值有限[43]。

采用嵌套型MZI结构可以改善FCA带来的两臂功率不均衡问题,单臂嵌套型MZI光开光结构如图8所示[75]。该结构实际上就是将MZI开关单元的一条波导臂上的电光移相器用另一个推挽式驱动的MZI移相器来代替。为了在一条干涉臂上产生所需的π相位以此改变光开关状态,MZI移相器需要工作在最大传输功率点,它的两个臂上相位分别从0~π以及π~0变化。在这种工作模式下,MZI移相器的输出端能产生精确的π相移,而且0和π相移状态下损耗相同。通过调节MZI光开关下臂的衰减器,可以使开关两臂具有相同的光功率,达到完全平衡干涉,因而能大幅度抑制功率不均衡所引起的串扰。

图8 单臂嵌套型MZI光开关结构示意图[76]

(4) 双臂平衡嵌套型MZI结构

上述单臂嵌套MZI光开关可进一步拓展为双臂平衡嵌套型MZI光开关,如图9所示。该光开关包括1个输入2×2耦合器,1个输出2×2耦合器以及两个由2×2 MZI嵌套构成的干涉臂。每个嵌套的MZI具有两个相同的载流子注入移相器。该光开关具有平衡结构,其中两个主干涉臂的光程等长,可以实现宽带光交换。

图9 双臂平衡嵌套型MZI光开关结构示意图

当移相器1和4相位为0而移相器2和3相位为π时,嵌套的MZI A将来自端口b的光信号传输到端口d,相位增量为π,而嵌套的MZI B将来自端口a'的光信号传输到端口c',相位增量也为π。因此,此光开关工作在交叉状态。由于平衡相位调节下两个嵌套的MZI插入损耗相等,因此光开关两干涉臂具有相等光功率,实现了平衡干涉,在直通端口处无串扰。

在开关另一个工作状态下,移相器1和3相位为π,而移相器2和4相位为0,此时嵌套的MZI A将光信号从端口b传输到端口d,相位增量为0,而嵌套的MZI B将光信号从端口a'传输到c',相位增量为π。因此光开关工作状态为直通状态。两个嵌套的MZI插入损耗在这种相位调节下也是相等的,因此该状态下光开关理论上也无串扰。

(5) 可调分光MZI结构

对于MZI光开关,如果前后两个耦合器具有相等的分光比,两个臂的相位差为π的话,光能完全传输到直通端,交叉端理论上无任何串扰;而如果两个臂的相位差为0的话,光是否能完全传输到交叉端取决于两个耦合器的分光比,只有在严格3 dB耦合比下,才能获得完全传输,直通端无串扰。这在实际情况下很难满足,而且工艺容错性也较低。

通过采用可调分光MZI结构可以在两种状态下都获得极小的光串扰,如图10所示[76]。该结构与传统的2×2 MZI光开关相同,只是前面的3 dB耦合器被另一个MZI所取代。增加的MZI用作可调分光器,其分光比可以根据后面3 dB耦合器的实际分光比做相应调节,以获得最大开关消光比。这种结构可以减小串扰,但增加了可调元件数目和光路损耗。

图10 可调分光MZI结构示意图[76]

(6) 级联MZI结构

图11 级联MZI光开关单元结构示意图[78]

级联MZI光开关单元由两个具有半波长长度差的非对称MZI以及1个交叉点构成,如图11所示[77-78]。该光开关单元适用于基于交叉矩阵拓扑结构的光开关中。MZI两臂的初始相位差为π,因此开关单元初始状态为直通状态(OFF状态);当MZI上的移相器提供π相移时,光开关处于交叉状态(ON状态)。在OFF状态下,输入端口1连通到输出端口2′,输入端口2连通到输出端口1′;在ON状态下,输入端口1连通到空闲端口(在交叉矩阵开关中没有用到该路径),输入端口2通过两个级联的MZI连通到输出端口2′。

在这两个非对称MZI开关单元中,OFF状态下泄漏到交叉端口的光是串扰的主要来源。ON状态下泄漏到直通端口的光最终传输到矩阵开关的空闲口,不会增加开关输出端的串扰;但是在OFF状态下泄漏到交叉端口的光最终传输到了矩阵开关的输出口。在级联MZI光开关结构中,来自MZI A的泄漏光被MZI B所阻挡,因此在OFF状态下串扰光功率大大降低了。因此,这种光开关的消光比远高于普通单个光开关。

(7) MRR结构

MRR结构在集成光子器件中有广泛的应用[61, 79-81]。图12(a)所示为常见的与两条波导耦合的MRR结构,它的特点是输入光、透射光和反射光端口没有重叠因而便于控制光的传输。相对于MZI开关,MRR结构简单紧凑,因而可构建更小尺寸的开关矩阵芯片。

MRR开关因其谐振特性而具有波长选择性,单个MRR的谐振谱线呈洛伦兹曲线,也因此导致工作带宽较低。MRR开关所需的相移量比MZI更小,因此功耗更低。MRR工作原理如图12(b)所示,初始状态下,如果光波长处于谐振波长λp上,从I1端口输入的光会从O1端口输出。如果对MRR调相改变其折射率使得谐振波长蓝移,则λp波长的输入光会从I1端口传输到O2端口。通过这种方式就实现了输入光在两个输出端口之间的切换。为了增加工作带宽,可以采用级联MRR,让每个微环的谐振波长对准同一波长,开关状态切换时让它们一起调谐。

图12 MRR光开关

(8) 双微环辅助MZI结构

双微环辅助马赫-曾德尔 (Dual-ring assisted MZI, DR-MZI)光开关结构结合了MRR和MZI的特点,能在较小尺寸上实现低功耗、低串扰和高消光比光交换[56, 63, 65]。2×2 DR-MZI结构如图13(a)所示,在一个较短MZI的两个臂上分别耦合有一个MRR。

传统MZI光开关单元为了在调制臂上引入π相移来实现开关状态的切换,需要数百微米长的臂长,导致开关单元的尺寸不够紧凑且所需功耗较高。为了减少调制所需的相移量从而减少功耗,可以采用慢光结构来替代MZI中较长的调制臂。波导中的相移与其群折射率直接相关。因此,如果慢光结构能引入较大的群折射率改变量,实现π相移量所需的调制臂,臂长就可以很大程度缩短。慢光结构多种多样,例如:布拉格光栅、光子晶体和MRR等。MRR由于其结构简单以及易于加工等优点,可以更方便地与MZI结合。

图13 DR-MZI光开关结构及工作原理示意图

与单波导耦合的MRR处于过耦合状态时,在其谐振波长附近,耦合波导的相位响应变化剧烈。DR-MZI结构所使用的MRR需要工作于过耦合状态,图13(b)描述了DR-MZI开关单元的工作原理。初始状态下,两个完全相同的MRR的谐振波长重叠,因而它们耦合波导的相位响应也完全一致。由于上下两个调制臂的相位差为0,基于MZI的干涉原理,此时该开关单元工作于交叉状态。由于MRR处于过耦合,MZI上下两臂的相位响应在MRR的谐振波长附近从0~2π剧烈变化。如果在其中一个MRR中采用电光调制引入较小的相移使其谐振波长蓝移,就可以在上下两臂之间引入π相位差,从而将DR-MZI开关单元的工作状态切换到直通状态。工作波长可以选在两个MRR谐振峰的中间点,工作带宽由两个MRR的耦合强度决定。

2.1.3 移相器

光开关对输入光信号进行路由,这个过程需要通过移相器调节相位来完成。硅波导移相器根据其工作原理主要分为基于热光效应的热光移相器和基于等离子体色散效应的电光移相器两种。

由于硅材料具有很大的热光系数,在1 550 nm波长附近为1.86×10-4K-1,因此热光移相器具有很好的相位调节效率。热光移相器结构简单,易于实现且稳定性较高。常用的结构一种是在波导包层之上加一层金属电阻(如TiN),对金属电阻进行加热,热量传导到波导上改变波导的温度,从而实现折射率调节。但是,由于SiO2的热传导系数很小,金属电阻上的热量传导到硅波导上较慢,并且有不少热量向上传导损失掉,导致调节功耗较高;另一种是将波导作为微加热器对波导本身进行加热,无掺杂或轻掺杂的波导芯区作为高电阻区,两边的平板区域都进行n++或者p++重掺杂,并通过金属接触形成欧姆连接,为低阻区,这样就在波导上形成了一个热电阻,由于波导芯区电阻较大,加电后热量直接在波导上产生,避免了所需的热量传导过程[81],相比于金属电阻加热,这种方法更为高效,功耗更低,调节速度也更快。虽然波导区两侧进行了掺杂,但在加热过程中波导芯区的载流子浓度增加比较小,所引起的载流子吸收损耗可以忽略不计。

热光移相器的缺点是热光效应的响应时间较长,大都在毫秒量级。此外,功耗较高也是热光移相器的不足之处,当实现光开关多端口大规模集成时,片上功耗过高会产生严重的热串扰现象,因此降低功耗也是热光开关研究的重点。

硅基电光移相器的原理是基于等离子色散效应。在半导体材料中,自由载流子浓度的变化会导致该材料的折射率和吸收系数发生改变。当硅中自由载流子的浓度变化为1018 cm-3时,硅材料折射率的变化大概为 -10-3量级。实现载流子浓度变化所采用的电学结构主要是PIN二极管。当向PIN 二极管加电时,本征区注入大量自由载流子,改变了波导的折射率。电光开关的优势在于开关响应速度快(纳秒量级),而且功耗较小;但是由于自由载流子的吸收,损耗也会增大。

热光和电光移相器各有优缺点:热光移相器结构简单,在相位调节过程中不会影响开关的消光比、串扰和损耗等特性,但是开关速度慢;而电光移相器则相反,反应速度快,但在开关过程中会引入额外的损耗,导致消光比和串扰特性的恶化,采用推挽式电光移相器设计或级联开关单元结构可以弥补这方面的不足。

2.2 集成光开关拓扑结构

影响光开关性能的一个重要因素是光开关矩阵的拓扑结构,多端口光开关基本都由基本开关单元通过一定的拓扑网络相互连接而成。光开关拓扑结构可分为有阻塞和无阻塞两种,无阻塞又分为严格无阻塞、广义无阻塞和可重构无阻塞3种[82]。严格无阻塞交换是指只要连接的起点和终点是空闲的,不管采用哪种算法,任何时刻都可以在交换网络中建立一个连接,而不影响现有已经建立好的光路;广义无阻塞网络是指如果按照某种特定算法建立连接,那么就不会影响到现有的光路;可重构无阻塞是指只要某个连接的起点和终点是空闲的,任何时刻都可以在交换网络中直接或间接对已有的光路重新配置来建立一个新的光路。下面介绍几种硅基光开关中常用的拓扑网络结构。

2.2.1 交叉开关矩阵网络结构

图14 4×4 Crossbar拓扑结构示意图

图14所示为4×4交叉开关矩阵(Crossbar)拓扑结构的示意图。Crossbar结构是一种应用广泛的光开关拓扑结构,该拓扑结构由N行乘以N列个开关单元组成一个N×N端口的开关网络。因此,该开关网络的基本开关单元为N2个。Crossbar结构的阻塞性质为广义无阻塞,由于结构较为简单,因而控制算法也非常简单。Crossbar结构的优点在于其拓扑网络中没有波导交叉,避免了由于波导交叉引起的损耗和串扰。该结构的缺点在于其不同交换路径经过的基本开关单元数量不一致,导致不同路径的损耗差异性很大。在N×N的交换网络中,传输路径中开关单元数量最少为1,最多为2N-1。假设每个开关单元引入的损耗为LSE,则该拓扑结构的路径损耗不均匀性为(2N-2)×LSE。

PILOSS结构是在Crossbar结构的基础上提出的改进型拓扑结构,它可以避免不同交换路径插入损耗的不一致性。PILOSS结构的阻塞性质与Crossbar相同,为广义无阻塞。PILOSS拓扑结构包含有N2个开关单元和N-1个波导交叉结。该结构最大的特点就是连接任意输入输出端口的传输路径都会经过N个开关单元和N-1个波导交叉结。因此,理论上该拓扑结构的路径损耗不均匀性为0。图15所示为4×4 PILOSS拓扑结构的示意图。

图15 4×4 PILOSS拓扑结构示意图

2.2.2 S&S网络结构

图16 4×4 S&S拓扑结构示意图

图16所示为4×4 S&S拓扑结构的示意图,S&S结构的阻塞性质为严格无阻塞。一个N×N的S&S拓扑结构可以拆分为3个部分,分别为输入/输出交换阵列和连接这两个部分的无源交换网路。输入/输出交换阵列由N个1×N二叉树子交换阵列组成,每个1×N二叉树子交换阵列由log2N级1×2基本开关单元组成。因此,S&S拓扑结构也叫二叉树结构。中间的无源交换网络由波导和波导交叉结组成。该结构共有2N×(N-1)个1×2开关单元,每条传输路径均会经过2log2N个开关单元。S&S拓扑结构存在的最大问题是其中间连接输入和输出阵列的无源交换网络需要大量的波导交叉结导致片上插入损耗增加,而且不同交换路径波导交叉结数量不同,引起过大的损耗不均匀性。其中,传输路径中波导交叉结数量最少为0,最多的则为(N-1)2。

2.2.3 Benes网络结构

图17所示为4×4 Benes拓扑结构示意图,该结构有着广泛应用[83]。Benes结构的阻塞性质为可重构无阻塞。一个N×N端口的Benes结构可以拆分为2log2N-1级开关阵列,每一级由N/2个2×2基本开关单元组成。因此,该结构所需的开关单元数量为(2log2N-1)×N/2。Benes结构是所需开关单元数量最少的无阻塞拓扑结构。在N×N端口的Benes结构交换网络中,每一条传输路径只需经过2log2N-1个开关单元,少于Crossbar和PILOSS结构。因此,Benes结构可以实现比Crossbar和PILOSS结构片上插入损耗更低的光开关芯片。该结构的不足之处在于,其阻塞性质为可重构无阻塞,已建立的端口连接可能会导致闲置端口受到阻塞从而需要复杂的重构算法来连接闲置端口。

图17 4×4 Benes拓扑结构示意图

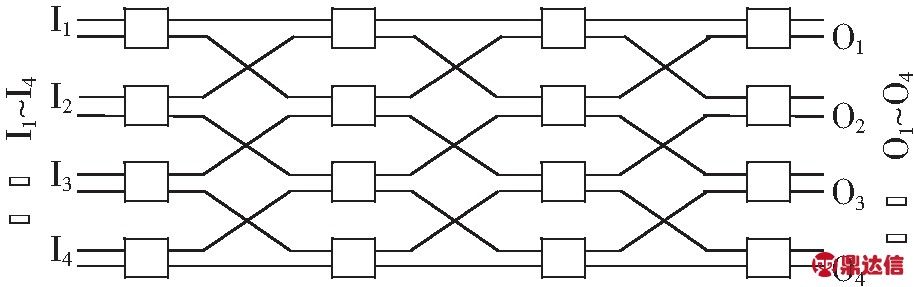

由于Benes结构在信号传输过程中不可避免地会出现一级串扰,扩展Benes结构正是为了解决一级串扰的问题而被广泛研究,8×8扩展Benes拓扑结构如图18所示[83-84]。扩展Benes结构通过增加开关单元的数目来优化开关单元的性能,从而提高整个光开关系统的性能。

图18 8×8 扩展Benes 拓扑结构示意图

2.2.4 双层网络结构

双层网络(Double-Layer-Network,DLN)结构是一种严格无阻塞交换结构,也是一个三级网络结构,输入级和输出级都由N个1×2的交换单元构成,而中间级由4个N/2×N/2的子网络构成。DLN的名字来源于其结构可以分成上下两层,每一层都分别有2级N/2个交换单元和2个N/2×N/2子网络,DLN光开关矩阵拓扑结构如图19所示。N/2×N/2子网络由递归法构成,直到最简单的2×2交换单元。如8×8 DLN结构中的4×4子网络的结构就是4×4 DLN的结构。N×N DLN结构的交换单元数目为5/4×N2-2N。可以看到DLN结构有点类似于S&S结构,只是中间的无源交叉网络换成了子网络,相对于S&S结构,其优点就是波导交叉结更少。因此,DLN可以实现低插入损耗和低串扰的交换矩阵[85]。

图19 DLN光开关矩阵拓扑结构示意图

2.3 偏振相关性问题

由于常规的亚微米尺寸绝缘体上硅(Silicon on Insulator,SOI)波导具有很强的双折射特性,横电场(Transverse Electric,TE)和横磁场(Transverse Magnetic,TM)偏振有效折射率差别很大,因而以此为基础的耦合器和移相器也具有偏振相关性。如何减小器件的偏振依赖性是硅基光开关设计中的难题,解决这个问题可以采用以下不同方法:

(1) 使用截面积更大的硅波导,比如波导高度为1.5 mm的脊型波导,选择适当的波导宽度可以使得TE和TM模式的有效折射率相等[86]。但这种波导的弯曲半径较大,不利于减小芯片尺寸。

(2) 使用偏振多样性设计,即将输入的两个偏振中的一个(通常为TM)通过偏振分束和旋转后变成另外一个偏振(通常为TE),然后再用两个相同开关阵列或一个双向开关阵列完成光路交换,最后再通过偏振旋转和合束变成双偏振输出[87- 88]。

(3) 使用片上偏振控制器,使任何偏振输入光都能调节到片上单一TE或TM偏振[89]。这种根据输入动态调节偏振的方式需要实时监控输入偏振状态,并反馈给偏振调控元件,因而器件更加复杂且增加了功耗。

2.4 开关状态监控和调节

为了获得想要的光开关状态,一般的方法是在芯片校准期间创建一个查找表,建立每个开关单元状态与达到最佳工作点所需控制电压之间的对应关系。这种方法虽然简单直接,但缺乏灵活性和容忍度,因为它无法消除动态温度变化以及元件之间的热串扰带来的影响。更好的方法是采取实时监控并反馈控制每个开关单元的状态,提高芯片工作稳定性[90]。

片上光功率监控方式多种多样,可以采用Ⅲ-Ⅴ族、锗材料或者硅材料本身。由于在硅材料上键合或生长Ⅲ-Ⅴ材料还比较困难,因此目前硅基探测器制作主要采用锗硅材料。锗与硅属于同族元素,且同为间接带隙材料。单晶状态下,锗的能带隙为0.74 eV, 比硅的能带隙小,可以吸收光波长到1.87 μm的近红外光,因而锗探测器在1.55 μm附近具有很高的探测效率。硅衬底的高质量锗层生长是制作高性能锗硅光电探测器的基础。作为同族元素,尽管硅和锗晶体结构相同,但是它们的晶格常数不同,因而在硅衬底上外延生长锗时会有4.2%的错位,这种错位会导致器件在制作工艺上的困难。

除了采用锗硅探测器之外,还可以采用全硅探测器。目前普遍关注的硅波导中近红外光子吸收效应有:表面态吸收(Surface-State Absorption, SSA)效应和缺陷态吸收(Defect-State Absorption, DSA)效应。SSA效应发生在硅材料的表面,且由于表面态缺陷是自然形成的,因而硅材料的表面态能级普遍存在。尽管SSA效应是一种较弱的光电转化效应,但利用这一效应可以制作简单的光电探测器,适用于片上光功率监控。为了增强全硅光电探测器中的SSA效应,一种方法是可以增加表面态与光模场的重叠面积,这需要通过优化器件尺寸来实现。另外一种提高响应度的方法是增加硅波导的表面态,通过提高硅波导表面积来实现。DSA效应是利用硅材料内部的缺陷在价带和导带之间产生中间能级,使电子吸收光子产生跃迁。

基于SSA 和DSA效应,利用交趾型PN结可制作全硅波导探测器,在-10 V反偏电压下探测响应度最高可达40 mA/W,3 dB探测带宽能达到11.5 GHz。除了PN结之外,也可以直接使用PIP或NIN型硅波导电阻作为探测器,结合锁相放大器,探测灵敏度可以达到-40 dBm,动态范围50 dB以上,光功率检测最小驱动电压为5 mV[69]。利用硅波导电阻进行光功率探测,可以在热光移相的同时,同步对波导内的光功率进行实时探测。探测所加载的驱动信号对波导光传输(幅度和相位)的影响基本可忽略,维持了光开关状态的稳定性和可靠性。基于SSA效应,也可以使用非接触式集成光子探头(ContactLess Integrated Photonic Probe, CLIPP),单独实时监控每个开关元件的状态 [91]。光开关监控可以提供光路路由的直接信息,允许各个开关元件的顺序标定和反馈控制,从而使光开关结构在没有温控时对热串扰仍然具有很强的容忍度 [90]。

大规模光开关阵列中由于单元数量非常大,不仅需要均匀稳定的工艺和可靠的封装,还需要校准每个开关,才能得到正确的光路开关。每个开关单元需要增加光功率监控,才能获得初始状态和切换所需的电压。根据开关拓扑结构不同,可以有选择地在某些特定光路上增加监控端口。比如,在Benes结构中,使用少量的片上光功率监控端口就能检测和确定所有光开关单元的最佳工作点[51]。采用这种方法可以减小芯片尺寸,提高单元检测效率。

2.5 光开关封装

大规模光开关除了需要考虑芯片设计和加工外,还需要考虑如何进行大规模光电端口封装。开关芯片的封装包括光学封装和电学封装两个部分。光学封装是连接芯片内波导与外部光纤实现光信号的输入和输出,而电学封装是连接芯片与驱动电路来给芯片内各类热光和电光元件提供直流和高速信号。只有完成封装才能进一步对芯片进行系统测试和应用,封装过程也会给光开关芯片性能指标带来一定程度恶化(如插损增加和开关响应速度变慢等),需要寻找一种方便、高效和经济的封装方式。

2.5.1 光学封装

光在光纤中传播时的模斑大小与硅波导的模斑大小存在严重失配,因此光纤到芯片无法直接耦合。目前光纤-芯片光耦合解决方法主要是水平耦合和垂直耦合。垂直耦合对精准度要求比较低,但光纤位于芯片之上,所占用的空间较大。将光纤端面进行40°角打磨抛光,让光纤中水平入射的光在光纤端面通过全反射以10°倾斜角入射到芯片的光栅中[92],这样光纤可以水平放置,使封装后的模块更加紧凑。这种耦合方式的对精准度能够有5~8 μm的容差[93]。通过水平光纤端面反射进入光栅的方法也可以用在多路的光纤阵列中[94]。光纤阵列中光纤之间间距通常为250或者127 μm,对于具有几十个输入输出光学端口的光开关来说,仍然占用了很大面积。解决这个问题的一种方法是采用二维排布高密度间距减小光纤阵列(Pitch Reducing Optical Fiber Array, PROFA)[95]。对于具有N个光学端口的芯片来说,PROFA所占用的面积与N1/ 2成比例,而线性光纤阵列的长度则与N成比例,而且PROFA中不同光芯间距比光纤阵列更小。这种封装方案对于具有大量光学端口的大规模光子集成芯片特别有吸引力。

在AIST的32× 32光开关芯片中,他们采用了陶瓷转接板和2112引脚0.5 mm间距的栅格阵列(Land Grid Array, LGA)封装以及极高折射率差PLC光纤连接器封装 [96-97],使用金凸块和非导电膏将陶瓷转接板倒装接合到光开关芯片。在PLC连接器中,单模光纤通过热扩张纤芯技术连接到高折射率光纤,然后将高折射率光纤粘合到高折射率差PLC芯片上。PLC波导的模场直径约为3 μm,与硅波导到锥形耦合器出来的光学模斑接近。利用这种光耦合方法可以实现从127~50 μm的波导间距转换。

完成光纤阵列耦合之后,需要对光纤阵列进行固定,可以采用紫外固化胶。在滴胶的过程中需要对光功率进行实时监控,由于经过光开关芯片后往往光功率比较小,不利于耦合对光,因此在设计芯片时需要在片上增加额外的短通光路(输入和输出通过一条U型波导直接连接),这样方便监控光纤和波导耦合的情况。紫外胶在紫外线的照射下会逐渐固化,固化时长与采用的紫外胶材料和照射光功率大小有关。光纤固化应该选取损耗小和折射率与SiO2匹配的紫外胶,以减小端面损耗。

2.5.2 电学封装

硅基单片集成能将驱动电路和光开关做在同一个芯片上,这是硅基光电子的独特优势,也是未来发展的一个重要趋势。IBM在他们报道的单片集成4×4和8×8光开关中,已经将CMOS逻辑电路和开关驱动连同光开关一起集成到了同一个芯片上[42]。由于需要大量开关驱动,他们使用了串/并转换电路和28比特位的移位寄存器。开关驱动是由数字反相器构成,驱动负载是MZI一个臂上集成的正向偏置的PIN结构。AIST采用了基于单片集成金属-氧化物-半导体场效应晶体管(metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)的开关驱动[98],他们采用基于脉宽调制(Pulse Width Modulation, PWM)技术的灰度控制对硅基热光开光进行驱动,实现了不使用数/模转换器(Digital-to-Analog Converter, DAC)和模拟电流驱动器的高效简单的热光调控。MOSFET的栅延时在3.7 ns左右,因此设计的MOSFET的带宽能够达到100 MHz。通过印刷电路板(Printed Circuit Board,PCB)上的通用现场可编程门阵列(Field-Programmable Gate Array,FPGA)芯片生成可变脉冲宽度,实现对加热器平均功率的调节。采用两个具有不同时钟频率的计数器,利用游标效应可以生成高分辨率脉冲[99]。为了加快热光移相器的响应,可以采用“涡轮脉冲”的方式,即在加热起始阶段施加大于目标值的功率,使得硅波导迅速升温;在加热终止阶段,在MZI另外一臂施加小功率,以使两臂间温差迅速变小[100]。

单片集成虽然能有效解决大规模光开关阵列的驱动问题,但是需要考虑光子器件和集成电路的工艺兼容性和流片成本。一种光电集成方式是混合集成,混合集成中也有多种实现方式,其中一种是将光芯片和对应的驱动电芯片采用不同的工艺节点独立制备,然后将两个芯片放置在同一基板上,通过引线键合的方式将两个芯片连接;另一种实现方式是采用芯片到晶圆(Die-to-Wafer,D2W)键合,这种方式还能实现激光器或III-V族材料与硅基光电子器件的结合。前一种方式研究时间较早,操作简单,但电学接口密度受限于金属焊盘在芯片四周分布的数量。在华为的32×32热光开关封装中,他们将光开关芯片引线键合到定制的具有1 560个焊盘和铜钨散热器的陶瓷球栅阵列(Ceramic Ball Grid Array, CBGA)上[70]。带有芯片的CBGA封装使用标准表面贴装技术(Surface Mount Technology,SMT)安装在电路板上。光电混合集成的最新研究集中在后一种D2W的方法上,采用倒装焊或者硅穿孔(Through Silicon Via, TSV)的方式将驱动电芯片直接和光路上的电极相连,将光路与电学走线完全分离。由于电芯片具有5~10层布线层,更容易实现大规模光开关要求的复杂布线[101]。

3 结束语

本文针对光开关芯片面向全光网络中高速、大端口和低功耗的需求,对光开关技术进行了全面的总结和研究。从上述介绍可以看到,相比于其他技术实现光开关阵列集成芯片,采用硅基光电子集成技术实现大容量光开关起步较晚。目前硅基热光驱动和MEMS驱动的开关芯片都已经能达到64×64规模,与其他SiO2和III-V族光开关技术相比,硅基光开关芯片存在尺寸小、功耗低和与CMOS工艺兼容的优点,但同时也存在不少问题,主要有以下几个需要攻克的难点:

(1) 扩大光开关阵列的规模

硅基2×2光开关单元具有较好的性能,但是实际应用中要求的开关阵列端口数较多,损耗和串扰也会在端口数增多时逐渐恶化,这大大限制了光开关芯片规模的进一步拓展;另一方面,光开关阵列规模增大意味着芯片尺寸的增大,这就需要芯片在加工工艺中保持良好的均匀性和可重复性。因此,需要创新设计出性能更好,对工艺容忍度更高的开关单元器件,来优化整体拓扑结构,提高制作工艺精度和稳定性,确保大尺寸芯片中各个单元器件性能的一致性。

(2) 降低硅基光开关芯片的损耗和串扰

硅波导相比于SiO2波导具有更大的传输损耗,也无法制作光放大器对信号进行放大,因此随着交换端口数目的增加,每条光路上经过的单元器件越多,光路损耗就越大。硅基光开关阵列通常采用微环和MZI作为开关单元,尤其采用FCD效应时对光的隔离度较低,因此串扰较大。硅基光开关芯片的损耗和串扰问题会随着端口数目的增加更加凸显,虽然如前文所述可以采用一些特殊设计减小串扰,但也往往会付出单元数增多或损耗增加的代价。

(3) 降低光开关芯片的驱动功耗

功耗问题是光电子芯片往更高集成度和更大尺寸发展需要解决的一个重要问题。当光开关阵列端口数增加后,芯片的总功耗会呈几何增长,不仅对驱动电路提出了更高的挑战,而且会使芯片温度急剧升高,影响光开关的正常工作。低功耗是未来集成光电子发展的必然要求,降低光开关芯片功耗需要从光开关的驱动控制电极着手,实现对光波导的高效调控。

(4) 消除光开关芯片的偏振相关性

目前硅波导器件大多采用220 nm厚SOI晶圆制备,因此光器件大多对偏振比较敏感。硅基光开关芯片一般只支持TE或TM偏振的光信号,而实际光通信系统都希望器件能够交换任意偏振的光。通常实现偏振无关主要是将输入光分为不同偏振的两路分别在两个相同的交换阵列上进行交换处理,交换完后再进行合路输出。这种方法所需芯片面积增加了一倍,驱动控制也较为复杂。因此,未来光开关芯片的发展需要采用更简单和更灵巧的方式来实现偏振无关性。

综上所述,采用传统的硅基光开关方案(如MZI结构或微环结构)和调节方式(热调或注入载流子电调)在损耗、串扰、功耗和偏振相关性等方面已不能满足实际光通信系统对多端口光开关阵列的需求。特别需要指出的是,不管是热调还是电调,都需要消耗很大的功耗来保持某一种开关状态,且开关状态具有易失性(断电后开关状态无法保持),这限制了光开关规模的拓展,降低了它在光通信系统中的实用性。未来可以探索采用相变材料和硅波导相结合的方式来突破目前平面集成光开关在端口数、功耗、易失性和偏振相关性等方面的问题,设计并实现CMOS工艺兼容的具有自保持能力的百端口以上光开关芯片。