摘 要:主要运用Quartus 5.1软件开发平台,利用VHDL语言编程和仿真,基于Altera公司MAXⅡ系列CPLD芯片EPM1270T144C5实现了硬件六十进制压缩BCD码加减运算功能。将设计的CPLD电路应用到光电编码器电路中,实现光电编码器的快速运算,提升了位置检测系统的动态性能指标。详细介绍了电路的原理、设计思路和软件设计,分析了目前设计中的不足之处,提出了部分改进建议。

关键词:FPGA;光电编码器

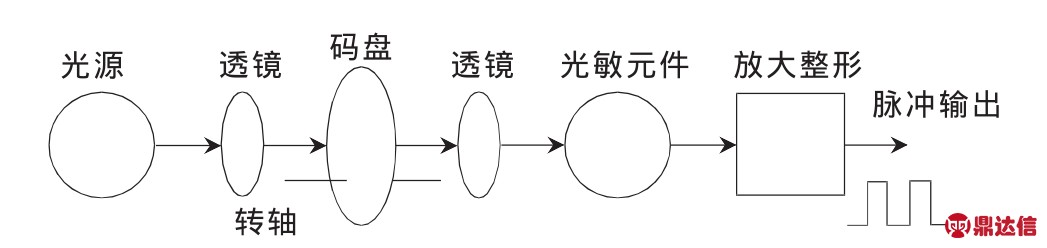

光电编码器是一种通过光电转换将输出轴上的机械几何位移量转换成脉冲或数字量的传感器,是目前应用最多的传感器。光电编码器由光栅盘和光电检测装置组成。光栅盘是在一定直径的圆板上等分地开通若干个长方形孔。由于光电码盘与电动机同轴,电动机旋转时,光栅盘与电动机同速旋转,经发光二极管等电子元件组成的检测装置检测输出若干脉冲信号,其原理示意图如图1所示。通过计算每秒光电编码器输出脉冲的个数就能反映当前电动机的转速。此外,为判断旋转方向,码盘还可提供相位相差90°的两路脉冲信号。根据检测原理,编码器可分为光学式、磁式、感应式和电容式;根据其刻度方法及信号输出形式,可分为增量式、绝对式以及混合式3种。

图1 光电编码器原理示意图

随着电子设计技术的飞速发展,现场可编程逻辑门阵列(FPGA)的复杂程度越来越高,其所具备的功能也越来越多,芯片也向小型化发展,逐步成为复杂数字硬件电路设计的首选。FPGA/CPLD既继承了ASIC的大规模、高集成度、高可靠性的优点,又克服了普通ASIC设计周期长、投资大、灵活性差的缺点。FPGA/CPLD的集成度很高,可完成极其复杂的时序和组合逻辑电路功能。本文所设计的系统就是基于CPLD芯片实现六十进制压缩BCD码加减运算功能。

1 软件设计

1.1 计算原理

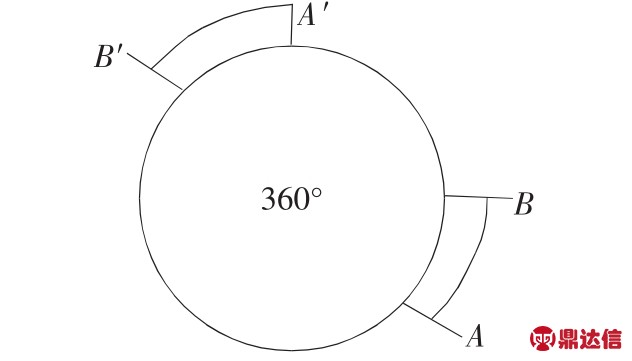

系统主要实现六十进制压缩BCD码的加减运算的算法,即:根据一个度数A的变化量来对另一个度数B实现同样的变化,并输出B变化后的值,从而实现光电编码器的快速运算,提升位置检测系统的动态性能指标。具体如图2所示,即B随A变化而变化,当A变化到A′时,B变化到 B′,A与 B的变化量相等,即 A与 B相差的度数始终相等。

图2 系统计算要求示意图

程序采用分别对度、分、秒进行运算的办法。

(1)实现对输入数据的转换,即从压缩BCD码转化为二进制码。

(2)计算部分。本程序采用对度、分、秒分别进行运算的办法,三者之间存在进位、借位信号 c2、c3、c4、c5,其中 c2、c3分别为 A、B初始值作差时 A度分秒各部分间的进位、借位信号,c4、c5分别为B变化后的值C的各部分间的进位、借位信号。

(3)实现把运算结果从二进制码转化为压缩BCD码。

1.2 算法实现

(1)当时钟 clk为上升沿时,把输入的压缩 BCD码转换为二进制码;

(2)当 reset有效时,置入 A与 B的初始值;

(3)当 load有效时,开始计算变化量;

(4)把变化后的 B变为压缩BCD码 C;

(5)由于本电路时钟频率为 5 MHz,输入数据的频率约为200 μs。为减小毛刺,设计一个300的计数器与一个锁存器,使输出效果更佳。具体为,每当计完300个数时,输出一次程序的运算结果。

(6)设计锁存器,当计数器计完300后输出C。

1.3 压缩BCD码向二进制的转换

以度部分为例,算法思路为:个位+十位×10+百位×100。

主要程序实现如下:

Q00:="00"& (Q (9 downto 8)*"1100100"+Q (7 downto 4)*"1010"+Q(3 downto 0))。

1.4 计算B变化后的值C

以分部分为例,算法思路如下。

(1)计算初始值 A00、B00 的差量 e,e=A00-B00-c2,其中c2为A的秒部分的进位或借位信号,若e为负则自加60,并输出借位给A的度部分;

(2)计算变化后的 B 值 C,C=A0+e+c4,其中A0为变化后的A值,c4为C秒部分的进位或借位信号;

(3)判断输出 C是否大于 60,若 C≥60,则输出进位给C的度部分,并自减60输出结果C。

1.5 二进制向压缩BCD码的转换

这一部分采用循环减的办法,以C的度部分为例。

(1)判断 C是否小于 10,若小于则对 C循环减 10,直到C小于10为止,C减完后的值为个位数;

(2)对步骤(1)中减的次数 n2再进行循环减 10,n2减完后的值为十位数;

(3)步骤(2)中减的次数n1为百位数。

2 结果分析

2.1 软件仿真结果

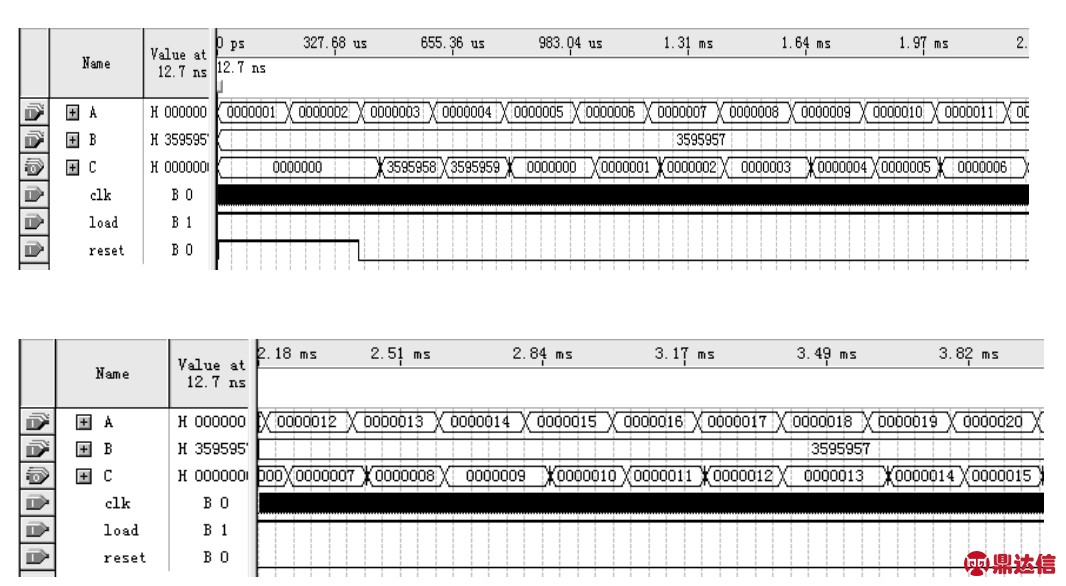

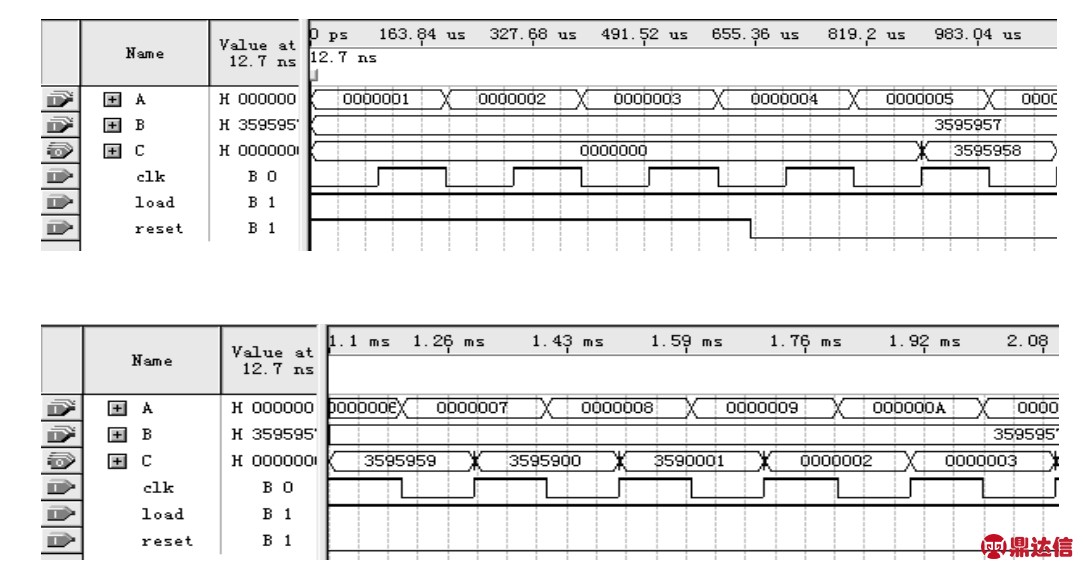

图3、 图 4 为当 A 初 值为 0,B 为 359°59′57″时,A逐次增加1″,输出结果C的变化过程。为方便检查和观看,图3为 A、B、C为未压缩BCD码的仿真结果,图4为A、B、C为压缩BCD码的仿真结果。

图3 BCD码仿真波形

图4 压缩BCD码仿真结果

由图 3、图 4可以看出,当 A初值为 0,B为 359°59′57″时,A逐次增加 1″,输出结果C的变化过程为由初值0 变为 359°59′58″, 之后顺次变为 359°59′59″、0、1″…,由结果可验证程序的正确性。

2.2 硬件调试与结果验证

硬件验证就是将编译、综合生成的下载文件下载到指定的CPLD芯片上,然后进行硬件验证。本项目通过一个转盘改变原始输入数据A,并用数码管显示出数据A,各输入数据、时钟、功能信号都由插头输入,输出数据C也由插头输出,并用数码管显示出数据C。

当数据 A 输入为 0°,B 为 359°59′59″,reset为高电平,load为高电平时,输出显示保持上一数据;当A变为1″,reset变为低电平,输出显示 0°;当 load变为低电平,输出显示 A的值 1″。

根据实验数据,验证了该电路功能的正确性与可靠性,达到了预期项目要求,实现了基于CPLD实现六十进制压缩BCD码加减运算功能。

3 不足之处与改进

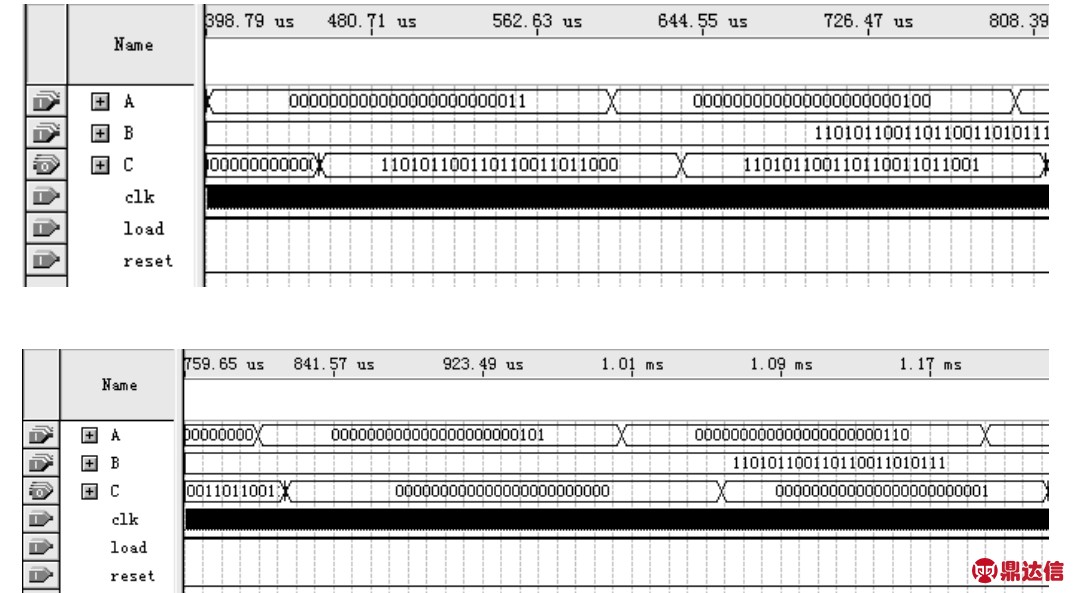

本电路的时钟频率为5 MHz,时钟频率约为数据A更新频率的1 000倍,当数据A的更新频率与时钟频率较接近时,会出现进位滞后的情况,如图5所示。

由图 5 可知, 当 A 初值为 0,B 为 359°59′57″时,A逐次增加1″,输出结果C的变化过程为由初值 0变为359°59′58″, 以 后 顺 次 变 为 359°59′59″、359°59′00″、359°00′01″、2″、3″…。 可见从 359°59′59″不能直接变到000°00′00″,直到 000°00′02″才恢复正确值,在 359°59′59″与 000°00′02″之间应该存在的两个数为 000°00′00″、000°00′01″实际为 359°59′00″、359°00′01″,这里可以看出 359°59′59″到 0°中间存在两次进位,每次进位滞后一个时钟周期,根本原因是由于数据更新相对较快,接近时钟clk的频率,在一个时钟周期内计算不完全,从而导致了进位滞后的现象。

图5 进位滞后波形

可用分频的方法实现进位的同步,比如秒、分、度分别采用时钟频率的2分频、4分频、8分频。

也可使用秒、分、度各自的计算部分占不同时钟段的方法解决,比如:秒部分从时钟上升沿开始计算,分部分从时钟三分之一周期处开始计算,度部分从时钟三分之二处开始计算。

参考文献