摘要:传统多串口并行通信数据传输系统无法自主获取串口号,需手动选择再打开串口,需要使用者事先了解接口编码,这无形增加了系统的工作时间。为此,设计一种基于FPGA的多串口并行通信数据传输系统,该系统中的串口数据接收模块采集多串口数据,并通过控制寄存器达到控制通信数据波特率的目的。系统利用NiosⅡ处理器使8种信道共同进行传输工作,其将数据传输到并串转换模块。并串转换模块对输出的8位并行数据添加通道标识、并串转换处理,再将处理后的并行数据传递到串口输出选择模块中。依据数据脉冲上升沿设计串口输出选择模块,该模块通过多路分配器将有数据通道的数据串行逐位送出。系统在软件中进行了传输设计、NiosⅡ处理器流程设计以及通信设备类的设计与封装。实验结果表明,所设计系统在FPGA上正确实现了8个串口数据的传输,并且具有较高的数据接收成功率。

关键词:多串口;并行通信;数据传输系统;数据采集

0 引言

随着计算机技术的迅猛发展,测试系统的总线技术也得到了一定的提高,人们对计算机与设备的通信能力要求越来越高。串口传输技术的出现,是实现以上要求的重要发明[1⁃4]。传统多串口并行通信数据传输系统无法自主获取串口号,需手动选择再打开串口,需要使用者事先了解串口号,大大降低了系统的运行效率。因此,研究出可自主辨识串口号的多串口并行通信数据传输系统,成为相关人员分析的热点[5⁃6]。

文献[7]通过串行处理方式完成串口数据的并行通信,但是该方式处理长数据帧时,容易出现部分串行口通信数据帧被截断的问题。文献[8]通过RTS/CTS硬件流控制串口数据,将串口通信两端的RTS和CTS线对应相连,数据终端通过RTS调控数据流,数据通信设备用CTS控制计算机的数据流。该方法的缺点是控制过程复杂,效率低。文献[1]采用XON/OFF完成基于软件流的多串口并行通信数据传输控制,当串口接收端的软件输入范围的数据量高于阈值,则向串口数据发送端传递XOFF字符,发送端采集到XOFF自发地后,终止发送数据;否则,当接收端的数据量低于阈值时,向串口数据发送端发送XOF字符,并开始发送数据。但是该方法用于文本的数据通信,具有较高的局限性。文献[3]提出一种采用多线程并行的方式,完成多串口并行数据通信的有效控制,但是该方法的控制精度较差,会出现数据帧缺失的问题。针对上述问题,设计基于FPGA的多串口并行通信数据传输系统。实验结果表明,在FPGA上正确实现了8个串口数据的传输,并且具有较高的数据接收成功率。

1 多串口并行通信数据传输系统设计与实现

1.1 系统总体设计

基于FPGA的多串口数据传输系统包括串口数据接收模块、并串转换模块以及串口输出选择模块,串口数据接收模块的主要工作内容是电平转换和数据收发,如图1所示。系统对串口数据接收模块的设计,主要进行了电平转换、UART IP特性参数分析,以及寄存器控制数据波特率的设计;系统对数据并串转换模块的设计,主要进行了解析外接信道信号、并串互转方式和时序模拟设计;系统对串口输出选择模块的设计,主要进行了解析目标信道串口数据以及ModelSim时序仿真,从中可以看出设计的系统实现了多串口数据传输的功能,并且串口波特率可调。

图1 系统结构图

通过FPGA UART IP将多串口数据传递到DSP处理器中,通过8个UART IP实现了8种串口数据的接收工作,以及通信数据波特率的实时调整,其将8种串口信道中的数据融合成1路数据,串行传输到DSP处理器中。通过FPGA完成DSP多串口的拓展工作,简化系统通信的数据传输流程,缩减系统运行成本。

1.2 串口数据接收模块设计

1.2.1 电平转换电路设计

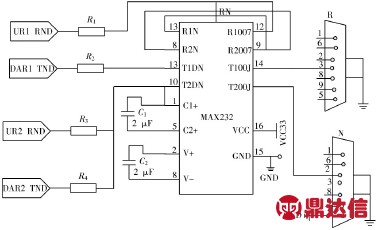

串口并行通信数据先通过电平转换电路实现数据信号转换,再将数据传至FPGA引脚。设计的串口数据接收模块采用4片MAX232芯片,完成8路UART的电平转换,其中的2路电平转换电路图,如图2所示。其他6路与此相似。

图2 电平转换电路

1.2.2 NiosⅡ处理器设计

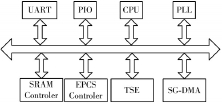

基于FPGA的多串口并行通信数据传输系统中的FPGA中NiosⅡ处理器,用于采集数据并将其发送到计算机,显控软件接收数据并存储。NiosⅡ处理器的组件设计以及如何搭建实现。设计的NiosⅡ处理器架构如图3所示。

图3 NiosⅡ处理器的架构

从图3中可以看出,NiosⅡ处理器包括四种组件,分别为:

(1)NiosⅡ运行μC/OS⁃Ⅱ所需组件:PLL,CPU,UART,其中的PLL和UART用于系统的调试和信息反馈;

(2)存储组件:SRAM Controler,EPCS Controler分别用于控制,系统的易失性存储器件和非易失性存储器件。

(3)以太网组件:TSE是以太网的通信层,SG⁃DMA用于完成串口数据的传输。

(4)管控组件:停止输入、输出PIO串口数据,进而实现对串口数据的管控。

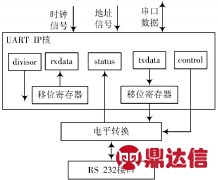

基于上述设计的NiosⅡ处理器,系统利用AlteraNiosⅡUART IP内核实现多串口通信数据的收取。其利用UART IP RXD进行经电平转换后的串口通信数据的获取,最后通过移位寄存器将获取到的数据反馈给rxdata,经由Avalon总线读取rxdata数据,并将数据传递到数据并串转换模块中。UART IP核在系统中的应用如图4所示。

图4 UART IP核在系统中的应用

UART IP核寄存器中的rxdata和txdata能够进行串口通信数据的收发工作;status主要对数据输入和读取进行标识;control管理寄存器,对接收发送数据时的中断使能进行管理;divisor寄存器,对串口波特率进行调整。系统NiosⅡ处理器经由多个UART IP进行8种串口信道的传递工作,主要将PIO输出的通信数据传输到并串转换模块。

1.3 并串转换模块设计

系统利用UART IP中的PIO传递出8位串口并行数据(取pio_0_data[7:0]通道为分析对象),这些数据传递给并串转换模块,该模块对数据进行通道标识和并串转换处理,再将处理后的数据传递到串口输出选择模块中。并串转换模块对串口数据进行通道标识的过程,也就是扩展串口数据pio_0_data到16位,高8位是通道标志,标识第一通道为1,第二通道为2,……,第八通道为8。通过移位寄存器完成16位数据的并串转换。p2s_u0串口的数据并串转换RTL视图如图5所示,可以看出8′h01被当成首路串口标识赋值在pio_data[15:0]的高8位。

图5 并串转换模块RTL视图

1.4 串口输出选择模块设计

NiosⅡUART IP每次接收到串口数据后,会形成对应的脉冲信号,脉冲信号将指引着串口输出选择模块进行工作。每个脉冲信号均会令data_vld产生周期性的电平信号,通常为高电平信号。这是由于NiosⅡ为该通道设置了特定的优先处理参数,使其在相同情况下仅产生惟一中断。因此设计多路分配器DSP,逐次输出存在数据通道的数据串行。DSP处理器利用其收取到的16位通信数据,进行数据串口的选择。

2 软件实现

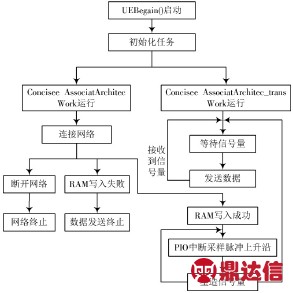

2.1 μC/OS⁃Ⅱ多任务执行流程设计同通信数据的管控

μC/OS⁃Ⅱ操作平台的多方处理能力,使其能够进行多任务的同时处理,使得CPU在多个程序间进行高速变换,确保各程序在一段时间中获取多次的CPU占用。在NiosⅡ处理器中嵌入μC/OS⁃Ⅱ操作系统,再在该操作系统中塑造两个任务:任务Concisee AssociatArchitec Work用于塑造断开网络关联和数据传输管理;任务Concisee As⁃sociatArchitec_trans Work用于发送串口数据。具体实现过程为:驱动μC/OS⁃Ⅱ中UEBegain()函数运行,逐次进行Concisee AssociatArchitec Work任务和Concisee Associ⁃atArchitec_trans Work任务的初始化,确保两个任务并行工作,Concisee AssociatArchitec Work接收到客户端的网络关联申请时,连接网络。

(1)Concisee AssociatArchitec Work获取客户端端口网络指令时,网络中断;

(2)Concisee AssociatArchitec Work获取客户端终止发送指令时,RAM无法进行写操作,停止串口数据发送;

(3)Concisee AssociatArchitec Work采集客户端发送串口数据指令后,RAM进行数据的写操作,若RAM写入31 543个数据,此时的输入中断将移动至脉冲信号的攀升处,调用UEEin Pos(t)进程令数据数量自动传送出去,Concisee AssociatArchitec_trans Work中UEEin Sinre()函数发现该信号量后,开始发送数据,完成全部数据的发送后,驱动UEEin Glv()函数过滤信号量,接收后续脉冲沿形成的信号量,上述过程不断运行,完成串口数据的发送。

NiosⅡ处理器中融入μC/OS⁃Ⅱ的工作流程以及串口数据发送控制过程,如图6所示。

2.2 通信设备设计和其封装技术

系统利用Pcomm数据库对通信设备进行设计,并根据其载入和封装技术,将其分为串口和设备两种类型。串口类型能够进行串口的开启、封闭以及通信数据的预设工作。

设备类型则能够将多串口的收发特点一一分析出并存储,随即对其进行编译和解编译,CALLBACK函数能够实现这一操作的调用。

图6 NiosⅡ处理器的工作流程

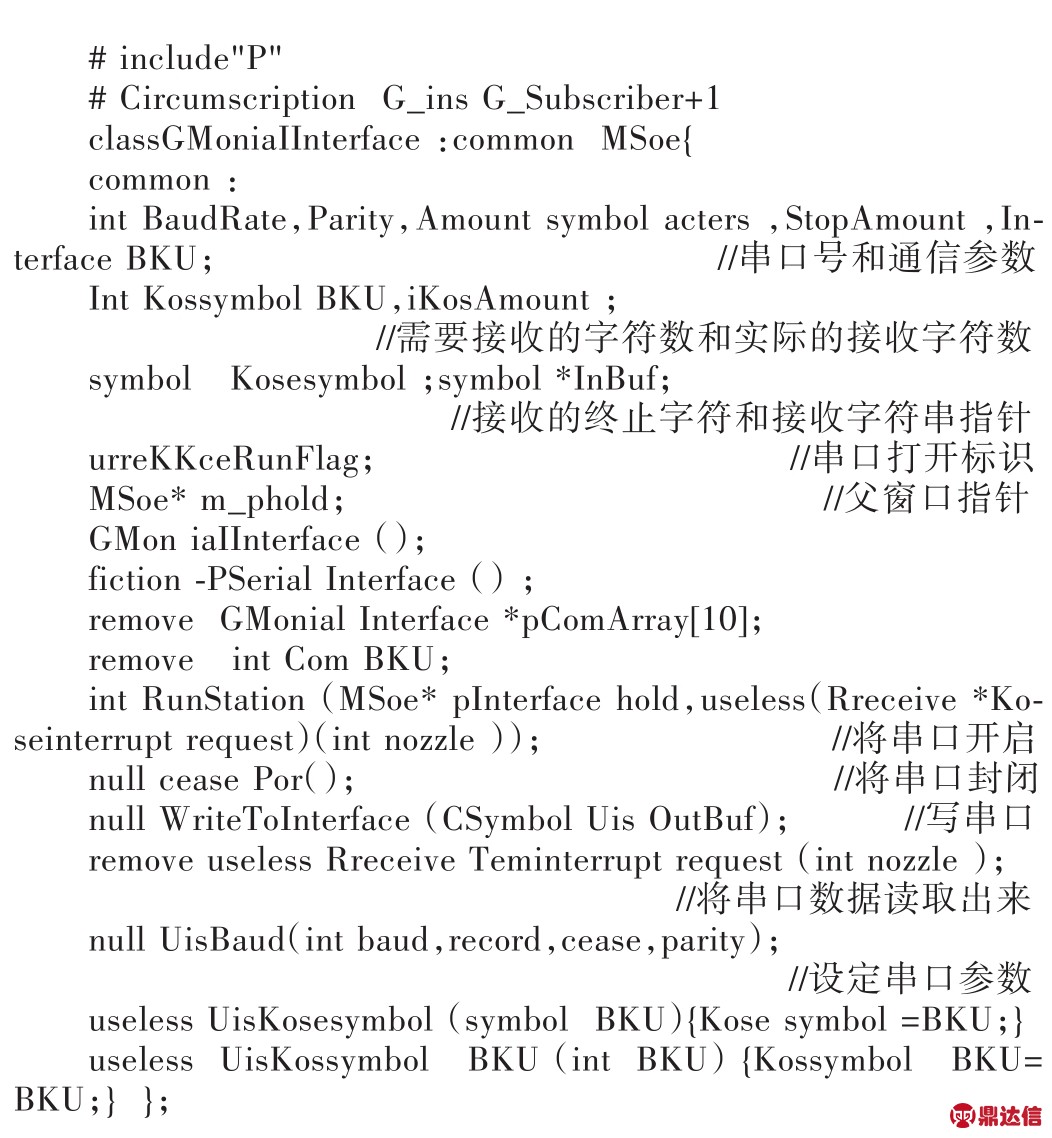

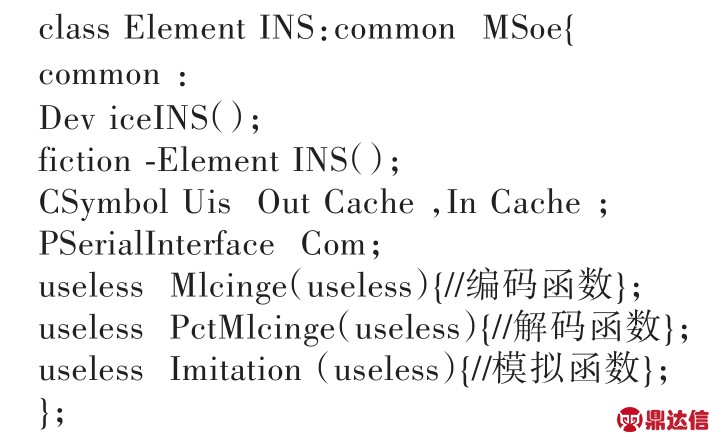

软件为串口类型设计的语言如下:

设备类实现代码如下:

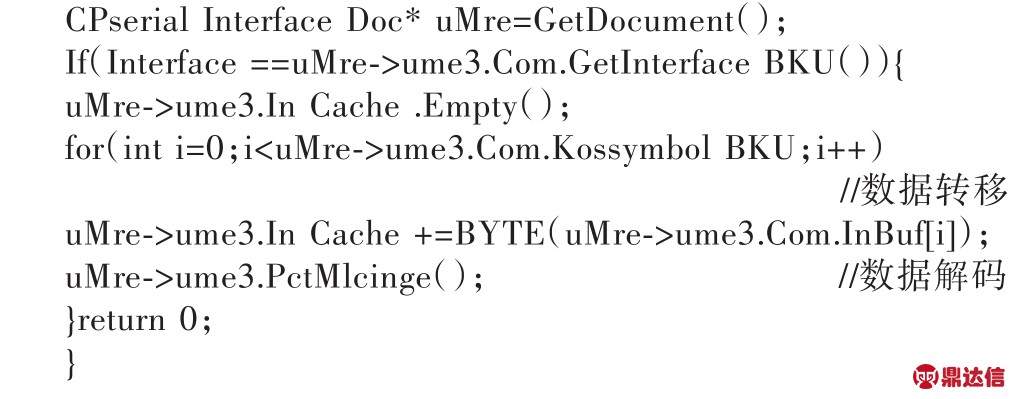

设备初始化和数据通信控制代码如下:

根据上述语言为多串口构建模型,假设该模型是设备类型内的重要组成变量,将文本的初始数据纳入到文本模型和串口通信中,并引用上述语言预设串口通信传输类型,进而开启模型入口,并塑造相应的线程;采用CALLBACK语言对所构建的设备类型模型中的线程进行整理和控制,进而实现多串口并行通信数据的通信处理。

3 实验分析

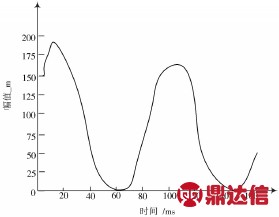

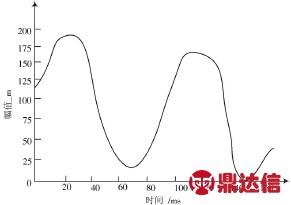

实验在计算机USB接口上连接了UART转换器,并参考说明对其进行启动,当UART转换器亮起绿灯,则代表模型已完成构建。令UART转换器的信号总线短路,排除外部信号干扰,实现传输信号的自动收发。利用本文所设计的基于FPGA的多串口并行通信数据传输系统在上述模型中进行工作,UART转换器的面板灯的亮灭,代表本文系统的工作状态是否正常。利用UART转换器的串口号,设置合理的比特率、校验位和停止位,并向发送区输入一周期的正弦数据,按下发送数据键,接收数据区会呈现发送的正弦波形,同时随着时间的变化而进行平稳移动,直至按下终止键。自发自收情况下的系统检测结果如图7所示。用本文设计的基于FPGA的多串口并行通信数据传输系统获取的结果如图8所示。

图7 串口通信系统检测结果

对比分析图7和图8能够看出,本文系统检测到的串口通信数据与正常运行状态下的输出数据无较大差别,证明本文系统是有效的。实验解析了本文系统中两个验证标准,分别为数据接收的时间延迟以及其成功率。利用多串口将通信数据从各并列系统向终端传输,必然会引起数据接收的时间延迟,且不同系统的延迟时间状态均不一致。把接收数据的终端时间减去并列系统的时间延迟时间,即可得到延迟时间(称作“延时值”);数据接收的成功率则用终端接收数据的有效量与并列系统总数据量相比表示。

图8 FPGA串口发送数据检测结果

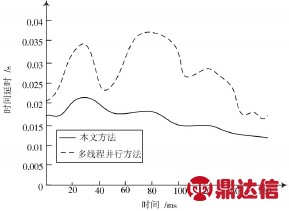

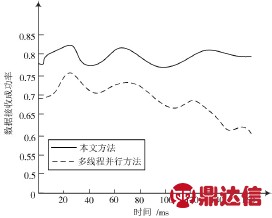

实验选取12 m长的串口线,该串口线的收据发送频率高达15 Hz,通信中的数据波特率是1 029 622 b/s。通过多次长时间实验,实验获取本文方法和多线程并行方法的相关数据分析结果,如图9和图10所示。

图9 通信延时曲线

分析图9和图10可得,相对于多线程并行方法,本文方法具有较低的通信延时和较高的数据接收成功率,能够实现串口数据的可靠通信。

4 结论

本文设计基于FPGA的多串口并行通信数据传输系统,该系统中的串口数据接收模块采集多串口数据,并通过控制寄存器达到控制通信数据波特率的目的。系统利用NiosⅡ处理器使8种信道共同进行传输工作,其将数据传输到并串转换模块。并串转换模块对输出的8位并行数据添加通道标识、并串转换处理,再将处理后的并行数据传递到串口输出选择模块中。依据数据脉冲上升沿设计串口输出选择模块,该模块通过多路分配器将有数据通道的数据串行逐位送出。系统在软件中进行了传输设计、NiosⅡ处理器流程设计以及通信设备类的设计与封装过程。实验结果表明,在FPGA上正确实现了8个串口数据的传输,并且具有较高的数据接收成功率。

图10 数据接收成功率曲线