摘 要: 搭建共差模抑制比测量系统,提出共差模分离器抑制比的测试方法:对输入端内部并联和外部并联两种连接结构进行测试和探讨,提出采用两路相位相互可调的鼎阳SDG2122X信号源替代差模信号变换器的方法,实现了高频段(30 MHz~110 MHz)共差模抑制比>30 dB的指标。反复试验表明:方法可行,可方便地进行抑制比性能的分别调整。方法已被相关检测机构采用,建议标准研究部门开展共差模分离器抑制比测试方法的研究。

关键词: 共差模;分离器;抑制比;鼎阳SDG2122X信号源;电磁兼容;相位

引言

目前,传导发射测试规范中只规定测试传导发射的干扰总量。为了能够精确测量传导发射所包含的共模(CM)和差模(DM)分量,学术界在不断地探索从传导发射干扰总量中分离出共模和差模分量的各种理论和方法。这些理论和方法与有效抑制传导干扰的EMI滤波器密切相关,而EMI滤波器的合理设计又与共模和差模分量密切相关,所以成为电磁兼容研究的热点课题[1-7]。

目前相关研究尚停留在“试错法”的原始状态,在不知道共模和差模分量的情况下,采用不断更换EMI滤波器的方法来观察抑制传导干扰总量的效果,导致了大量人力和物力的浪费。现在市场已有共差模分离产品公布了其共差模抑制比(隔离度)的性能指标,但由于目前没有相关共差模分量测量的国际或国家标准规范,所以这些性能指标失去了应有的推广应用作用。

本文针对共差模抑制比的测试方法进行论述,提出共差模分量的具体测试方法,通过实际测试验证测试方法可行性,以供相关行业制定共差模分量测试规范时参考。

1 共差模抑制比的理论定义

查阅相关文献[3],将共差模抑制比定义如下。

1.1 差模抑制比

差模抑制比(DMRR)定义为

其中,

Vo,cm表示输出的共模信号幅值;

Vi,dm表示输入的差模信号幅值。

差模抑制比所表达的物理概念是,DM输出信号不应受到输入CM电压的影响,即差模抑制比表示对共模信号的抑制程度。在理想情况下,DMRR=0。

1.2 共模抑制比

共模抑制比(CMRR)定义为

其中,

Vo,dm表示输出的差模信号幅值;

Vi,cm表示输入的共模信号幅值。

共模抑制比所表达的物理概念是,CM输出信号不应受到输入DM电压的影响,即共模抑制比表示对差模信号的抑制程度。在理想情况下,CMRR=0。

2 共差模抑制比的测量方法

2.1 原理框图

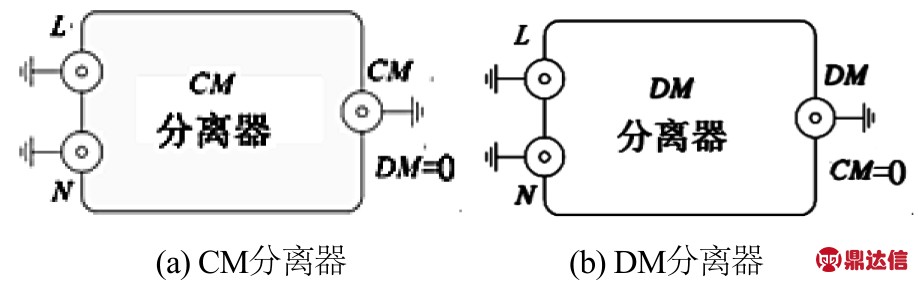

共差模分离设备一般由共模分离器和差模分离器组成。理想情况下,共模分离器输出的共模分量信号不受输入的差模信号影响,而差模分离器输出的差模分量信号也不受输入的共模信号影响。测试时,L、N在没有相位可调的信号源时可用共模或差模信号变换器替代,原理框图如图1所示。

图1 共差模分离器原理框图

2.2 测量系统

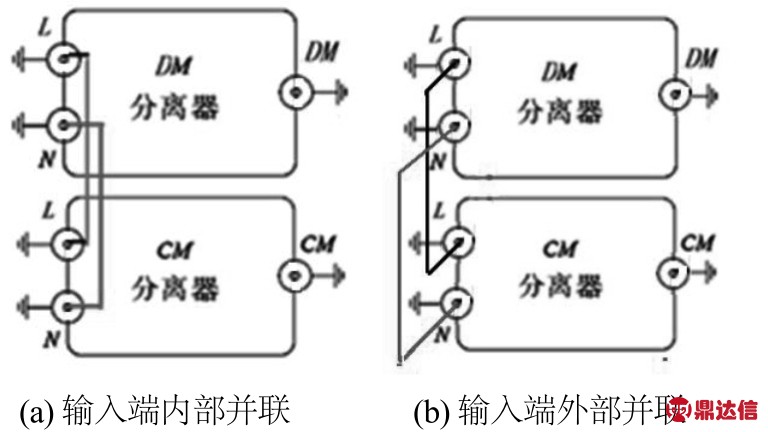

CM分离器和DM分离器有输入端内部并联和输入端外部并联两种连接结构,如图2所示。

图2 两种输入端连接结构

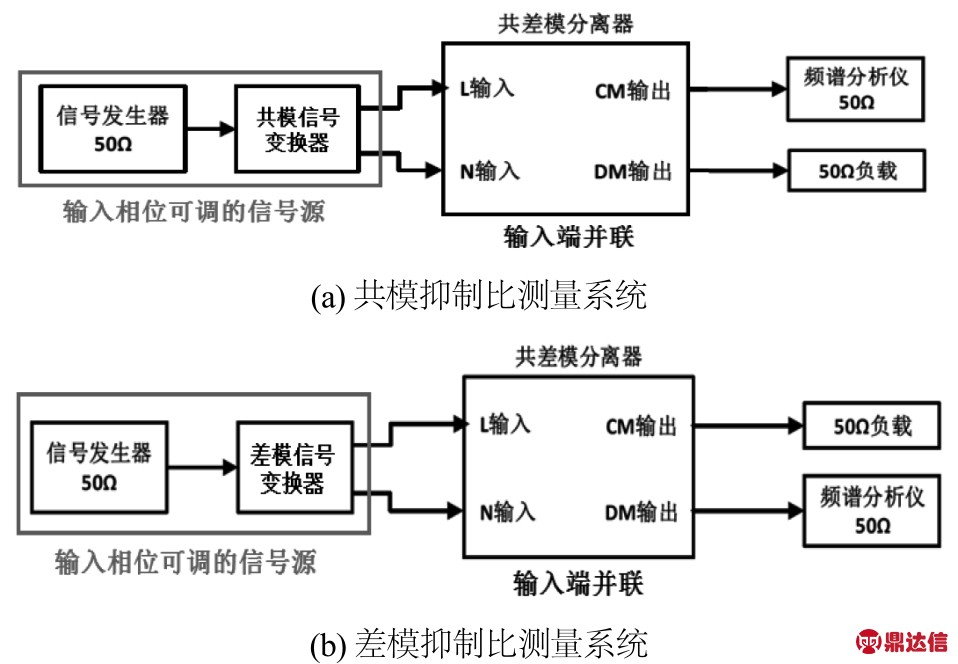

抑制比测量系统如图3所示,其中:

(1)输入端内部并联是在同一屏蔽外壳内部,共模和差模分离器的输入端是内部并联的;输入端外部并联是使用两个屏蔽外壳,共模和差模分离器的输入端是外部并联的。

(2)输入信号应采用相位可调的标准信号源;如果不在100 MHz范围内,也可以采用该范围以下的信号变换器。

(3)共模信号变换器将信号源的单端输出信号变换为两路幅度和相位相同的输出信号;差模信号变换器将信号源的单端输出信号变换为两路幅度相同、相位相反的输出信号。

图3 共差模抑制比测量系统

(4)为了匹配的需要,在测试共模输出时,差模通道的输出端要接50 Ω匹配负载;在测试差模输出时,共模通道的输出端要接50 Ω匹配负载。

(5)以上测试方法被北京泰派斯特科技发展有限公司和航天科工集团203所采用。

2.3 实际验证

为了实际验证抑制比测量方法的可行性,本节提供若干实测案例。

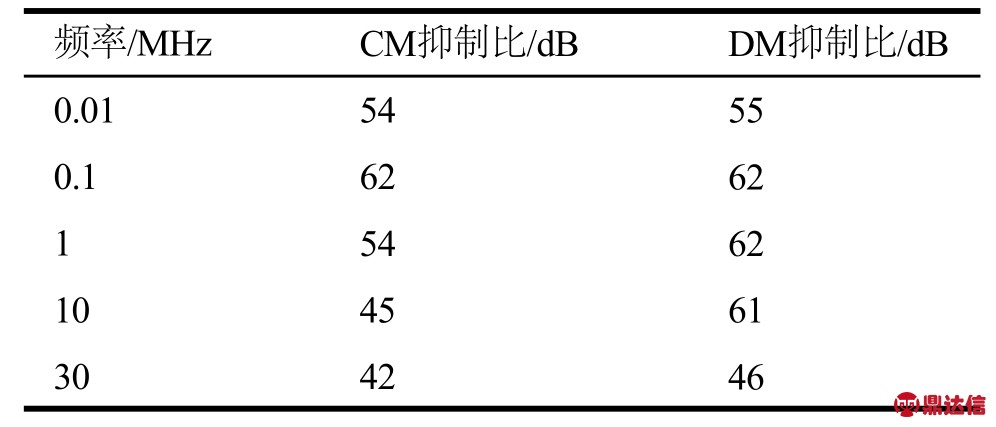

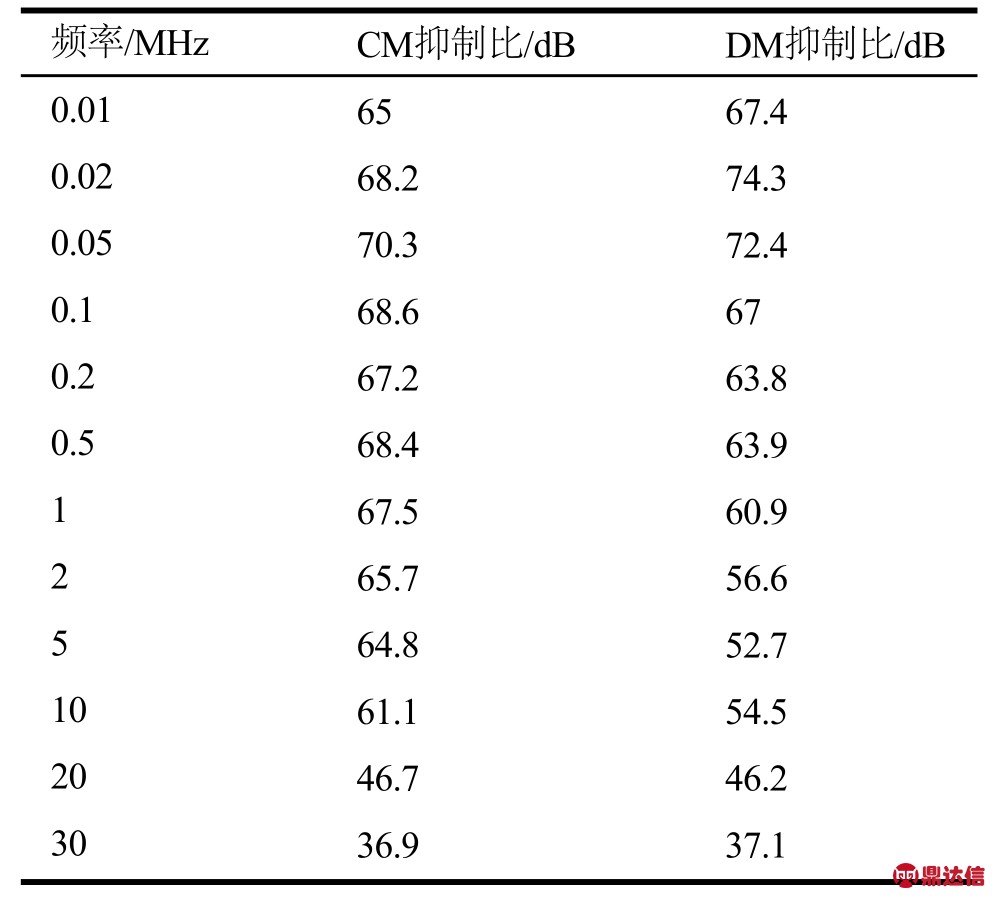

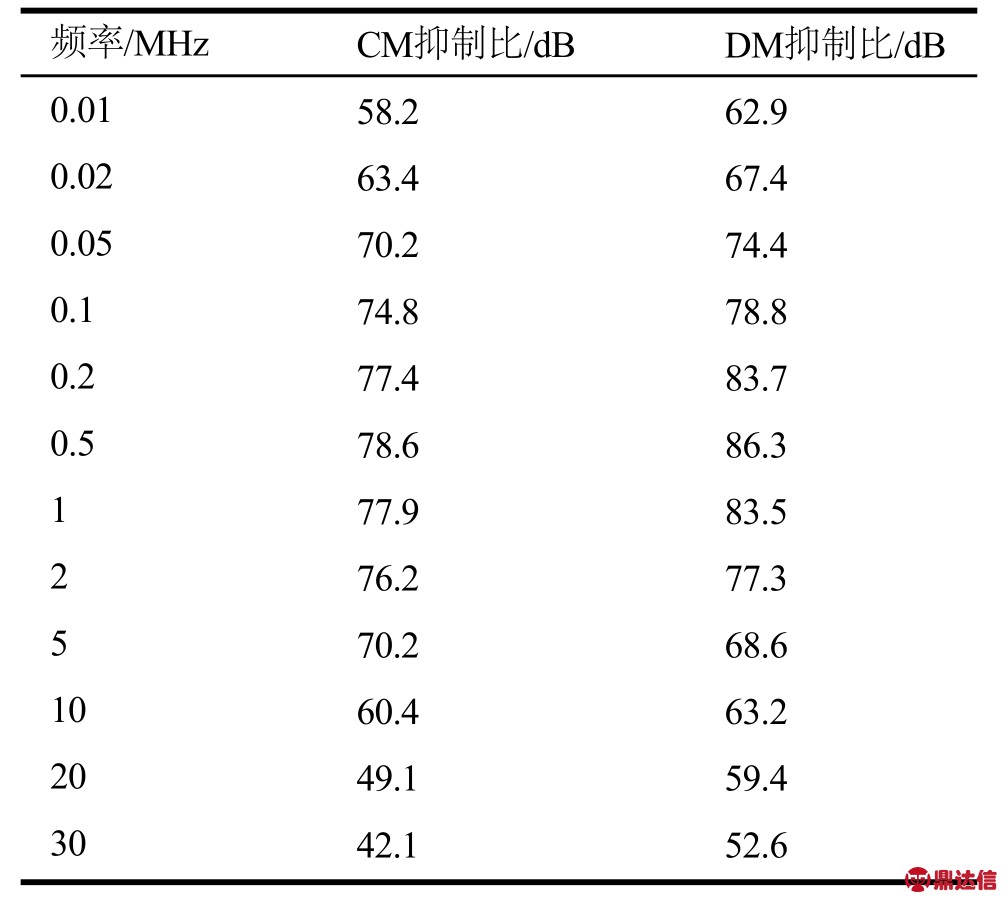

韩国EMCIS公司EA-2100 EMI Analyzer共差模分离器原规格书中的抑制比性能数据如表1所示。

表1 EA-2100 EMI Analyzer共差模分离器抑制比性能数据

采用本文测试方法所得的测试数据如表2所示。

表2 采用本文测试方法所得的测试数据

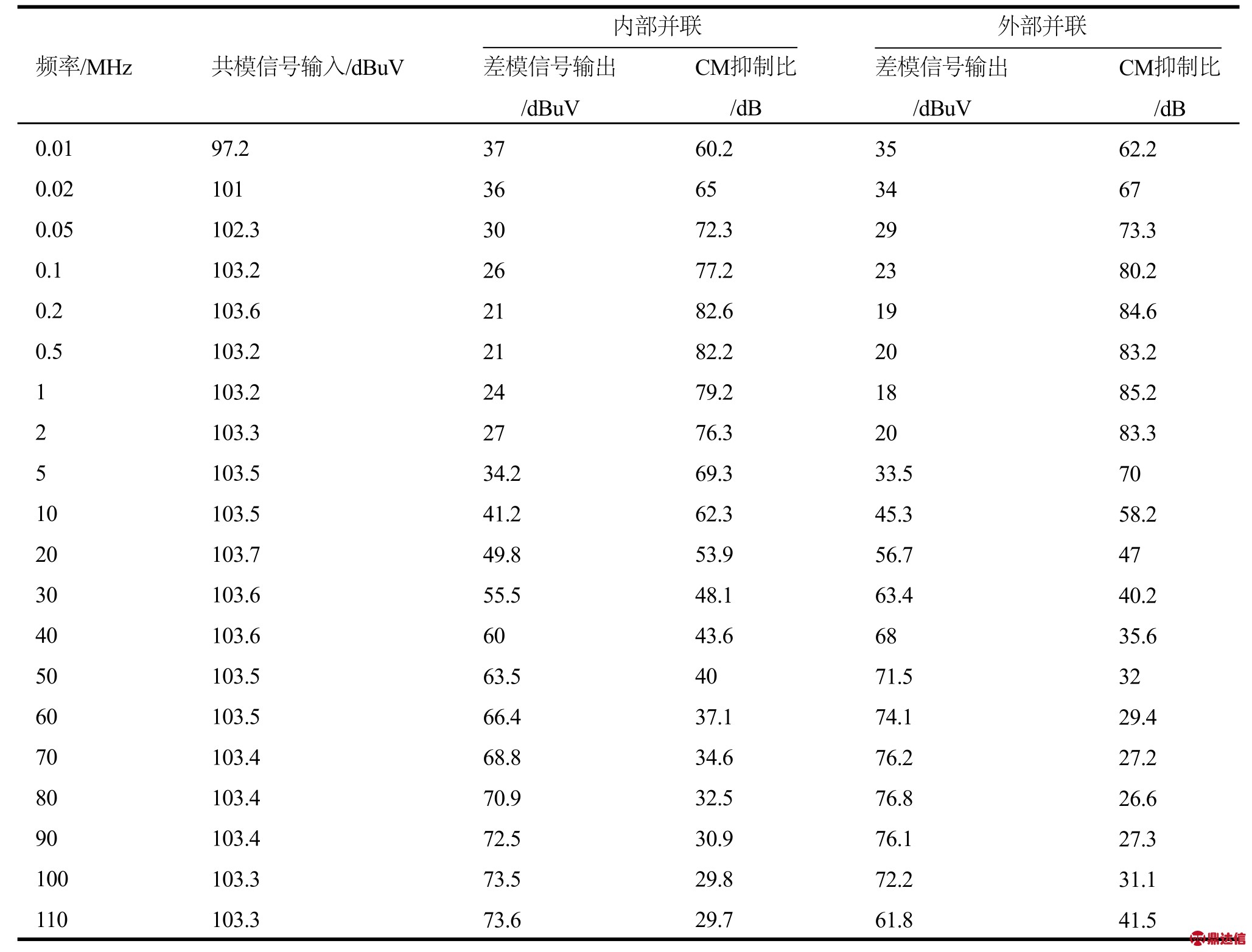

对于北京泰派斯特科技发展有限公司EA3040综合分析仪内的共差模分离器,航天科工集团203所采用本文测试方法所得的测试数据如表3所示。

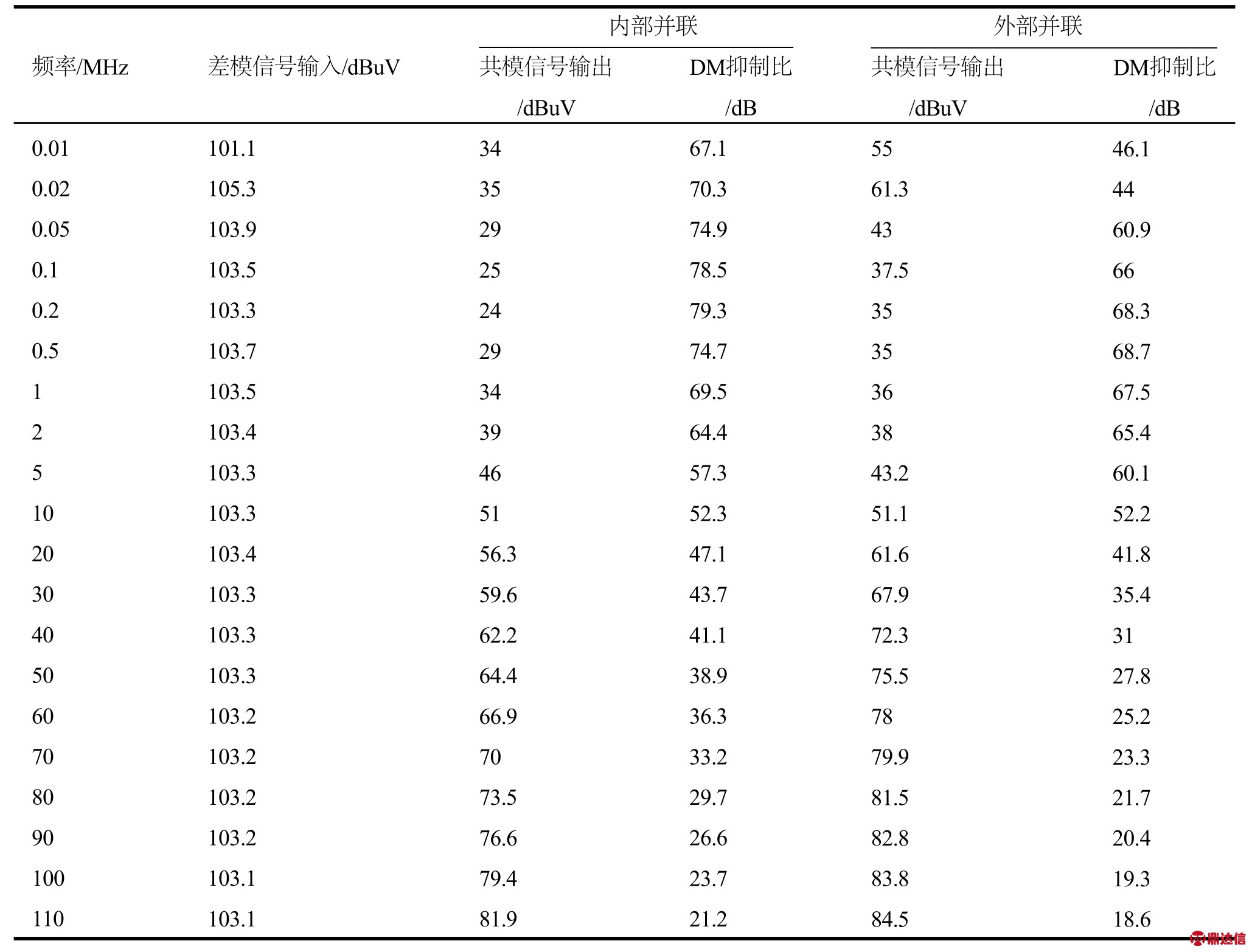

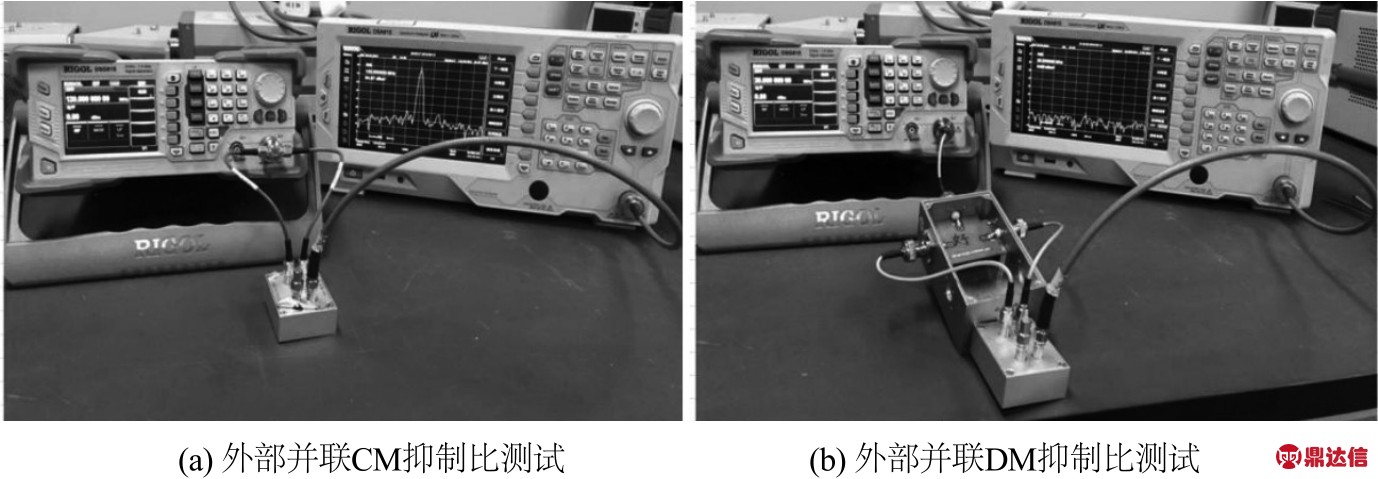

3 输入端内部并联和外部并联结构的测试和探讨

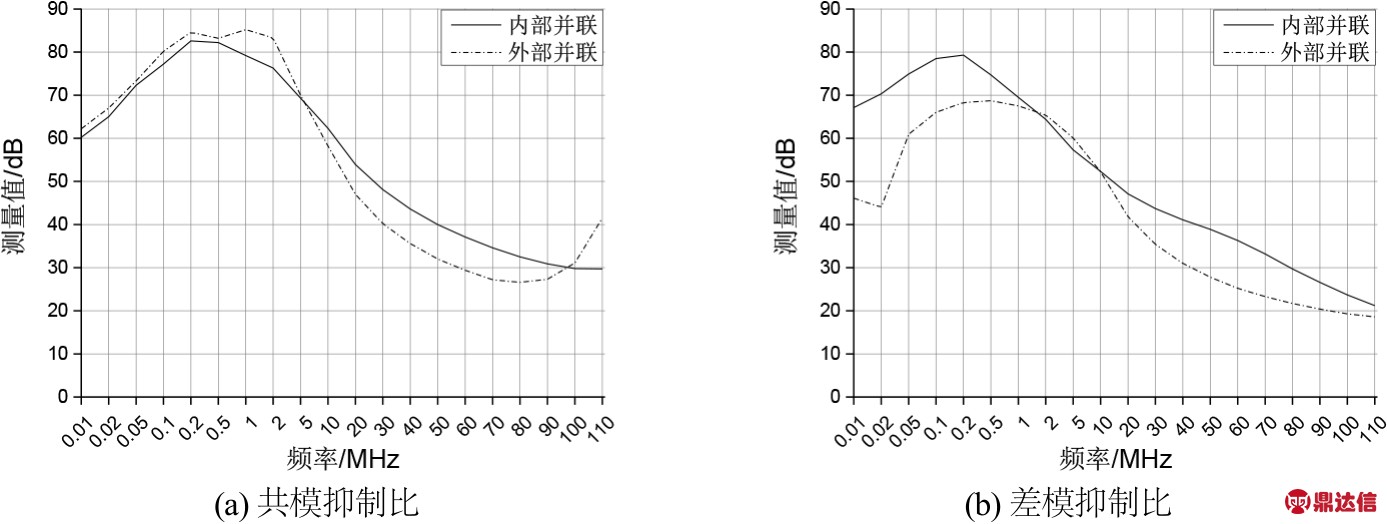

通过实际反复测试发现,在内部并联结构中,由于CM和DM分离器分别安装于PCB的正反面,因此两者之间会产生相互的电磁耦合和电路耦合,对两者的抑制比产生影响。为了验证,本章对输入端内部并联和外部并联两种连接结构进行对比测试,结果分别如表4和表5所示。输入端外部并联结构的实验样机如图4所示。根据表4和表5绘制的曲线如图5所示。根据测试结果得到以下认识:

表3 航天科工集团203所采用本文测试方法所得的测试数据

(1)对比受到电磁和电路耦合的影响程度,差模抑制比要大于共模抑制比。

(2)输入端外部并联结构没有电磁和电路的耦合影响,便于进行抑制比性能的分别调整。

(3)若10 kHz~30 MHz频段抑制比指标>40 dB,那么无论外部并联还是内部并联结构,基本上都能达到要求。

(4)若30 MHz~110 MHz频段抑制比指标>30 dB,那么无论哪种分离器结构,抑制比指标都不满足。换言之,还另有原因影响高频段抑制比指标。

4 影响抑制比指标的诊断

若要实现30 MHz~110 MHz频段抑制比>30 dB的指标,那么分离器电路拓扑的对称性、共差模信号变换器的相位精度以及分离器的L、N信号源输入电缆长度对称性等等,凡是涉及相位的,都是重要影响因素。

表4 输入端内部并联和外部并联结构的共模抑制比测试数据

表5 输入端内部并联和外部并联结构的差模抑制比测试数据

图4 输入端外部并联结构的实验样机

图5 输入端内部并联和外部并联结构的测试数据曲线

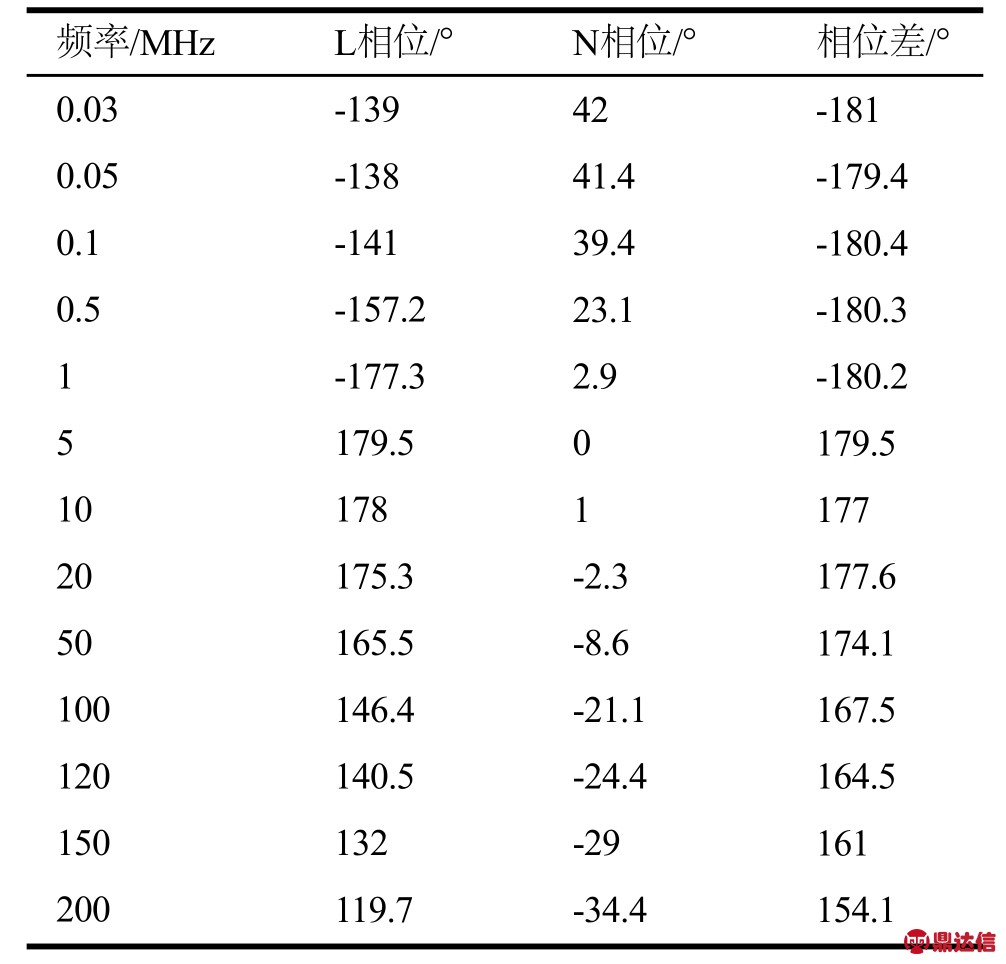

表6 差模信号变换器两路输出信号的相位差

用网络分析仪,在50 Ω负载测试条件下,对差模信号变换器的两路相位差进行测量,结果如表6所示。在30 MHz时L、N信号源之间的相位误差约为3.6°,在100 MHz时L、N信号源之间的相位误差约为12.5°。

值得注意的是,表6只是差模信号变换器两路输出信号的相位差,而表5的抑制比数据是差模信号变换器和差模分离器内部电路的综合结果。

为了证实这一认识,采用可调相位的函数发生器(鼎阳SDG2000X)替代差模信号变换器,在110 MHz人为调整L、N信号源之间的相位差来补偿差模分离器内部造成的相位差时,发现在110 MHz满足抑制比>30 dB指标时的相位差分别是:内部并联分离器为13°、外部并联分离器为7°。

总之,若要使差模分离器在30 MHz~110 MHz频段满足抑制比>30 dB的指标,必须调整差模分离器内部电路和外部连接电缆的两路相位差等于或接近180°。

5 结束语和建议

(1)实际测试表明,本文提出的共差模分离器抑制比测试方法是正确可行的。该方法已被航天科工集团203所采用。

(2)本文提出的共差模分离器抑制比测试方法可供制定国际、国家及行业标准时参考。

(3)本文提出的共差模分离器差模抑制比诊断方法的关键点在于要采用两路相位相互可调的鼎阳SDG2122X信号源,以更好地满足抑制比的指标要求。