摘 要:数据的串并转换与字节对齐是高速串行数据通信的一个重要环节.为了使串并转换后输出的并行数据是一个完整字节,设计了一种基于FPGA的高速数据串并转换及字节对齐方法.首先在数据中嵌入8B/10B编码中的K28.5同步码,然后将数据串化发送.用Verilog HDL语言设计了串并转换模块和码形检测模块.串并转换模块负责产生并行时钟并将串行数据并行化后进行输出.实现了1∶10的串并转换以及并行数据字节比特偏移的检测和调整的功能.通过对不同传输速率下的数据进行实验验证,结果表明,该方案能满足高速串行数据通信的要求,减少了硬件电路的设计复杂程度.

关键词:串并转换; 字节对齐; FPGA; 8B/10B编码

高速串行通信凭借传输速率高、抗干扰能力强、电路结构简单、传输距离远等优势已经成为高速数据通信的理想选择.工作模式由数据串化与时钟嵌入、低压差分传输、时钟数据恢复、串-并转换以及数据编码这几部分组成[1-3].其中串-并转换是在时钟的驱动下,将单比特的位数据流输入移位寄存器,直到移位寄存器存满输出并行数据的过程[4].为保证准确恢复出发送的并行数据,需要在接收端找到每个字节的边界,并将每个字节的头对齐,这个过程称为字节边界对齐[5].串-并转换及字节边界对齐是保证高速串行数据被成功接收的重要环节.

在高速串行数据通信中,已有将串行数据并行化的方法,例如苏彦峰等[6]利用D触发器搭建了用于千兆以太网收发器的串并转换电路,自行设计了串行移位寄存电路、同步信号检测电路以及并行时钟发生电路.周玲和林福昌[7]设计了一种在数据的串并转换中进行并行数据与字节时钟同步的电路,实现了同一时刻输出的并行数据是一个字节的功能.魏智[8]分别采用Maxim公司生产的MAX9206和MAX9208LVDS解串器进行数据解串,该解串器内部自带时钟数据恢复、串并转换和输出锁定的功能,保障了并行数据传输的稳定性.上述几种方案均采用硬件电路实现数据的并行化处理过程,增加了设计复杂度和系统成本,硬件电路的增加也为系统增加了潜在的故障点,并且通常工作频率范围有限,因此不能作为最佳的选择方案.孙志雄和谢海霞[9]基于现场可编辑逻辑门阵列(FPGA)设计了一种串并转换器,但该方法缺乏字节检测的环节,长时间工作的稳定性得不到保障.

Altera公司生产的CycloneⅢ系列EP3C25F324C8N,这款FPGA具有215个输入/输出接口以及24 624个逻辑单元,经过验证该FPGA工作频率可以达到250 MHz以上.本文基于这款FPGA设计了一种高速串行数据串并转换以及字节边界对齐的方法,首先在并行数据发送端对需要发送的并行数据进行编码处理,将8B/10B编码中的K28.5同步码整合到数据中,然后将数据串化发送.在数据接收端通过编程设计串并转换单元(包括移位寄存器、字节位移调整以及产生并输出并行时钟的功能)和数据字节位移检测单元.该方法在系统长时间不间断工作的方式下,数据传输没有产生误码,是一种低成本并且可靠的方法.

1 系统设计

1.1 数据传输流程

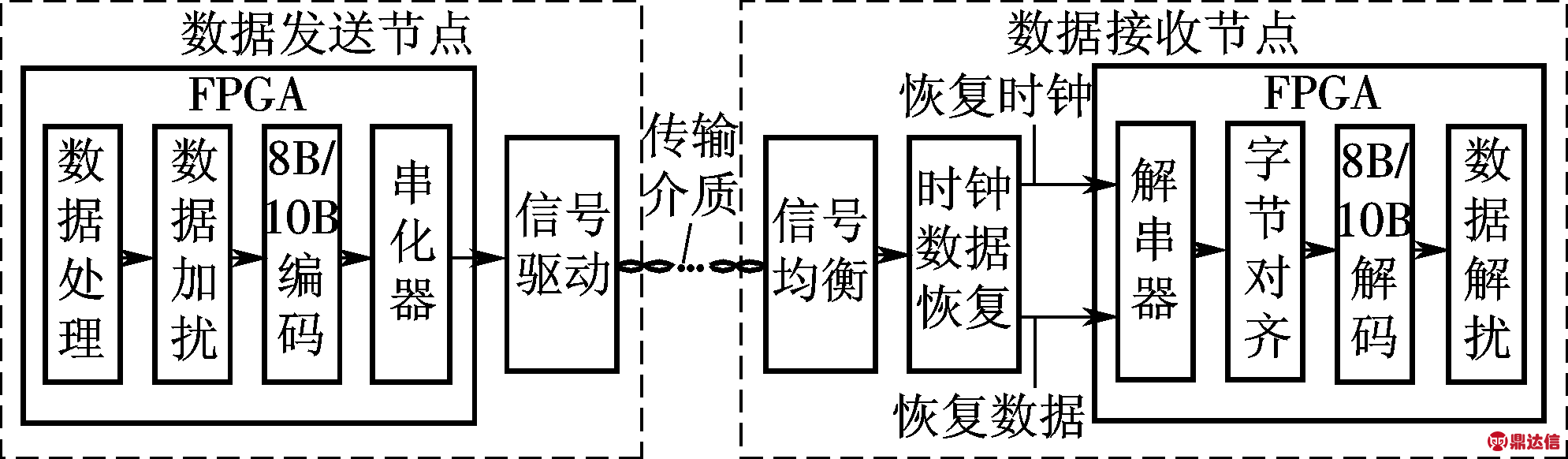

高速串行数据通信的数据传输流程如图1所示.数据传输系统主要由发送节点、传输介质和接收节点组成.在发送节点中,首先通过FPGA逻辑编程控制数据帧的结构,在传输总线中没有数据时自动填充K28.5控制码流用于总线的同步,再依次经过数据加扰、8B/10B编码来实现抑制EMI噪声干扰和数据传输直流平衡的目的.8B/10B编码后产生的10位并行数据通过串行器转变为串行数据,并且与串行时钟同步进行输出.串行数据输入至信号驱动芯片后可以提高信号的峰峰值,这样能抵消一部分传输过程中信号产生的幅值衰减,更好地实现信号的远距离传输.数据发送节点与接收节点间由传输介质进行连接,该传输介质通常选取双绞线或者同轴电缆.数据接收节点主要由信号均衡芯片、时钟数据恢复模块和FPGA构成.信号均衡芯片能够减少信号由于长距离传输所造成的失真与码间串扰.时钟数据恢复模块能够恢复出串行数据与串行时钟.串并转换单元作为解串器被调用,时钟数据恢复模块恢复出的串行数据与时钟通过该解串器后转换成并行数据.在串并转换单元随着同步时钟输出的并行数据可能存在字节错位的情况.字节对齐的环节就是通过字节位移检测单元检测K28.5同步码来确定数据错位的情况,并反馈移位脉冲给串并转换单元来进行字节位置的调整,从而完成数据移位调整的功能.当移位调整完成后再通过FPGA控制8B/10B解码和数据解扰,完成数据的处理与分析.

图1 串行数据传输流程

Fig.1 Flow chart of serial data transmission

1.2 串并转换原理

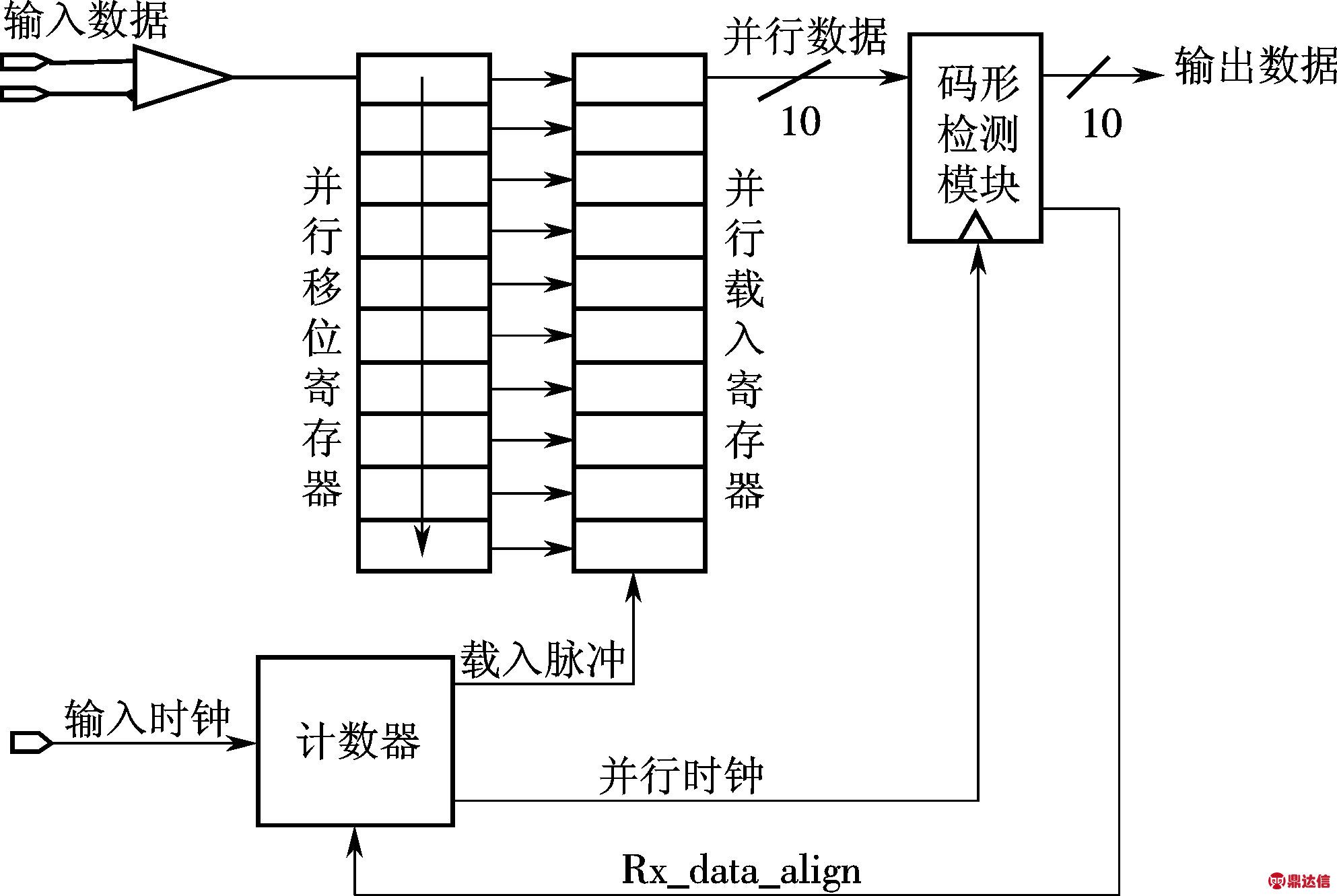

串并转换原理如图2所示,串并转换单元首先接收由数据时钟恢复模块恢复出来的串行数据和串行时钟.首先获取码形检测模块工作需要的同步并行时钟.因为经过8B/10B编码后的并行数据以10比特为单位,所以同步并行时钟与串行时钟是10分频的关系.以串行时钟为基准,设定一个4位的计数器,该计数器以串行时钟的下降沿为基准进行累加,当计数器的模累加到4或9时,输出并行时钟(clk_out)进行翻转.从而达到串行时钟的10分频的目的以获取并行时钟.并且在串行时钟下降沿的作用下串行数据被存入并行移位寄存器中(D_SR),在串行时钟的上升沿和载入脉冲的作用下并行数据被存储到并行载入寄存器(D_LOAD)中.由于并行数据是以10比特为单位向下载入的,所以载入脉冲直接决定了并行数据字节边界的位置.因此只要控制载入脉冲到来的时刻便可以调节并行数据的边界.Rx_data_align作为串并转换模块的反馈信号可以控制载入脉冲的频率,当Rx_data_align出现高脉冲并且至少持续两个并行时钟周期时,计数器便会在一个串行时钟的周期多进行一次计数,这样一来,并行数据存储到并行载入寄存器内的时间便得到了调节,数据字节的位置也得到了相应的调整,直到并行数据的字节实现对齐.

图2 串并转换原理示意

Fig.2 Schematic of principle of serial-to-parallel conversion

1.3 码形检测模块的设计

码形检测模块通过Verilog HDL语言编程实现,该模块主要实现检测字节边界并反馈给解串模块字节边界调整脉冲的功能.即接收解串器输出的10位并行数据,然后通过比较这10位并行数据的位置来调整Rx_data_align脉冲的个数,决定了串并转换模块中计数器计数的频率.

检测字节边界首先要检测同步码,本实验采用的同步码是8B/10B编码中的特殊同步码K28.5.K28.5是一种非平衡码(数据位1和0的个数不相等),这种码有两种表现形式,分别为1100000101和0011111010,用16进制表示分别为305H和0FAH.经过8B/10B编码后的K28.5的10B码序列如图3所示,两种表现形式间隔排列.

图3 K28.5同步码序列

Fig.3 K28.5 synchronous code sequence

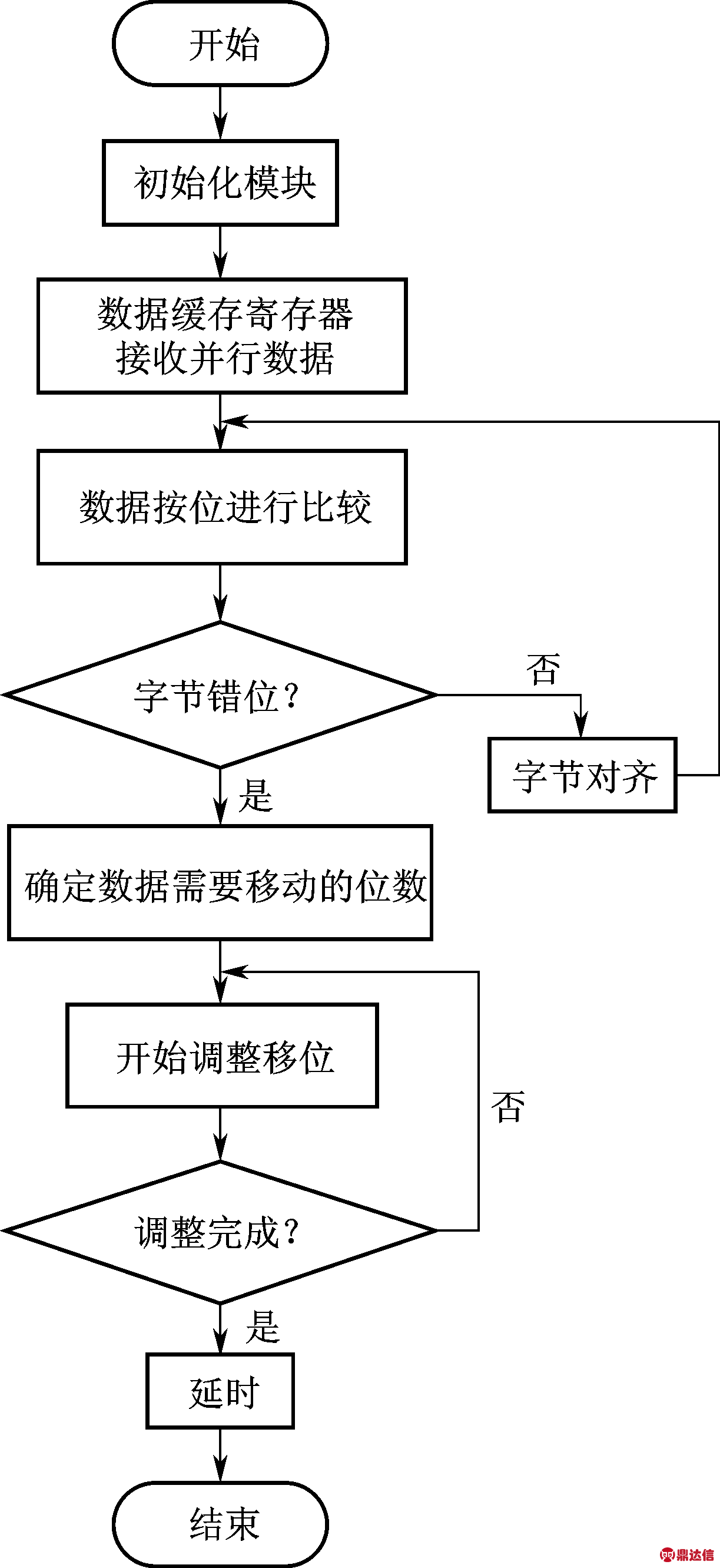

码形检测程序流程如图4所示.完成了模块的初始化配置后,由内部数据缓存寄存器接收并行数据,将数据缓存寄存器中的数据与305H/0FAH按位进行比较来确定数据字节的字头是否已经对齐.如果数据与305H/0FAH完全匹配则字节边界已经完成对齐,否则判断字节已经错位,进一步确定数据需要移动的位数,并通过控制Rx_data_align高脉冲的时序进行移位调整.待移位调整完成后延时6个并行时钟周期来确保数据缓存寄存器中的数据被更新.数据字节位移检测以及错位调整结束.

图4 码形检测程序流程

Fig.4 Flow chart of code pattern checking

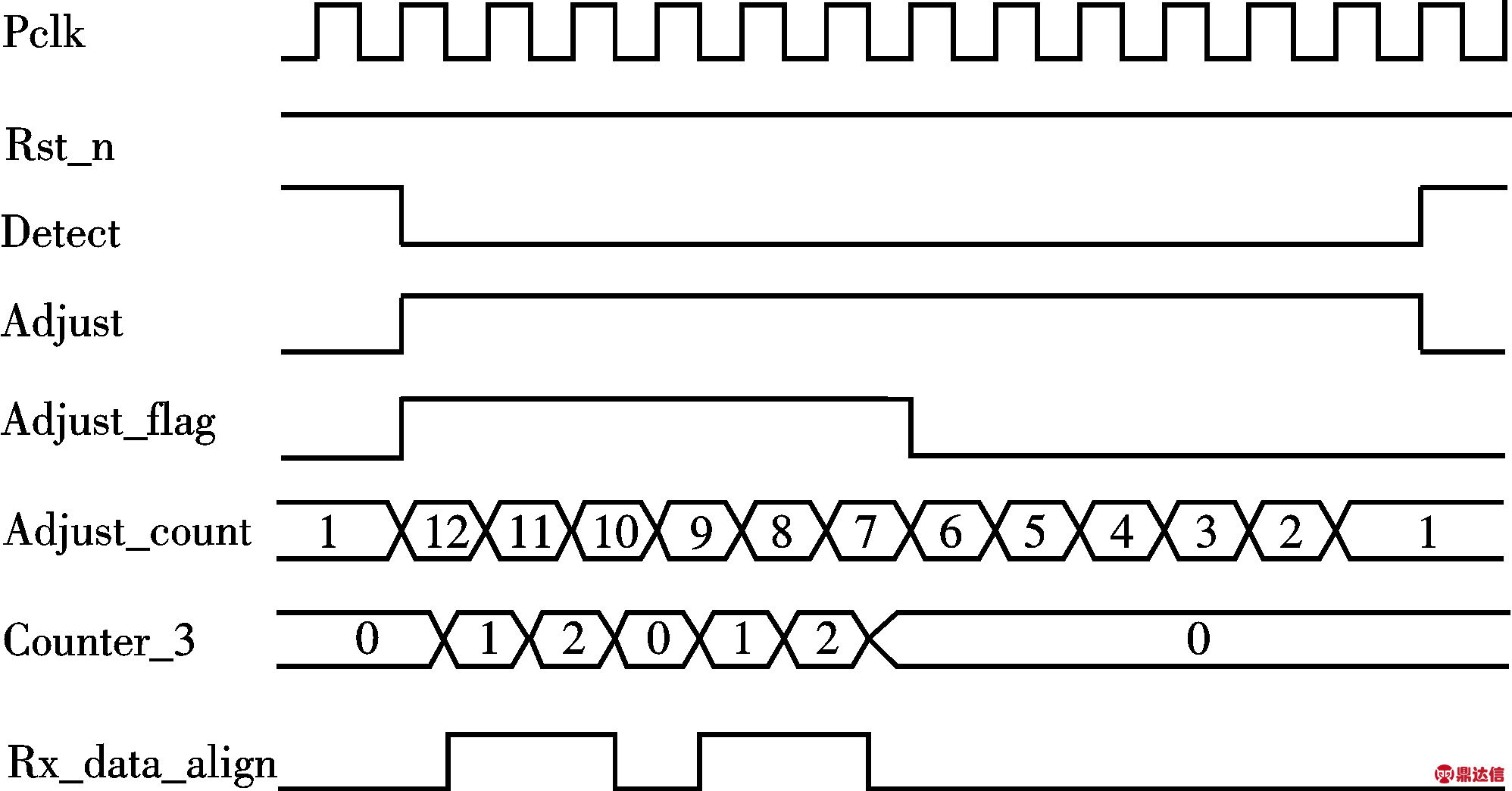

1.4 码形检测模块的时序逻辑

码形检测模块的时序逻辑如图5所示,以字节偏差两位为例.Pclk为并行时钟,当检测到字节存在错位偏差后,Adjust被置1,寄存器Adjust_count被赋值为12,Adjust_flag标志位也被置1,计数器Counter_3开始计数,计数到2后被置0.所以Rx_data_align被置高并维持两个并行时钟周期后被拉低,当Adjust_count被计数到7后标志位Adjust_flag被置0.在这期间Counter_3完成了两次计数,结果产生了两个Rx_data_align脉冲,这两个脉冲被反馈给解串器模块进行字节边界调节.在边界调节期间,Adjust需要保持高电平6个并行时钟周期,即当寄存器Adjust_count重新被赋值为1后,代表数据缓冲寄存器内的数据已经被更新,移位调整完成.Adjust置0,Detect置1.

图5 码形检测模块逻辑时序

Fig.5 Logical sequence diagram of code pattern checking module

2 仿真及实验

2.1 软件仿真

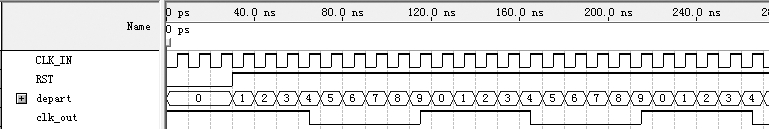

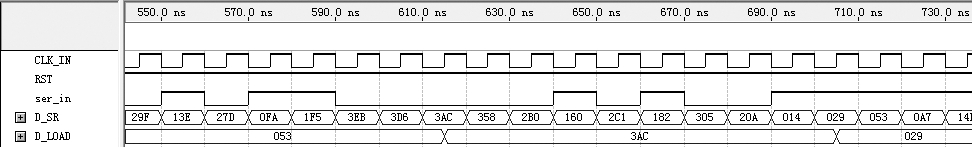

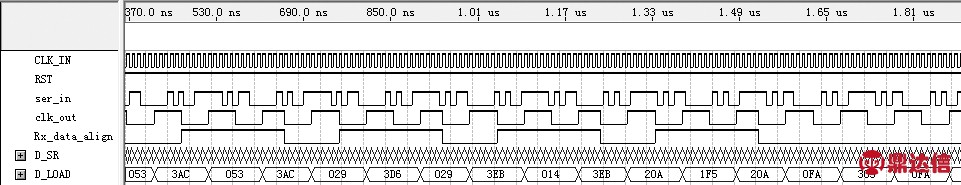

在Quartus Ⅱ 9.0开发工具中,使用Verilog语言对串并转换及字节对齐模块进行了仿真.并行时钟产生时序逻辑如图6所示.CLK_IN为串行时钟,depart为分频器,clk_out为输出并行时钟.当depart的模为4或9时,clk_out会以时钟的上升沿为基准进行翻转,从而实现串行时钟10分频的目的.字节位移调整仿真如图7~8所示.从图7中可以看出,ser_in为输入串行数据,D_SR为并行移位寄存器,D_LOAD为并行载入寄存器,在串行时钟下降沿的作用下ser_in被逐位存进D_SR中,并且在串行时钟上升沿和载入脉冲的作用下,D_SR中的并行数据会被载入到D_LOAD中.从图8中可以看出,存在4个Rx_data_align脉冲,说明并行数据存在4 bit的错位,并且载入到寄存器中的并行数据与并行时钟是同步的,在Rx_data_align脉冲存在的情况下,并行时钟的周期宽度得到了调整,输出的并行数据的字节位置也得到了相应的调整,经过4次位移调整之后,K28.5同步码得到了恢复,说明字节位移调整完成.

图6 并行时钟产生时序逻辑

Fig.6 Time sequence logic generated by parallel clock

图7 D_SR与D_LOAD时序逻辑

Fig.7 Time sequence logic of D_SR and D_LOAD

图8 字节边界调整时序

Fig.8 Time sequence adjustment of byte border

2.2 系统测试

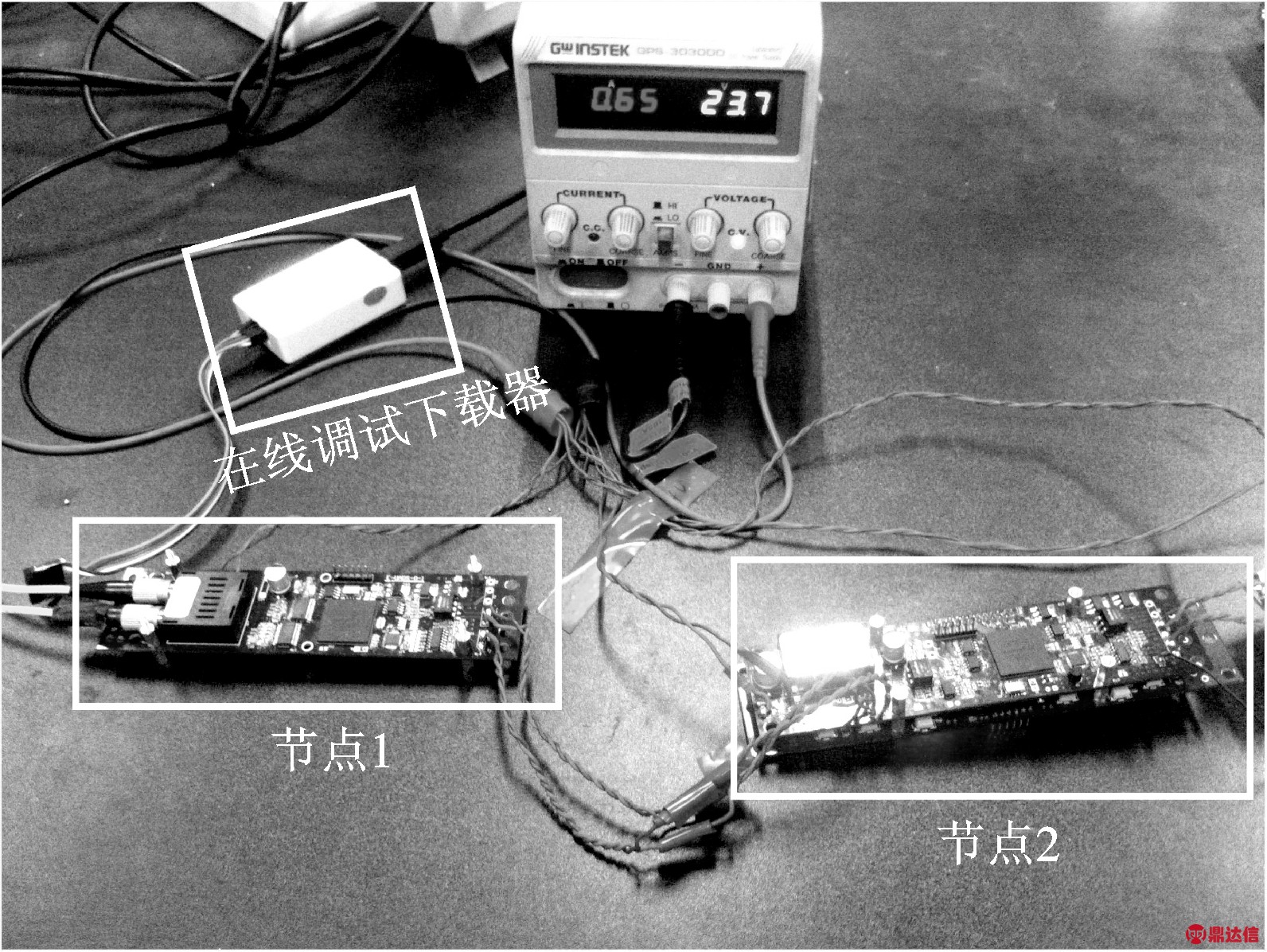

基于本文提出的串并转换以及字节对齐的方法,搭建了测试该方法的实验系统,如图9所示.

图9 实验系统

Fig.9 Experiment system

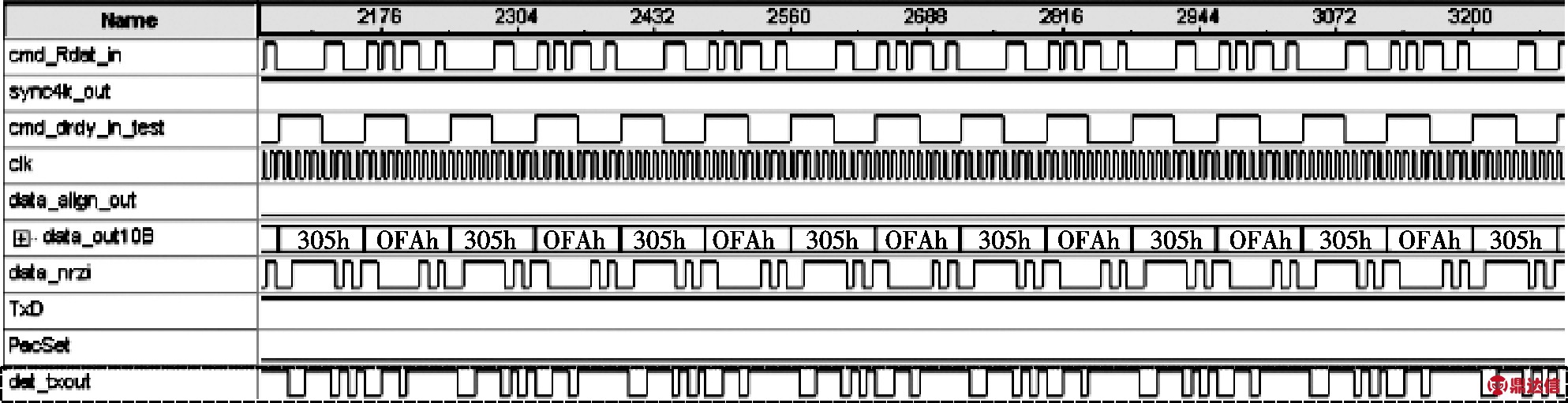

实验系统由两个节点组成,其中节点1负责将数据串化后进行发送,节点2负责串行数据的接收,节点1与节点2之间的信号传输介质采用六类双绞线(带宽为250 MHz),系统测试采用电路系统配合Quartus Ⅱ 9.0开发平台中的Signaltap Ⅱ工具进行在线调试的方法.节点1中的FPGA以16.384 MHz的串行时钟发送同步码与数据,因此串行信号的速率为16.384 Mb/s.Signaltap Ⅱ获取的数据波形如图10所示.其中data_align_out为码形检测模块的反馈信号,dataout_10B为恢复的10位并行数据.从图中可以看出,该系统可以有效地接收串行数据并恢复出完整的K28.5同步码,完成了数据的并行化与字节对齐的功能.

图10 串行数据接收测试结果

Fig.10 Results of serial data receiving test

在16.384 Mb/s的测试完成之后,又分别对32.768 Mb/s、64.384 Mb/s传输速率下的信号进行了测试,实验验证表明,数据节点1能完成信号的串化、驱动和发送功能,数据接收节点2能够完成数据时钟恢复、数据信号均衡以及字节边界对齐的功能,本测试系统在测试频率范围内性能稳定,满足设计要求.

3 结 语

本文针对高速串行通信的特点,设计了一种基于FPGA的高速串并转换和字节对齐的方案.此方案通过Verilog HDL语言编译设计串并转换模块与字节位移检测模块,可以对接收到的高速串行数据进行解串并实现字节对齐的功能.经过相关实验验证,该方案已经实现了16.384~64.384 Mb/s传输速率范围内数据解串与字节对齐的功能.本文设计串并转换与字节对齐方案在某种程度上可以替代一些现有的硬件设计方案,并且在一些低频段可以胜任硬件解串器无法完成的任务.该方案实现简单,很大程度上减少了硬件设计的复杂度,受环境影响小,方案设计灵活,能满足高速串行通信中串行数据的接收、解串和字节边界对齐的要求.