摘要:为提高数字电源回读数据的精确性、抑制噪声、降低成本,开发设计了全数字化回读系统。在本系统中,发送端的数字电源控制器通过光纤模块,按专用协议以2 kHz频率发送4种数据;接收端的数字信号采集设备接收、存储每台电源的回读数据,并标记以时间戳。系统采用有效机制保证每条数据通路的时钟同步,并提供了数据分析图形化界面。经现场测试,验证了系统的性能,达到了设计目的,使全数字化回读首次在重离子医用加速器励磁电源系统上得到成功应用。基于其较好的抗干扰性和经济性,未来可在重离子加速器中推广应用。

关键词:数字电源回读系统;高速串行数据传输;数据时间戳;海量数据处理;重离子加速器

在重离子加速器调束过程中,电源回读系统对分析电源运行状态进而优化束流品质起着至关重要的作用。对于典型的电源回读系统,每台电源配备1台电流监测设备(如DCCT零磁通电流传感器)测量电源的模拟输出,多张数据采集卡采集监测设备的电流或电压,A/D转换后,将数据集中到服务器。武威重离子医用加速器(HIMM)[1]和兰州重离子加速器(HIRFL)的已有电源回读系统[2]均为这种架构。这种方式回读数据种类单一,安装在不同机箱的数据采集卡之间较难同步,系统硬件成本较高。最突出的缺点在于,根据现场布局,数据采集卡和电流监测设备距离较远,强电磁环境下模拟信号传输易受干扰。

为解决上述问题,本文以自主研发的数字电源控制器(DPSRS)[3-6]为基础设计全新的数字电源回读系统。参照MedAustron[7]和SNS[8],DPSRS实时发送给定电流、输出电流、误差电流、电源状态4种数据。为弥补加速器因使用末端定时系统(同步定时触发系统)[9]而电源回读数据没有时间标记的缺陷,数据接收端负责为回读数据标记时间戳。

1 数字电源回读系统硬件设计

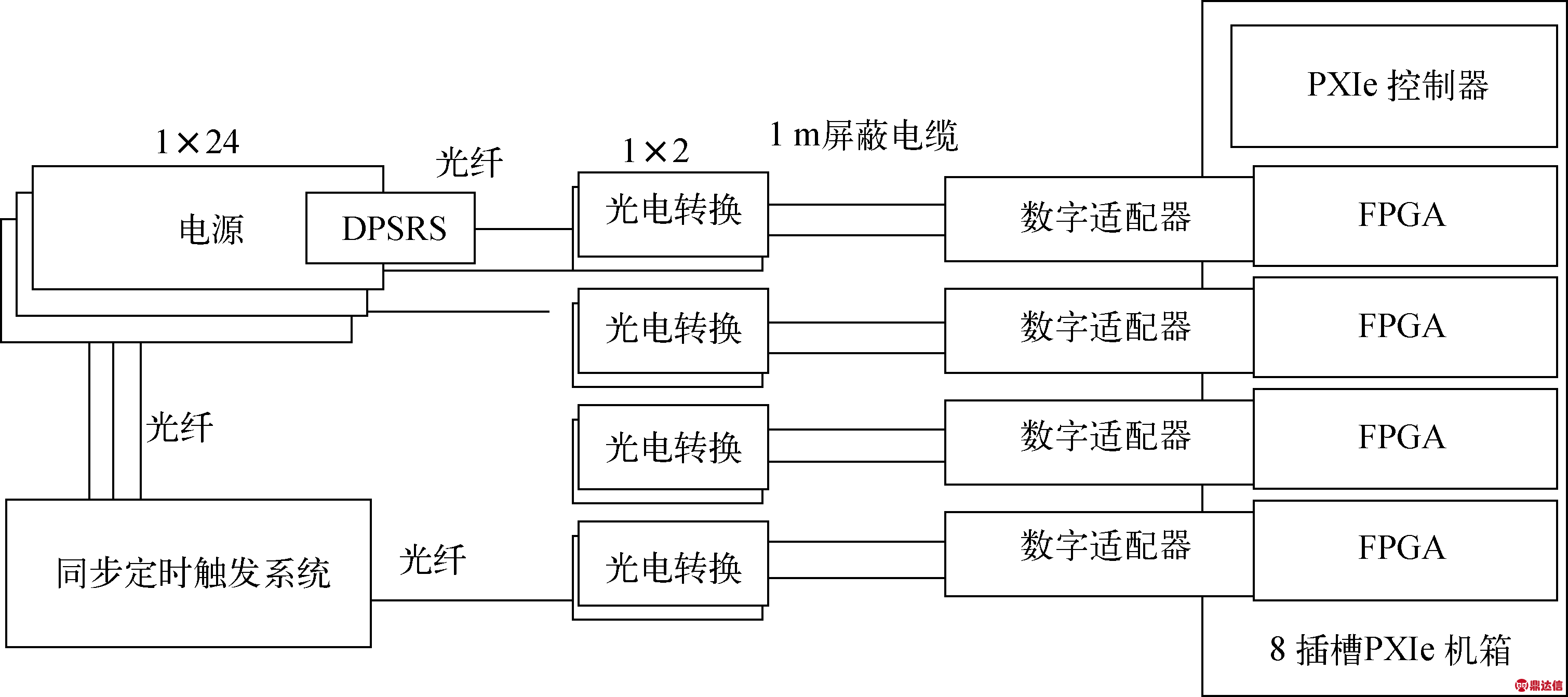

与已有的电源回读系统采用DCCT和NI PCI 6133卡采集电源的模拟输出不同,新数字电源回读系统传输的均为数字信号,因此需对系统进行全新的软硬件设计。DPSRS的数据发送接口采用HFBR-2522Z光发射器,每24台电源的回读光纤接到1台自主研发的多路光电转换器。回读光纤采用等长POF光纤,根据重离子加速器现场布局,每条光纤长度不超过40 m。数据接收处理设备是1套配备嵌入式控制器(NI PXIe-8840)、4块FPGA板卡(NI FlexRIO 7975R)的PXIe机箱(NI PXIe-1082)。每块FPGA板卡接1块数字适配器模块(NI 6581B),用于提供多路数字I/O通道,每块数字适配器通过屏蔽电缆连接2台光电转换器。因此,该套接收设备可处理多达192台电源的回读数据。同时,接收设备接入1路同步定时触发系统信号,以便保存触发事例并标记时间戳供数据分析时使用。系统硬件架构示于图1。

2 数字电源回读数据传输协议

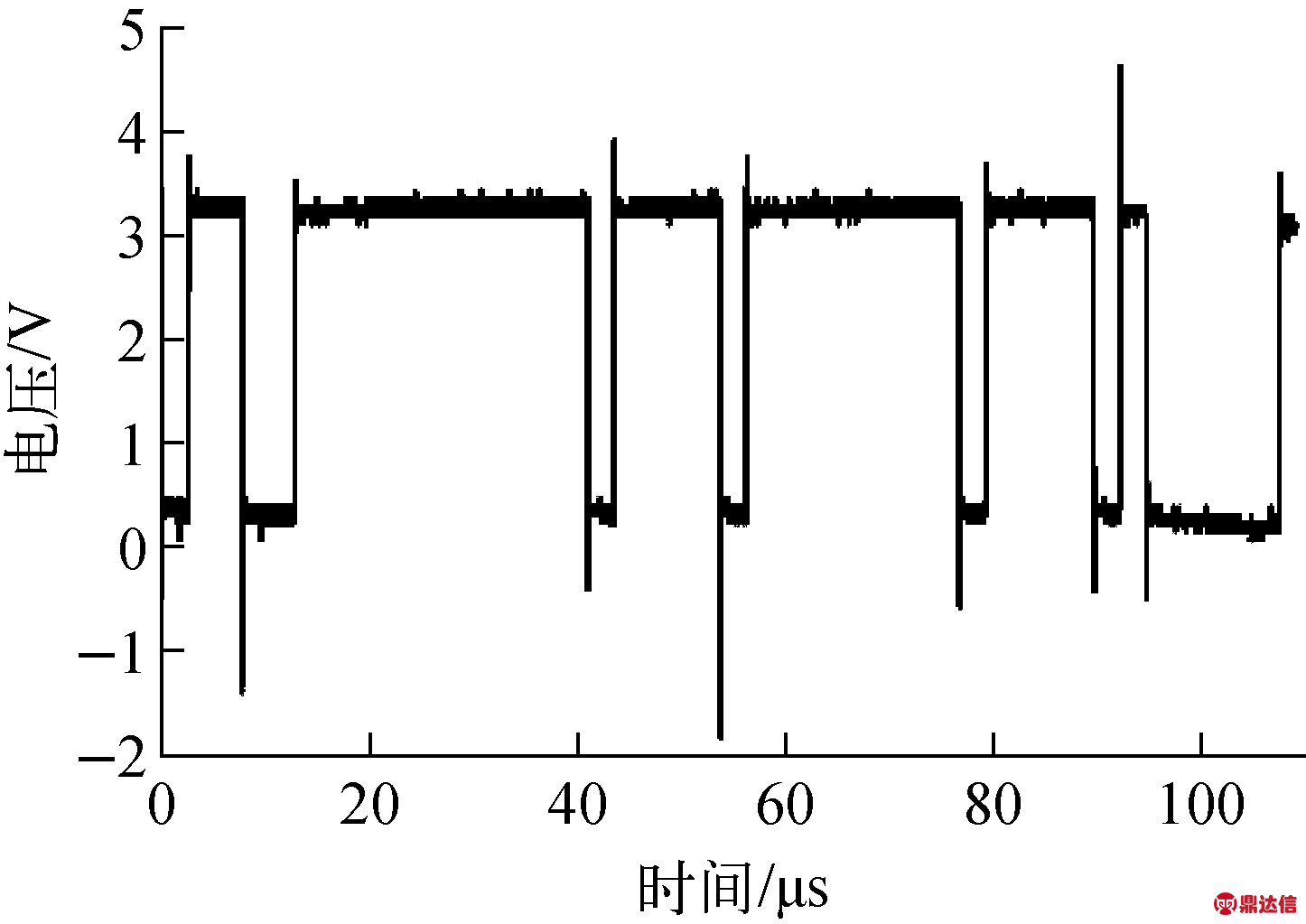

为了保证高速串行数据传输的高效率和低差错,设计的数据传输协议为:起始位,1 bit;数据种类,4 bit;数据值,32 bit;校验位,4 bit;停止位,1 bit。数据传输波特率定为390.625 kbps。采用4位循环冗余CRC-4校验[10],其生成多项式g(x)=x4+x+1来自ITU-T G.704标准[11]。从理论上讲,CRC-4能检出所有单个误码、离散的2个误码、奇数个误码、4位及以下突发误码,对5位及以上突发误码的检出概率是87.5%和93.75%。图2为示波器记录的按协议传输的电源状态数据。

3 数字电源回读系统软件设计

3.1 数字电源控制器数据发送设计

DPSRS根据给定量和反馈量进行PID运算产生高精度PWM波形控制电源功率器件,同时调节运算的中间结果及电源状态实时存储在SDRAM中。调节运算和回读数据发送是FPGA硬件逻辑的两个并行任务,用VHDL硬件描述语言实现。回读数据的发送使用状态机机制,在2 kHz定时器的驱动下读取并发送SDRAM寄存器数据,每个发送周期依次发送给定电流、回读电流、误差电流和电源状态。

图1 数字电源回读系统硬件架构

Fig.1 Hardware architecture of digital power supply measurement system

图2 示波器记录的电源状态数据

Fig.2 State data captured by oscilloscope

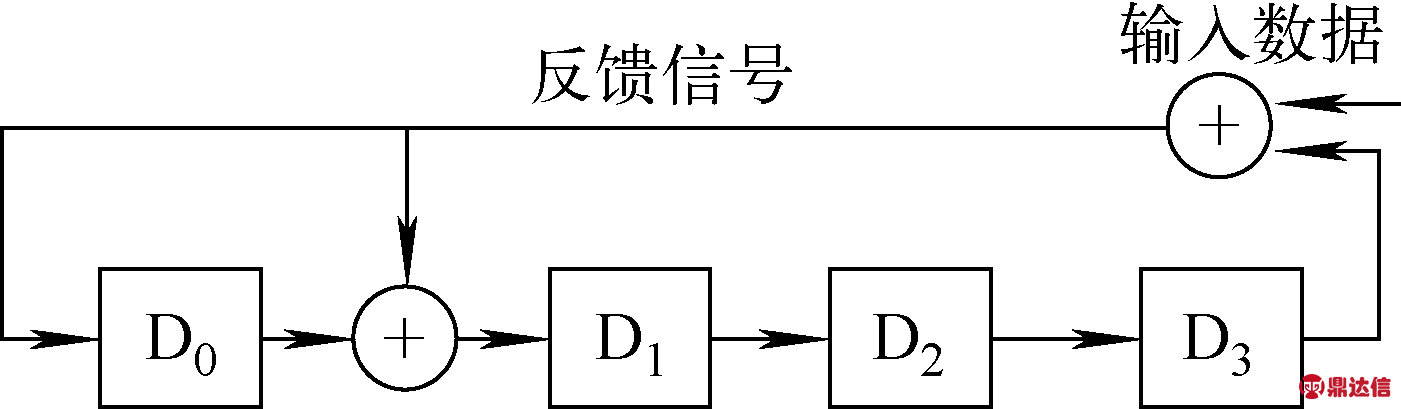

CRC-4校验码用线性反馈移位寄存器得到(图3),4个D触发器初始值为0,生成多项式各项系数为1时有反馈,系数为0时无反馈,36位数据由高到低按位输入,输入完成后D触发器中的值即为校验码值。

图3 计算CRC-4校验码值的逻辑图

Fig.3 Logic diagram for calculating CRC-4 code

3.2 数据接收处理程序设计

数据接收处理程序分为FPGA程序和控制器程序,图4为系统数据流图。每块FPGA板卡并行接收、解析48路电源数据(其中1块多接收处理1路同步触发数据),并为每个数据点标记时间戳;FPGA板卡之间和板卡的每条数据通路由特殊机制实现时钟同步。FPGA处理后的每个回读数据及时间戳为2个U64(64位无符号整数),具体格式为:63~32位,数据值;31~12位,固定值20h’64610;11~4位,通道编号;3~0位,数据种类;63~32位,时间秒的整数部分;31~20位,保留;19~0位,时间秒的小数部分。数据通过直接内存访问(DMA)[12]传给控制器,控制器程序负责数据的分类存储及系统全局配置。

图4 系统数据流图

Fig.4 System data flow chart

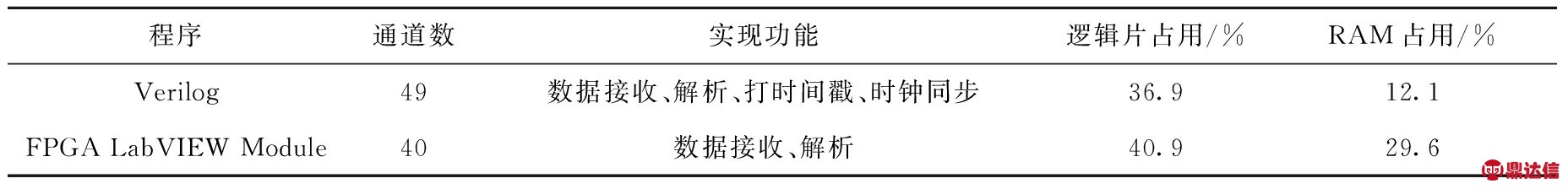

接收程序使用LabVIEW编写。LabVIEW提供了FPGA Module[13]用于自定义FPGA逻辑,易于使用,侧重应用级编程。但在本工作中,每块FPGA程序涉及多达49路数字信号的采样、协议解析、时间标记、时钟同步等底层比特流操作,通过复制的方式显式地并行化程序会使得代码难以维护,过多的控件使用会导致FPGA资源利用线性增加。而Verilog程序直接对硬件电路进行操作,减少了LabVIEW控件使用。表1为FPGA LabVIEW Module与Verilog程序编译结果的对比,可看出,操作更多路数据、实现更复杂的功能,Verilog程序编程反而占用更少的FPGA资源。因而从程序的高效性、灵活性和可维护性出发,应使用Verilog硬件描述语言对FPGA进行编程,实现49路数据接收处理操作和时钟同步功能。Verilog程序封装为组件级知识产权 (CLIP),FPGA VI将CLIP放在一单周期定时循环 (SCTL)中,SCTL提供高吞吐量和高精确的定时控制,保证其内程序在特定的FPGA时钟周期内执行完毕。

1) FPGA接收回读数据及时钟同步

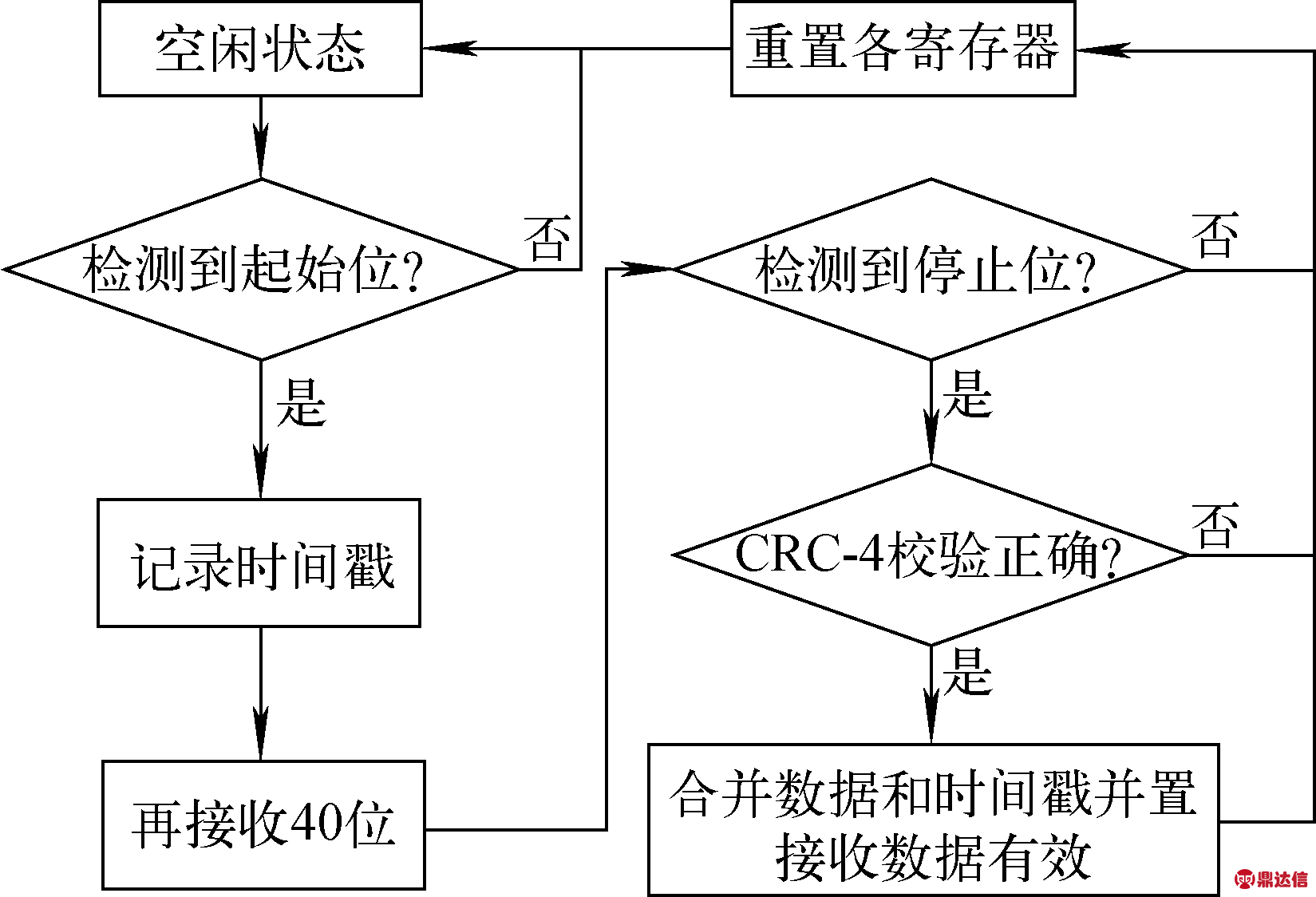

FPGA接收处理每路电源数据的流程示于图5。以SCTL设置的100 MHz时钟频率对管脚中输入的数字信号进行采样,每位数据采样256次,结果取最中间1次。理论上100 MHz系统时钟可标记精度为10 ns的时间戳,考虑到实际应用需求,系统中时间戳存储精度为1 μs。

表1 FPGA LabVIEW Module与Verilog程序编译结果对比

Table 1 Comparison of FPGA LabVIEW Module and Verilog program

图5 每路电源回读数据接收处理流程

Fig.5 Flow chart of data receiving and processing of one channel

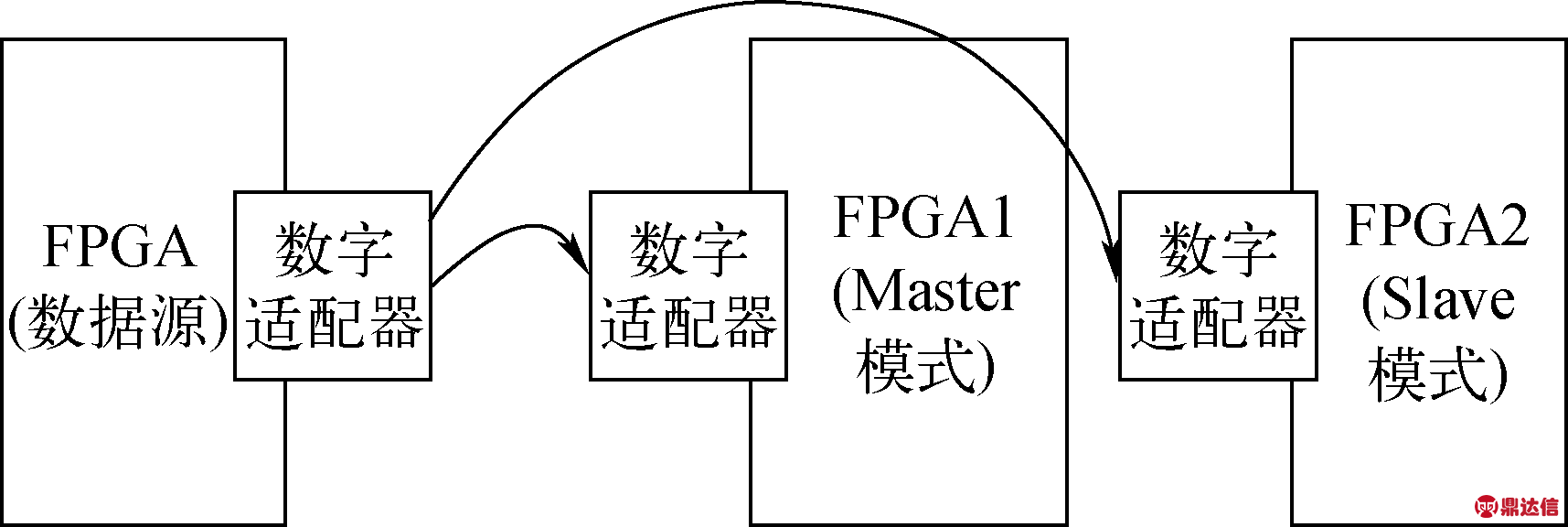

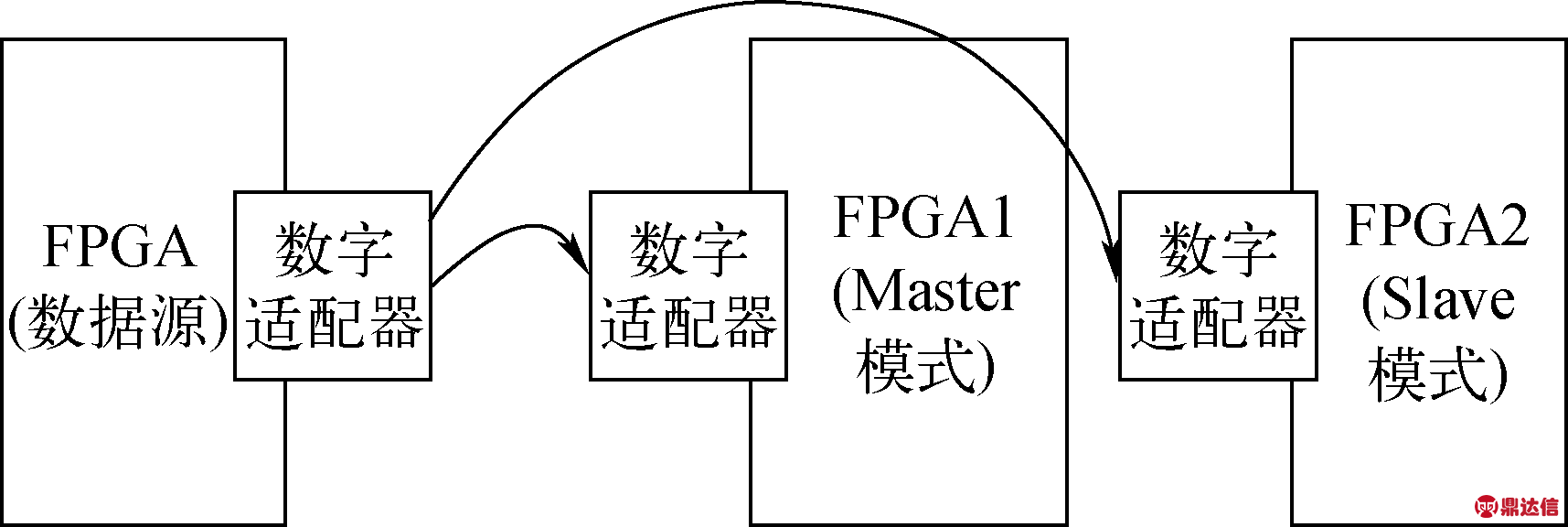

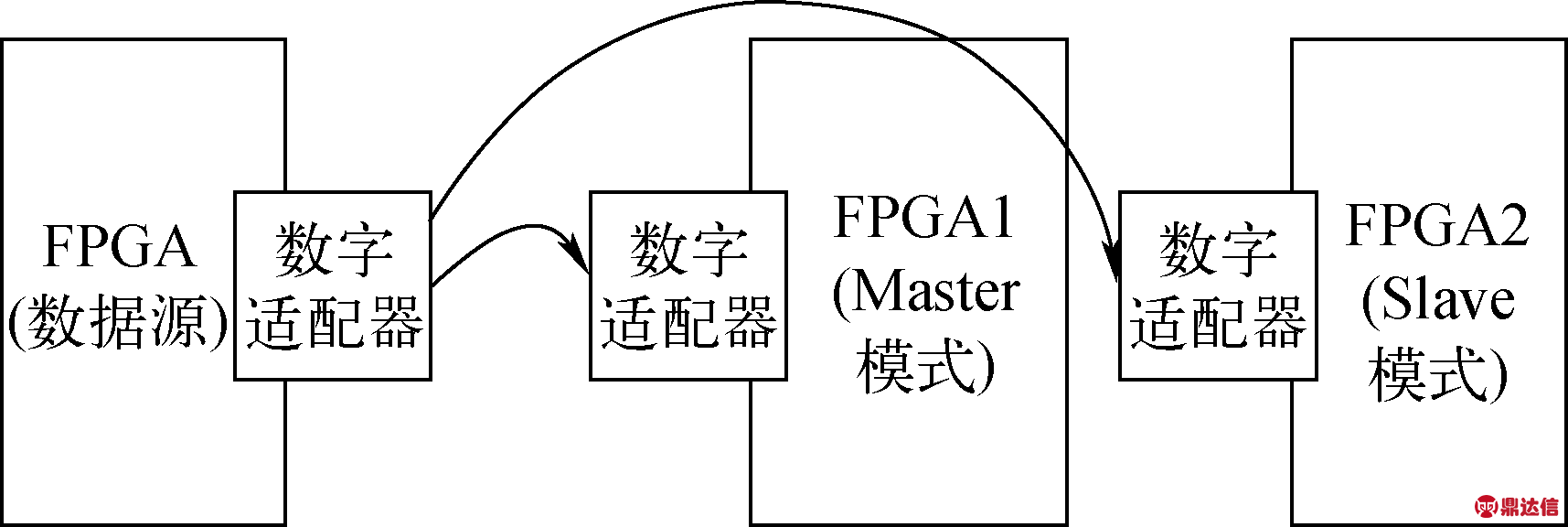

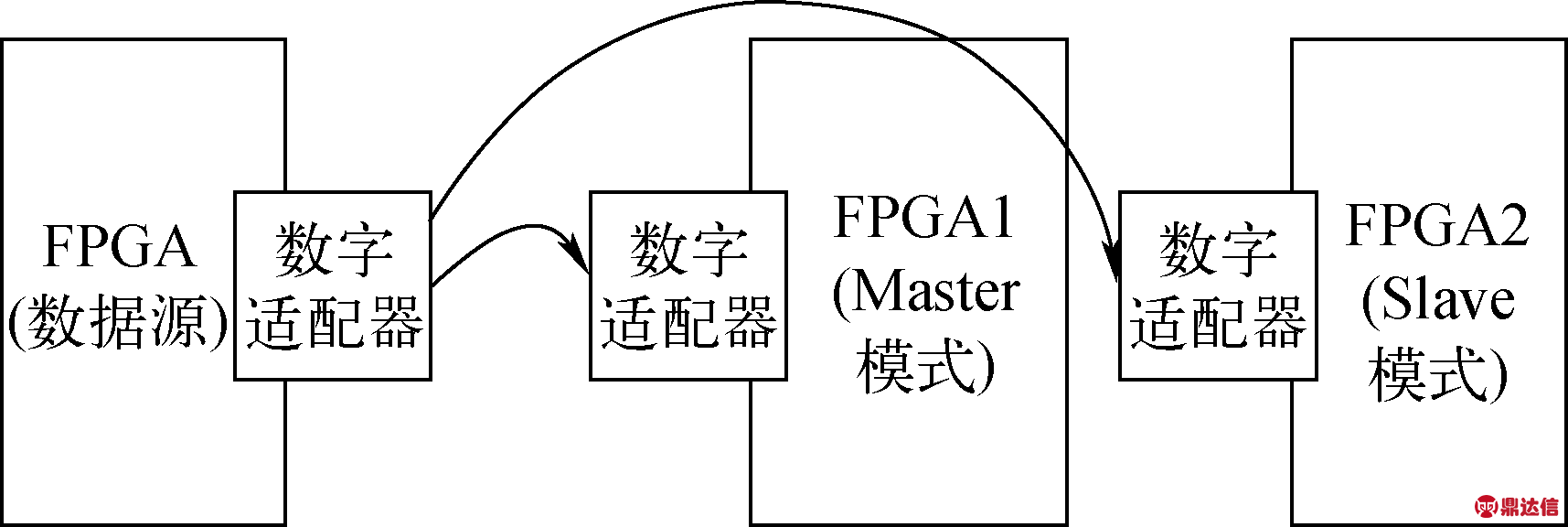

Signal line模块对应上述流程,每块FPGA有48个Signal line模块,FPGA时钟同步机制如图6所示。通过以下机制保证接收设备各FPGA各数据通道的时钟同步:1) Timer模块的100 MHz主时钟由PXIe机箱背板的PXI_10 Mclk 10倍频得到,保证各FPGA主时钟的同步,Timer模块得到10 ns分辨率的绝对时刻并分发给各Signal line模块;2) 各FPGA设置为相同的本地时间,1块FPGA指定为Master主模式,其余3块指定为Slave从模式。程序启动后,Master FPGA的Timer是自由时钟,每计时到整数秒时触发Synchronization模块,发送负脉冲到背板的PXI_TRIG0线上,该脉冲为PPS;而Slave FPGA的Synchronization监测PXI_TRIG0线上的负脉冲并转发给Timer,Timer时间秒的整数部分根据PPS计算,小数部分则自由计数并在PPS到来时清零,以此来确保板间Timer时间计数的同步。如此,每台电源回读数据的时间标记是同步的,实现了电源系统内的数据时钟同步。该机制可扩展性强,未来新增1块定时板卡接入中央定时系统,取代Master FPGA发送PPS到PXI_TRIG0,所有FPGA设置为Slave模式,即可实现数字电源回读系统在加速器系统级的时钟同步(图7)。

2) 控制器处理和存储回读数据

在数据获取系统中,FPGA和控制器是生产者与消费者的关系。本系统满载情况下,每秒产生的数据高达24.6 MB,控制器必须匹配FPGA产生数据的速度和传输带宽,避免FIFO溢出造成数据丢失。本系统采取以下措施保证控制器对数据的高效处理。

(1) DMA FIFO的使用。FPGA和控制器双方不需要CPU的参与,DMA引擎通过PXIe控制总线实现数据在内存中的批量传输。

图6 FPGA时钟同步机制

Fig.6 FPGA synchronization mechanism

图7 FPGA时钟同步机制接入加速器中央定时系统

Fig.7 FPGA synchronization mechanism accessing accelerator central timing system

(2) 面向对象和异步调用。使用LabVIEW中的面向对象LVOOP技术[14]将数据存储封装为Logger类,控制器每隔5 ms获取4个DMA FIFO中的数据并异步调用Logger对象来保存数据。数据存储成为独立进程,不与其他模块竞争系统资源,处理速度快。

(3) 数据文件结构的设计。TDMS是NI公司新推出的数据管理系统[15],以二进制存储数据兼具关系型数据库优点。回读数据按类型保存到同1个TDMS文件的4个通道,满108个数据点再创建另1个文件。程序同时操作的文件句柄数为1,将极大地减少操作系统调用,提高数据存储速度。

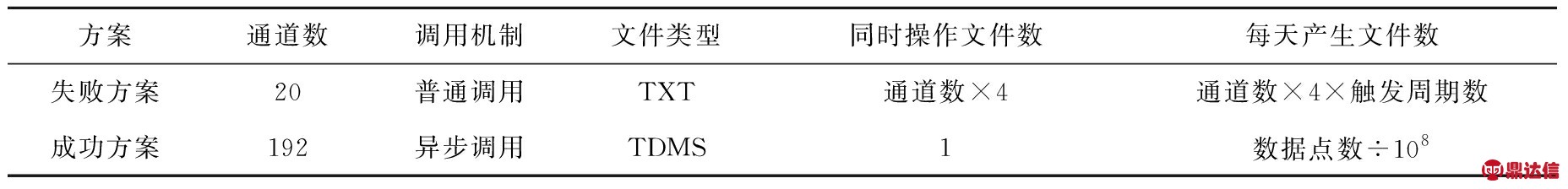

系统设计之初未用独立进程和TDMS文件格式,而是在1个进程中同时操作多个TXT文件,结果20路数据产生严重溢出,表2为控制器数据存储方案的比较。

表2 控制器数据存储方案的比较

Table 2 Comparison of data storage method in controller

4 数字电源回读系统验证及应用

4.1 同步性验证

图8 FPGA时钟同步机制验证方法

Fig.8 Verification method of FPGA synchronization mechanism

图9 FPGA时钟同步机制验证结果

Fig.9 Verification result of FPGA synchronization mechanism

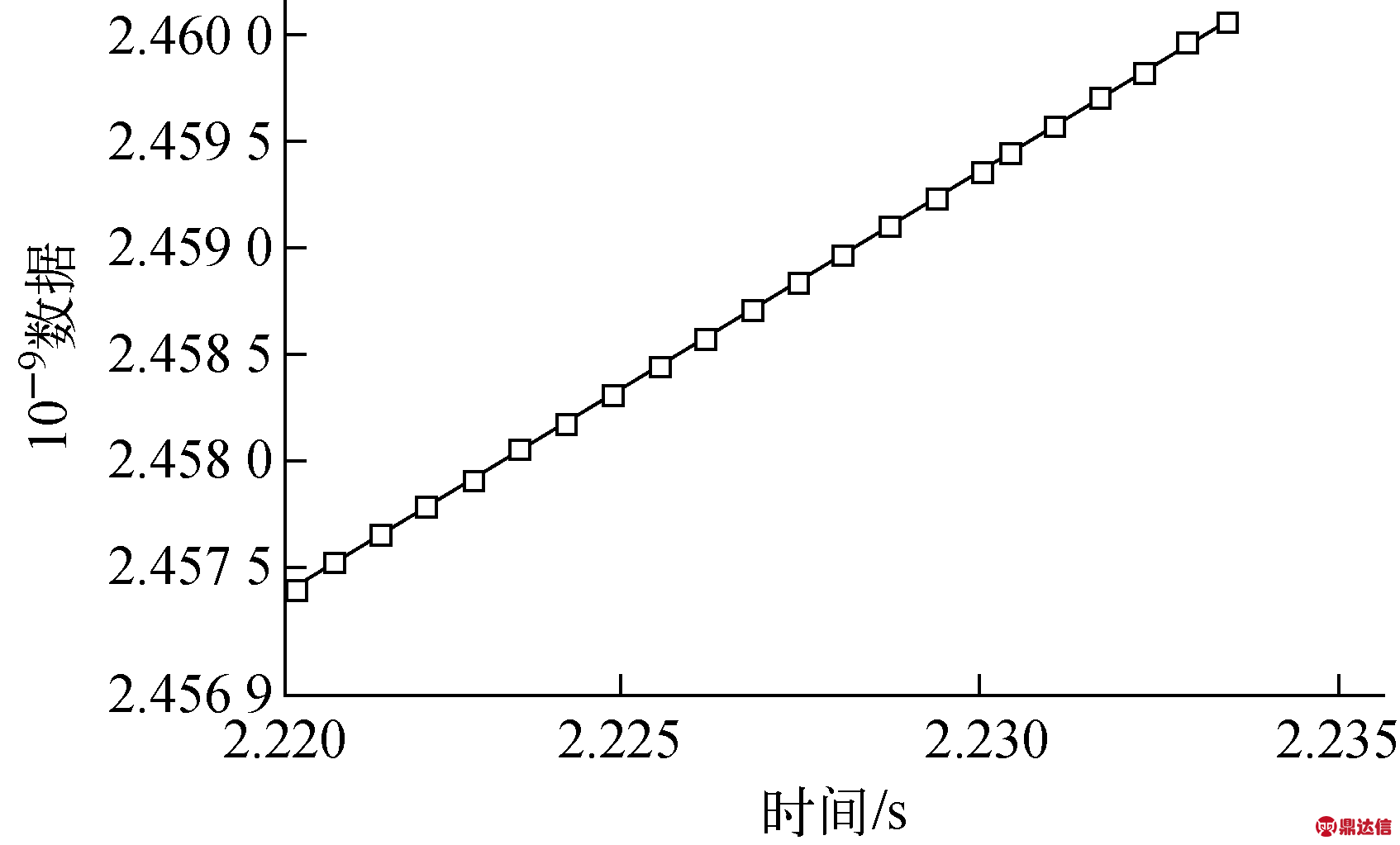

图8为FPGA时钟同步机制验证方法。1块FPGA产生随时间递增的数据,按电源回读数据传输协议从48路I/O口同时发出,其中24路接入接收设备的Master FPGA上,另24路接入Slave FPGA。从存储的48路数据中任意选择多路显示在XY图上,发现各通道的数据点严格重合在一起(图9),说明接收设备对不同I/O通路同时到达的数据标记的时间戳是相同的,各数据通路的同步性得到验证。

4.2 系统应用

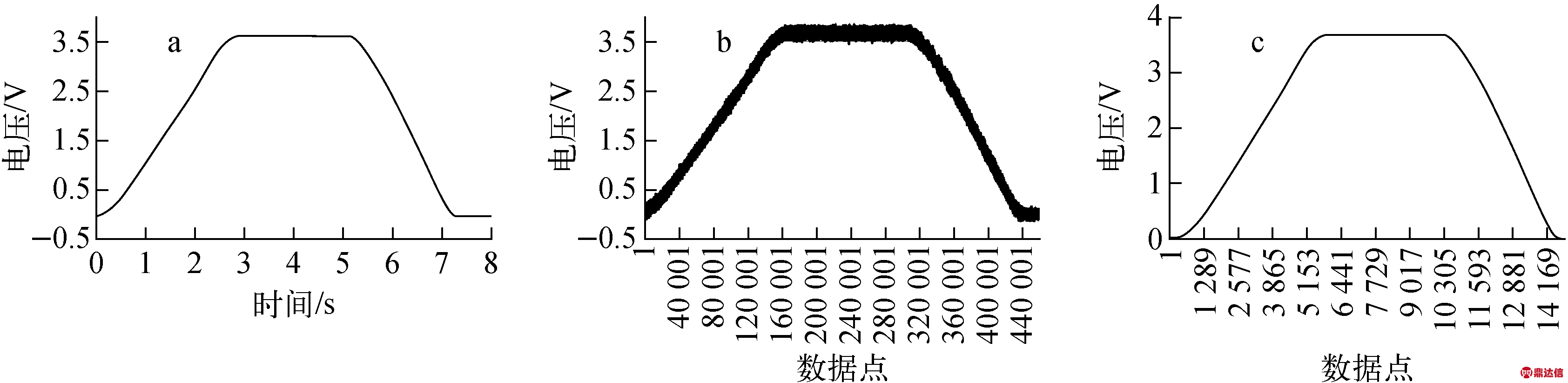

数字电源回读系统于2017年3月在HIMM武威现场安装调试完毕,作为辅助系统运行,接入同步加速器和高能束运线脉冲数字电源共108台,平均每天保存数据超过100 GB。原电源回读系统由于长距离传输电源输出模拟量,数据噪声大;而新系统中,回读数据从发送、传输到接收均为数字信号,数据噪声问题得到解决。从2017年3月30日对HIMM高能束运线二极铁电源HIMMWW53PS0D5某触发周期的输出电压实测结果(图10)可看出,与原电源回读系统相比,本系统的回读数据几乎无噪声,与示波器记录值较为一致。

本文介绍的数字电源回读系统不仅能帮助调束人员分析电源的同步性,还能提供精确的历史数据用于故障诊断。如2017年3月11日22:52:40,HIMM同步加速器的二极铁电源HIMMWW44PS0D发生故障,用系统提供的数据分析界面可清楚地看到故障发生时的回读数据波形及其局部放大部分(图11),帮助工作人员分析定位故障原因。

图10 示波器(a)、原有回读系统(b)、本文回读系统(c)记录的同一电源输出电压波形

Fig.10 Output voltage waveforms recorded by oscilloscope (a), in-use system (b) and introduced system (c)

图11 发生故障时电源回读数据波形(a)和局部放大数据波形(b)

Fig.11 Measurement data waveform (a) and its amplifying part (b) of failure power supply

5 结论

本文介绍了重离子加速器数字电源回读系统,利用数字电源控制器自身资源,为加速器调束人员提供了多种带同步时间戳的高精度电源回读数据,弥补了现有电源回读系统数据单一、抗干扰能力弱、回读数据无同步时间戳、系统成本高的缺点。新系统的每部分均采用了高效的设计思路,结构简单、易于部署,未来可在重离子加速器控制系统中推广应用。