摘要 针对自由电子激光装置(Free Electron Laser, FEL)对束流位置测量的需求,研制了可同时用于条带束流位置检测器(Stripline Beam Position Monitor, SBPM)和腔式束流位置检测器(Cavity Beam Position Monitor, CBPM)信号处理的数字化束流位置信号处理器(Digital Beam Position Measurement processor, DBPM)。该处理器为一体化的嵌入式结构,以现场可编程逻辑门阵列(Field Programmable Gate Array, FPGA)为系统核心,采用分布式的实验物理及工业控制系统(Experiment Physics and Industrial Control System, EPICS)进行远程数据交互。处理器对SBPM和CBPM系统的测试分辨率在0.5nC流强时分别达到4μm和0.4μm,达到设计指标,成功应用于大连相干光源(Dalian Coherent Light Source, DCLS),并将应用于上海软X射线自由电子激光装置(Shanghai X-ray Free Electron Laser, SXFEL),是国内首台自主研制成功并实现工程应用的DBPM处理器。

关键词 自由电子激光,束流位置信号处理器,条带束流位置检测器,腔式束流位置检测器,大连相干光源,上海软X射线自由电子激光装置

自由电子激光(Free Electron Laser, FEL)具有高亮度、高相关性、短脉冲、频率连续可调等优点,在多个学科上有重要的应用。当前国际和国内已有多个大型FEL装置建成或在建,如美国斯坦福直线加速器中心(Stanford Linear Accelerator Center, SLAC)的第二代直线加速器相关光源(Linac Coherent Light Source-II, LCLS-II)、瑞士自由电子激光(SwissFEL)和欧洲X射线自由电子激光(European X-ray FEL, EuropeanXFEL)、日本紧凑型自由电子激光(SPring-8 Angstrom Compact free electron Laser, SACLA)、韩国浦项X射线自由电子激光(Pohang Accelerator Laboratory XFEL, PAL XFEL)、国内的大连相干光源(Dalian Coherent Light Source, DCLS)与上海软X射线自由电子激光装置(Shanghai X-ray Free Electron Laser, SXFEL)。上海光源承担了DCLS和SXFEL的建设工作,于2016年开始安装调试。自由电子激光加速器由直线段与波荡器两部分组成,束流位置测量在直线段采用条带束流位置检测器(Stripline Beam Position Monitor, SBPM),波荡器采用腔式束流位置检测器(Cavity Beam Position Monitor, CBPM)。DCLS与SXFEL的指标要求在0.5nC电荷量,重复频率50Hz的情况下,SBPM分辨率达到10μm,CBPM分辨率达到1μm。

测量系统由安装在加速器真空管道上的探头和相应的信号处理电子学组成。束流位置检测器(Beam Position Monitor, BPM)的信号处理器是FEL关键的束测设备之一,对保障FEL的高分辨率束流位置测量至关重要,同时其数量比较多。PAL XFEL和LCLS-II采用SLAC[1]研制的BPM信号处理器;SwissFEL和EuropeanXFEL[2]采用PSI研制的处理器。上海光源已经运行了多年,积累了比较丰富的BPM系统使用经验[3‒8],并持续开展了处理器的研制工作[9‒13],已研制成功用于储存环的数字化束流位置信号处理器(Digital Beam Position Measurement processor, DBPM),逐圈位置分辨率可达亚微米。与此同时,进行了储存环逐束团束流位置信号处理[14]与CBPM信号处理的研究[15‒17]。基于以上工作的积累,以DCLS与SXFEL的建设为契机,开始自行研制用于DCLS和SXFEL的单次通过型DBPM信号处理器。

1 背景

BPM系统如图1所示,包括BPM探头和信号处理两部分,其中信号处理包括射频信号调理、模拟/数字转换(Analog-to-Digital Converter, ADC)、数字信号处理和数据采集与控制。

图1 BPM系统框图

Fig.1 Block diagram of BPM system

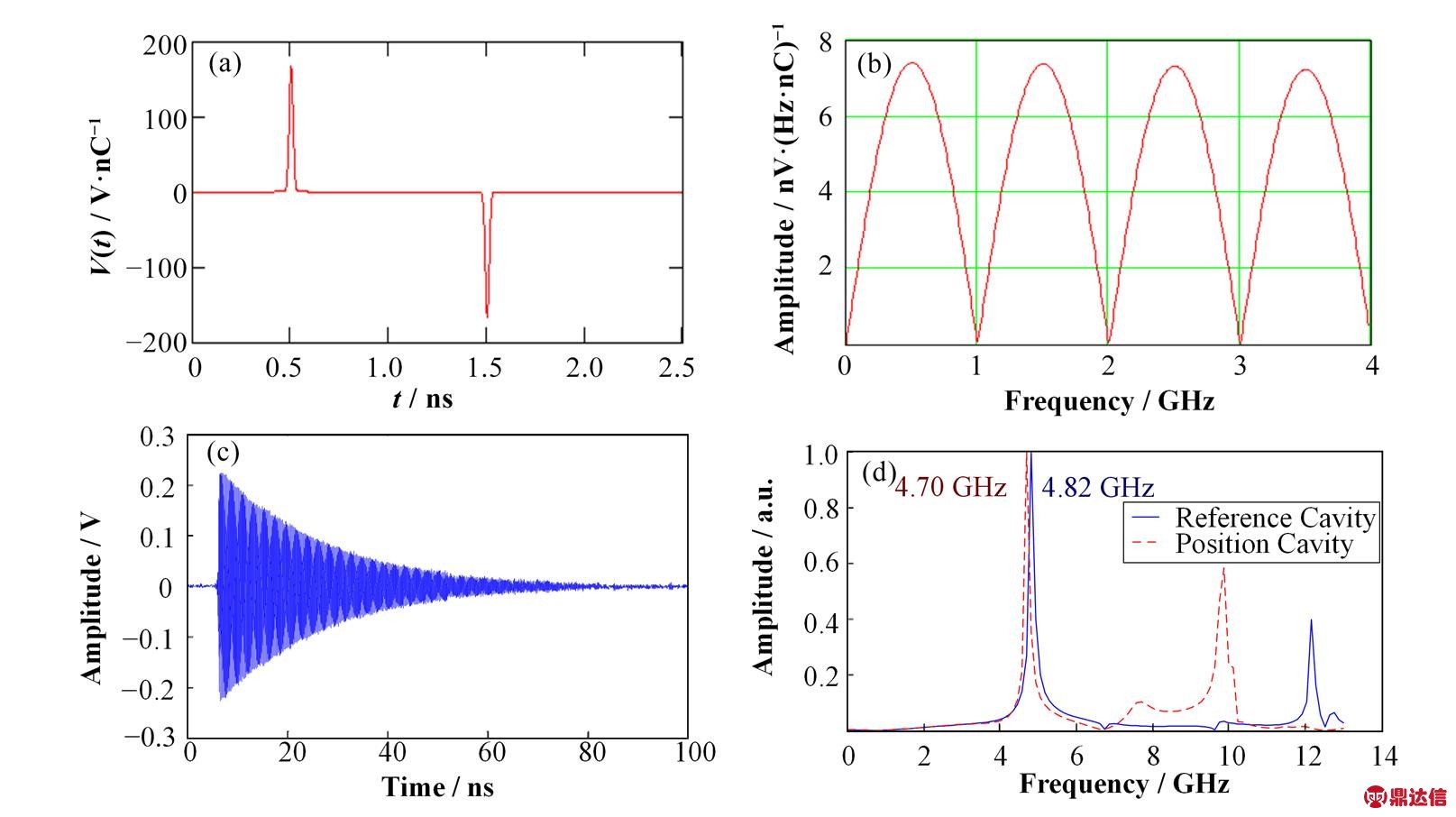

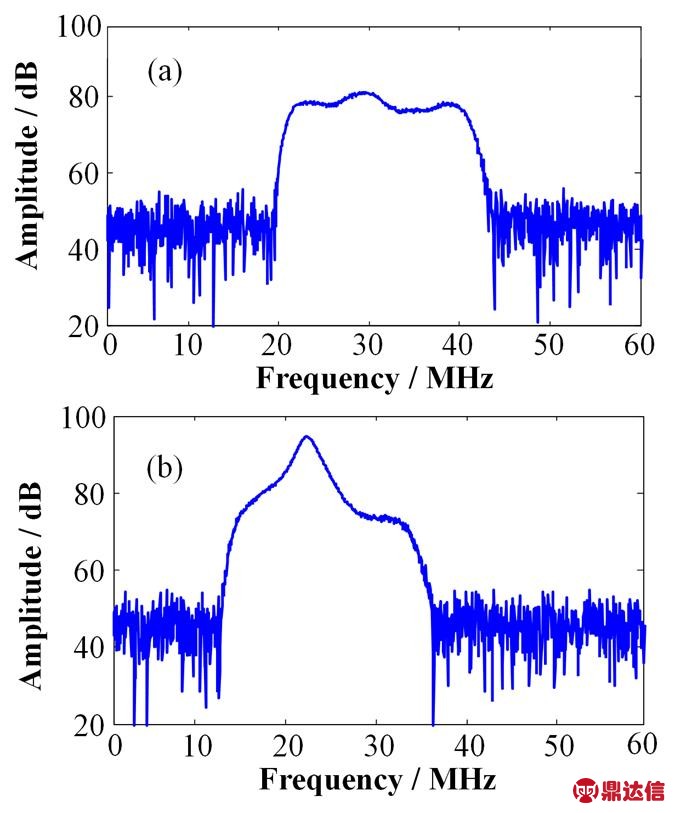

根据不同的应用对象有不同种类束流位置测量的探头,FEL主要有用于直线加速器部分的SBPM探头和波荡器部分的CBPM探头。SBPM和CBPM输出信号的时域波形与频域波形如图2所示。束流通过时,SBPM输出双极脉冲信号,从频域上看是宽带的梳状周期信号;CBPM时域信号呈指数衰减,频域是高频窄带信号。

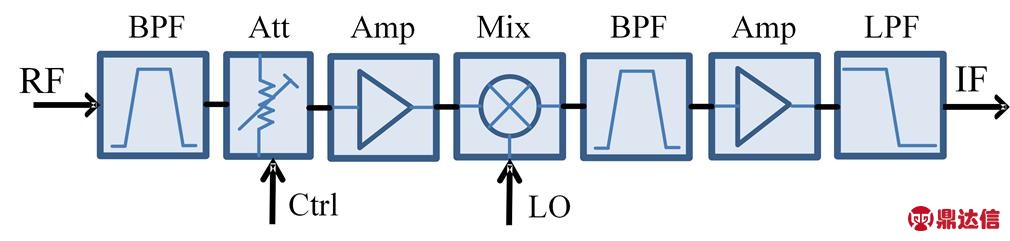

信号调理部分将BPM探头输出的宽带或窄带信号调理成适合ADC采样的中频信号,处理流程一般如图3所示。窄带滤波器(Band Pass Filter, BPF)提取感兴趣部分信号,然后将高频信号(Radio Frequency, RF)与本振信号(Local Oscillator, LO)混频(Mix)至中频信号(Intermediate Frequency, IF),此外还有相关的信号放大(Amplifier, AMP)与低通滤波(Low Pass Filter, LPF)等。

SBPM输出4通道束流感应宽带信号,直接利用DBPM进行窄带滤波,数字化采样及运算后,提取各通道信号幅度,进行差比和运算获得束流位置信息。CBPM输出3通道束流信号是中心频率达几个GHz的高频窄带信号,信号先经过射频前端下变频之后再输入DBPM,提取信号幅度与相位信息并计算束流位置。为了使DBPM能同时满足SBPM与CBPM信号处理,同时也为将来环形加速器的应用做准备,DBPM采用同一硬件结构。模拟信号处理前端部分将输入信号处理为中心频率500MHz、带宽20MHz左右的窄带信号;4通道16位ADC,采样频率约120MHz;采样时钟可在内置时钟或外接时钟间切换;利用现场可编程门阵列(Field Programmable Gate Array, FPGA)进行数字信号处理;控制系统采用Linux EPICS。

图2 SBPM输出信号波形(a)及频谱(b)、CBPM输出信号(c)及频谱(d)

Fig.2 SBPM output signal (a) and the spectrum (b), CBPM output signal (c) and the spectrum (d)

图3 射频信号调理框图

Fig.3 Block diagram of RF conditioning

DBPM处理器架构可分为背板总线式和一体式。采用背板总线集成度高更紧凑,而且更便于同步采样,LCLS-II和Swiss FEL/EXFEL设计的处理器就采用了Micro TCA总线架构。一体式处理器则可独立工作,使用灵活,符合分布式系统架构,NSLS-II及IT公司的Libera Electron和Brilliance采用该架构。本设计采用一体化结构,保持与上海光源当前使用Libera Electron和Brilliance保持一致。

综上所述,该处理器结构设计如图4所示。DBPM由射频子板和数字母板组成。射频子板包含4通道输入,输入信号经调理后进行ADC数字化 采样,采用复杂可编程逻辑器件(Complex Programmable Logic Device, CPLD)进行射频板远程控制;数字母板以FPGA和ARM CPU为核心进行信号处理、数据采集及系统控制。

图4 处理器结构设计

Fig.4 Architecture design of DBPM

2 设备开发

开发内容包括三部分:硬件、FPGA及CPLD上的固件(Firmware)、上层应用软件EPICS IOC及EDM面板。

12.1 硬件开发

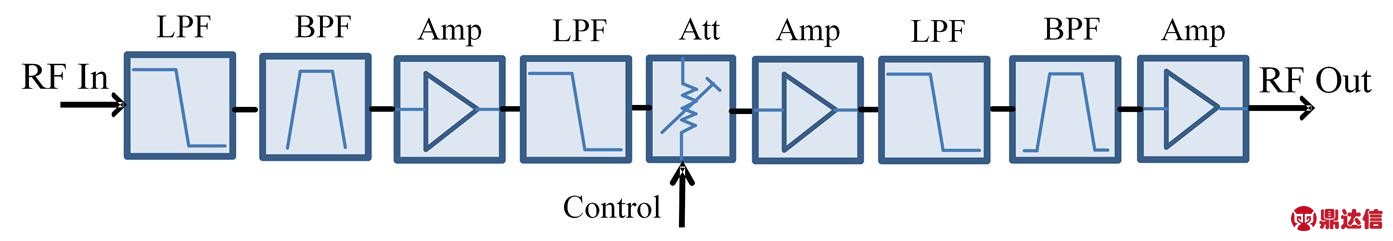

SBPM输出4个通道位置信号,CBPM输出由两通道位置信号和一个通道参考信号,单个通道的射频信号处理流程如图5所示。输入信号经过一级低通滤波器滤除高频信号,然后经过中心频率为500MHz,带宽为12MHz的一级窄带声表滤波器、一级放大(约20dB)、二级低通滤波、31dB数字可调衰减器、二级放大器、三级低通滤波器、二级窄带滤波器、三级放大器等。

图5 射频信号处理链

Fig.5 RF signal processing chain

ADC芯片采用美国Analog Devices公司AD9265芯片,该芯片为16位,最高采样率125MHz,带宽0~650MHz。采样时钟由内置晶振或外接时钟提供。射频子板的远程配置采用美国XILINX公司的CPLD芯片XC2C256,数字母板通过SPI总线与CPLD通信,对输入时钟、可调衰减值等参数进行设置。图6为DBPM的ADC采样的SBPM与CBPM单通道信号频谱图,SBPM输出信号已经滤成窄带信号,CBPM输出信号频谱的峰值处为下变频后的信号中心频率。

图6 射频前端处理及ADC采样后的SBPM (a)和CBPM (b)信号

Fig.6 ADC sampled data from SBPM (a) and CBPM (b) inRF front-end

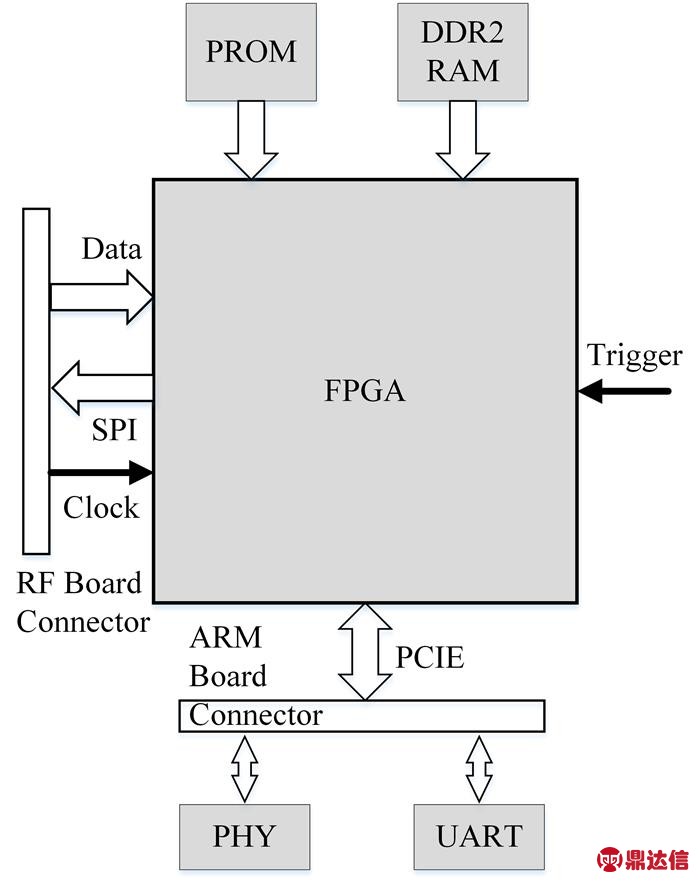

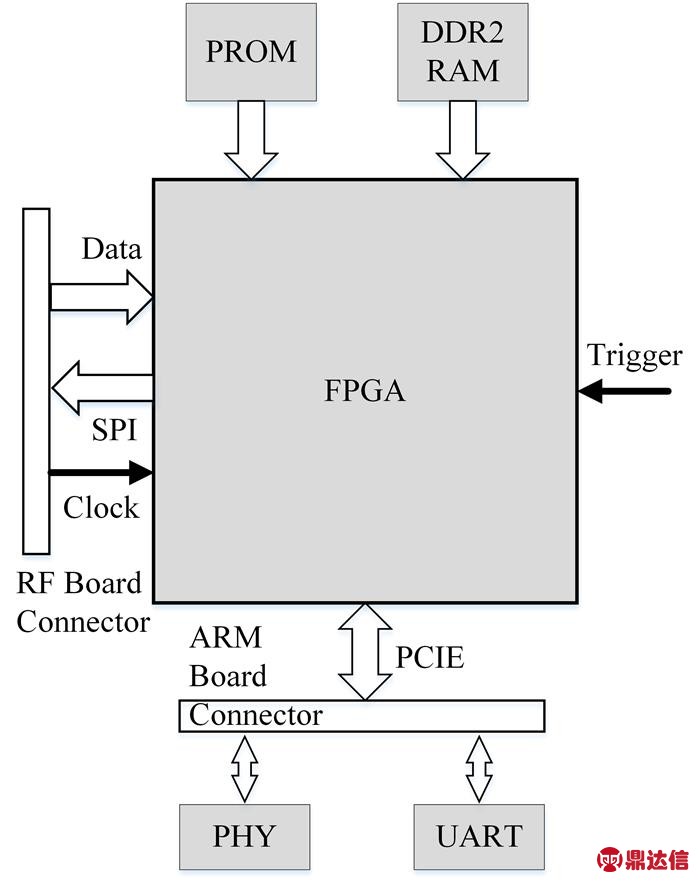

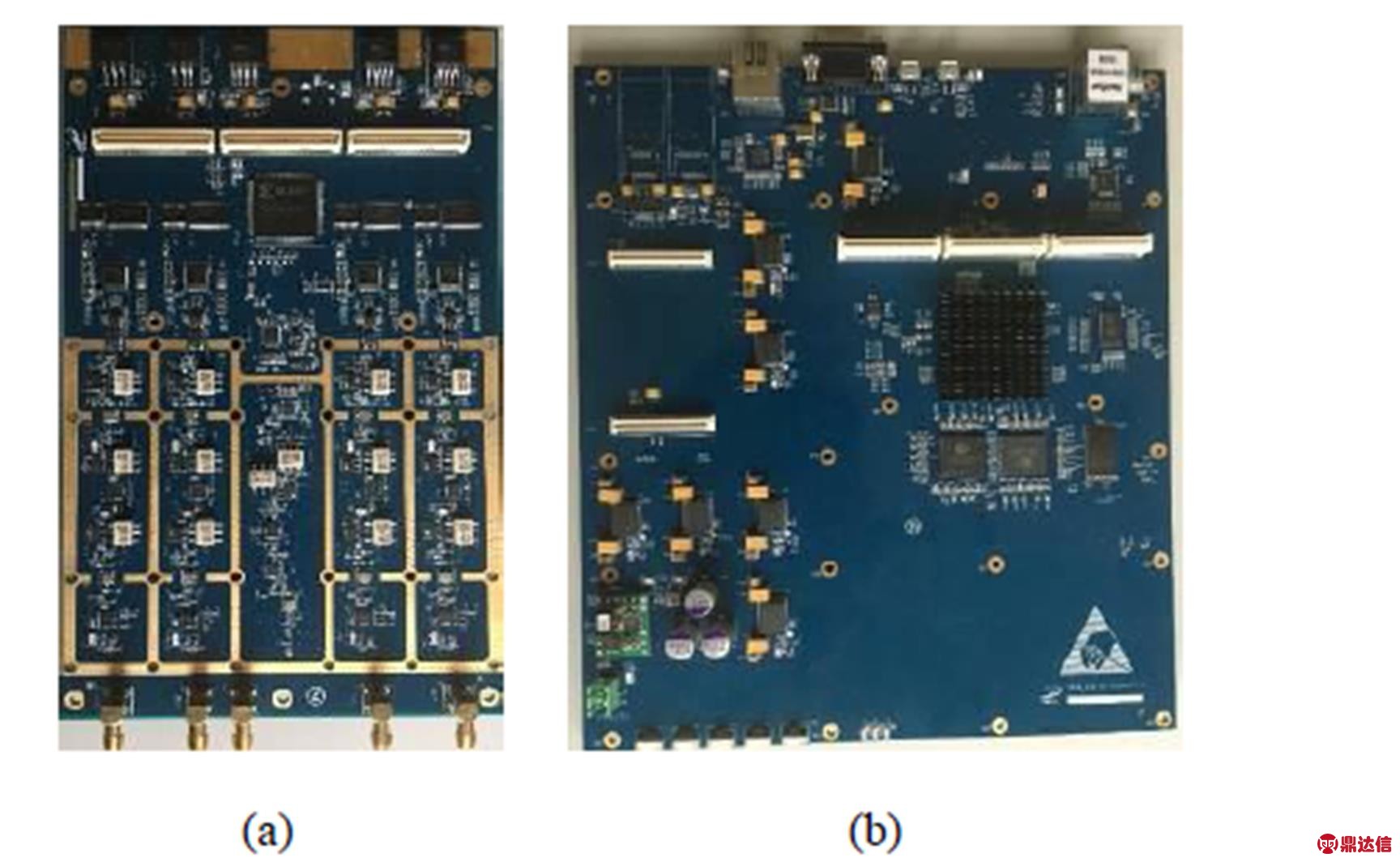

数字母板以FPGA芯片XILINX XC5VSX50T和ARM芯片Freescale iMX6q为核心,功能结构如图7所示。可分为以下三部分:数字板与射频子板接口,包括ADC输出数字信号、时钟信号、CPLD通信的SPI总线等;数字板与ARM子板接口,包括串口数据线、网口数据线、与FPGA通信的PCIE总线等;母板上还有外触发输入、配置PROM芯片、数据存储芯片DDR2 RAM、时钟、电源等外围设备。模拟子板与数字母板的实物照片如图8所示。

图7 数字母板功能结构

Fig.7 Digital board function diagram

图8 模拟子板(a)与数字母板(b)硬件板

Fig.8 Photos of RF board (a) and digital board (b)

12.2 Firmware开发

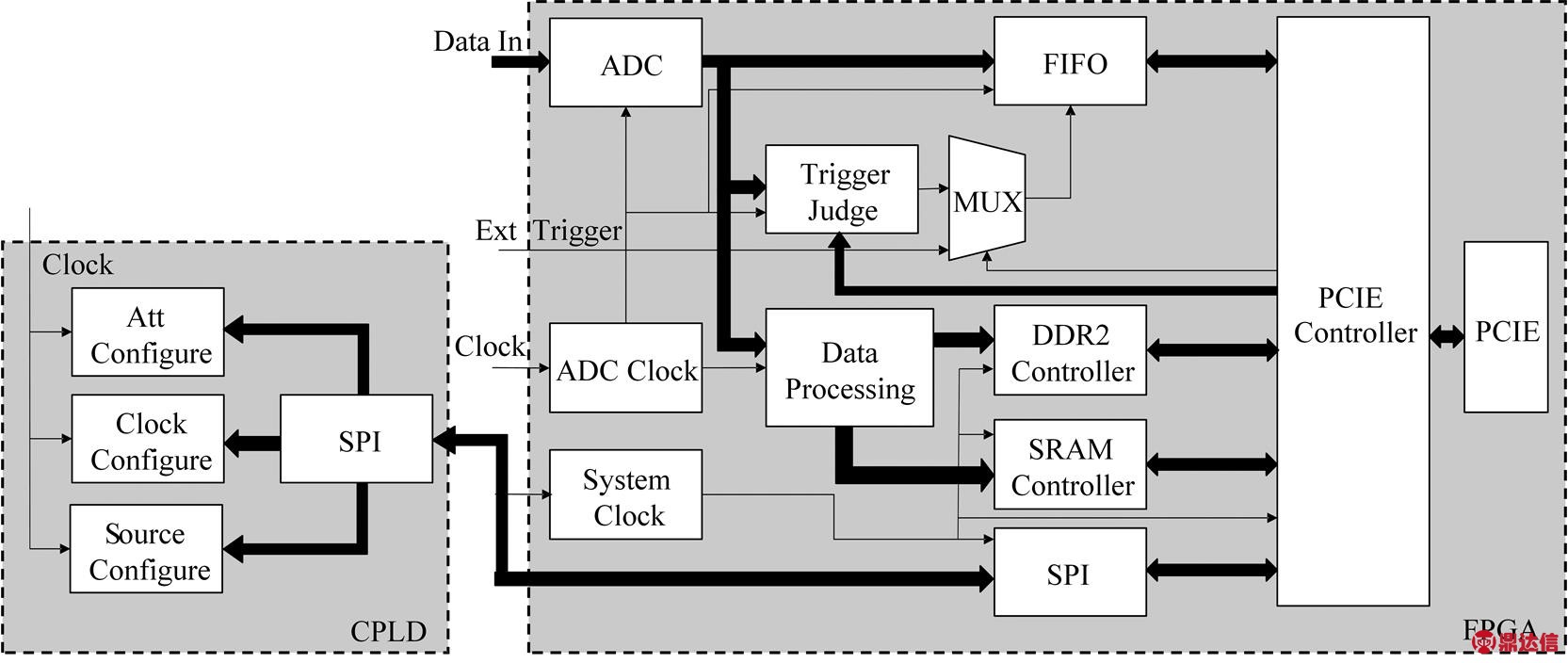

Firmware开发包括两部分,数字板的FPGA与模拟板上的CPLD,具体逻辑设计如图9所示。FPGA是整个处理器的核心控制器件,负责设备接口、系统控制、数据处理器等。主要可分为以下两部分功能:第一部分为对外接口逻辑,包括DDR2存储器、SRAM存储器、FPGA与ARM通信的PCIE总线、FPGA与CPLD通信的SPI总线、ADC数据、时钟、触发;第二部分包括判断束流到达时间并产生触发信号、FIFO (First Input First Output)缓存数据、解析ARM发送命令并进行系统配置(对采样时钟源、触发源、射频板衰减值、自触发阈值进行设置)、数据处理。

CPLD主要实现SPI接口,解析FPGA发送的配置命令对模拟子板进行配置,包括可调衰减、时钟、信号源等。其中,FEL束流为单次通过,为了捕捉到束流通过时BPM信号,需要提供束流到达时间的触发信号。同步系统一般会给DBPM提供外触发信号,但需要准确设置与BPM之间的延时,调试过程比较费时,也增加了系统的不稳定因素。为此在FPGA内开发了自触发模块,该模块实时检测束流信号情况,根据设置的阈值判断是否有束流到达并提供触发信号,FPGA内部的缓存FIFO根据触发锁存束流数据。自触发功能极大地方便了束流调试和系统的鲁棒性。

图9 Firmware逻辑开发

Fig.9 Flowchart of firmware development

12.3 软件开发

采用ARM-Linux操作系统,集成EPICS控制软件,并开发了DBPM的IOC。由于束流最高重复频率只有50Hz,因此将BPM的位置信号处理在EPICS IOC层实现,如果将来提高束流重复频率,需要在FPGA内实现数据处理。

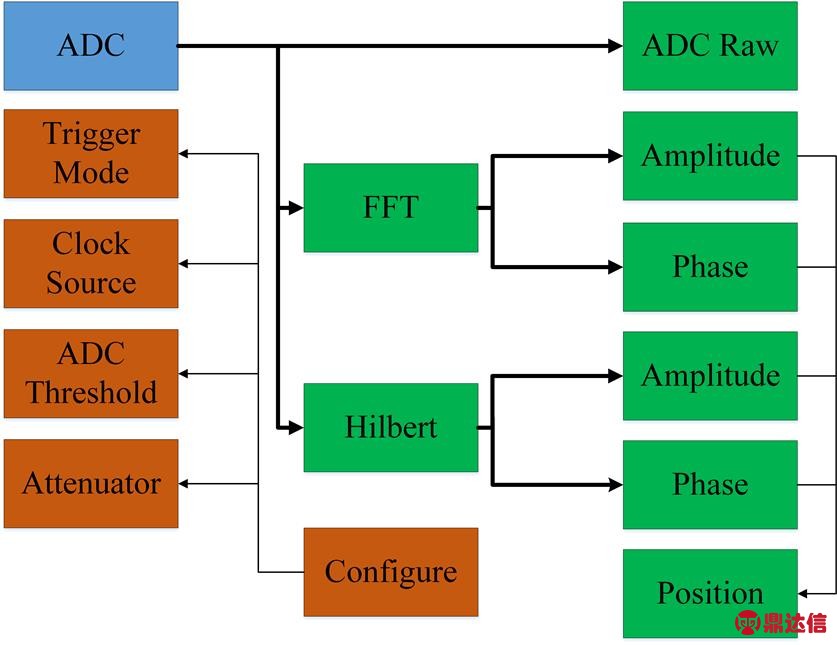

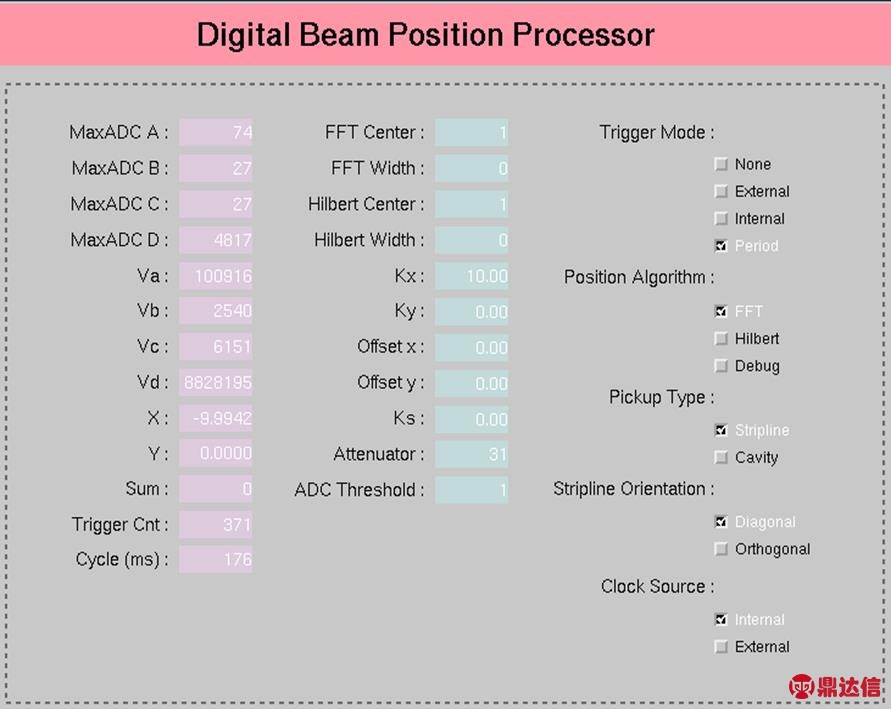

IOC实现的功能模块见图10。DBPM IOC实现了以下功能:系统配置如触发、时钟、自触发ADC数据阈值、衰减; FFT (Fast Fourier Transformation)或Hilbert两种幅度和相位计算算法;SBPM或CBPM的位置计算算法。EDM控制面板如图11所示,除了工作模式配置,还可进行k值和offset 设置。

图10 软件实现功能结构

Fig.10 Software structure of functionalities

图11 EDM控制面板

Fig.11 EDM control panel

3 实验室测试

在实验室对DBPM的噪声水平、通道串扰、线性度、信噪比进行了评估测试。

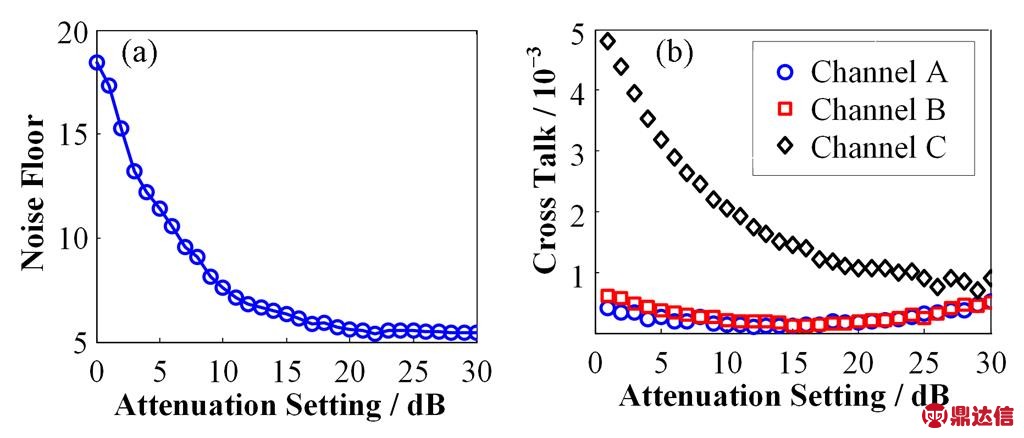

在不输入信号的情况下,测试不同衰减时的噪声水平,测试结果如图12(a)所示,在衰减大于16dB时,ADC噪声约为6。

为了测量通道间的串扰,D通道输入−20dBm的500MHz的正弦信号,其他三个通道接50W匹配负载,设置不同衰减并测量另外三个通道的信号强度与D通道信号强度的比值。测试结果如图12(b)所示,相邻的C通道串扰比其他两个通道大,在衰减大于16dB时串扰小于千分之一,其他两个通道串扰一直小于千分之一,达到−60dB。

处理器衰减为31dB时,最大输入信号功率为10dBm,即输入信号的峰值电压要小于1V。

图12 实验室测试结果

Fig.12 Lab test results

4 现场测试及应用

DCLS已于2016年9月份完成安装,在9月24日首次出光。一共在线安装了8套SBPM、10套CBPM。SBPM处理器工作在内部时钟117.28MHz,CBPM处理器工作在外部时钟119MHz。由于采用自触发工作模式,所有BPM电子学在第一时间检测到了束流通过信号。图13为DCLS现场CBPM电子学机柜。

图13 CBPM电子学设备机柜

Fig.13 Photo of CBPM electronics cabinet

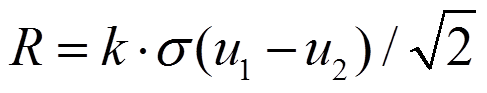

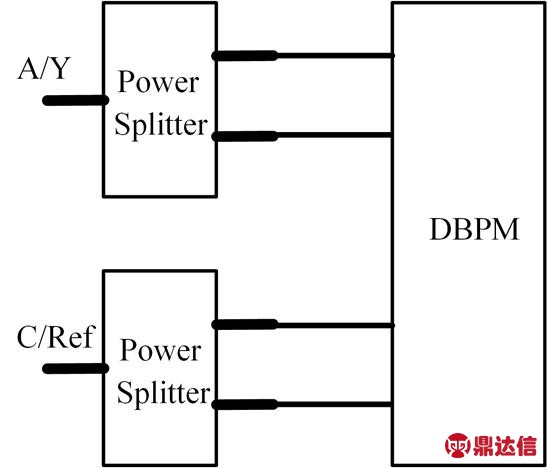

为了评估电子学性能,在大连DCLS上分别对SBPM和Cavity BPM输出信号进行了现场测试。测试方案如图14所示,SBPM的A、C电极或者Cavity BPM的Y电极和参考腔电极的前端输出信号分别经功分器一分二后输入DBPM处理器的4个通道。SBPM采用差比和算法计算束流位置,CBPM采用位置腔与参考腔信号归一化计算束流位置,处理器分辨率R的计算如式(1)所示:

(1)

(1)

式中:u1、u2为两组分别计算的束流位置;σ为对两组位置数据的残差计算方差;k为探头标定因子。

图14 DCLS现场测试连接图

Fig.14 DCLS field test

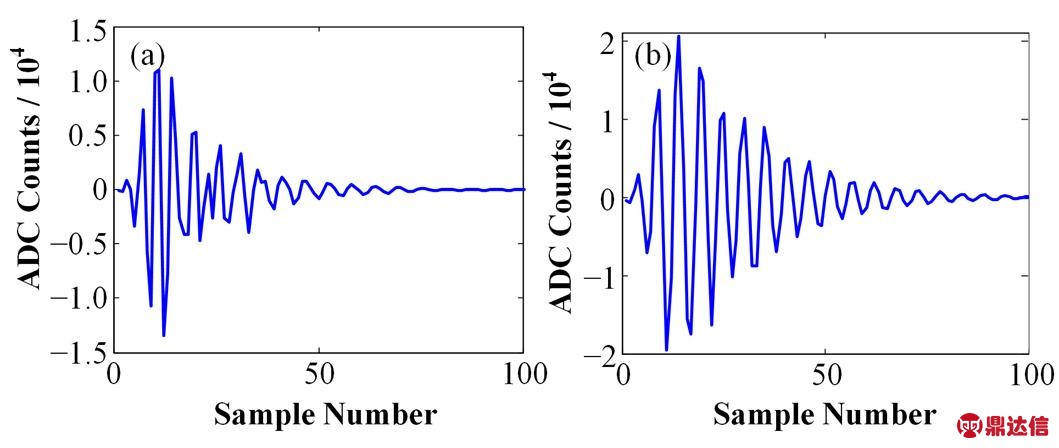

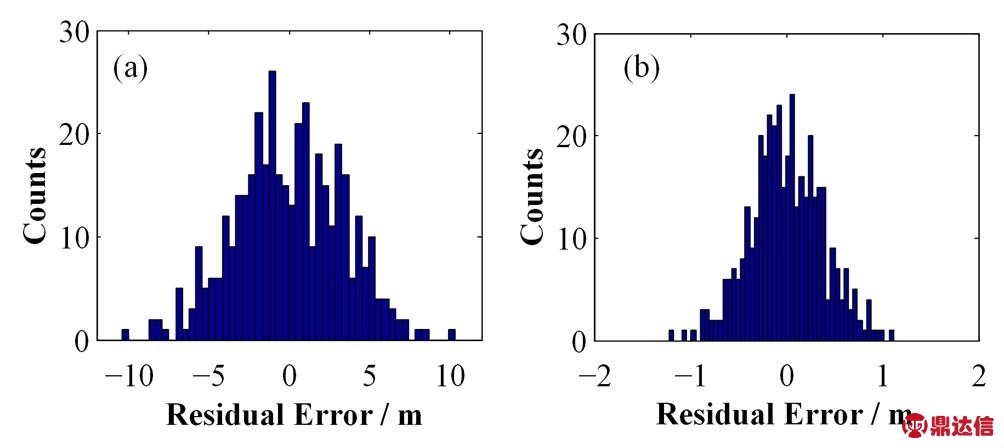

图15为ICT测量电荷量约为500pC、处理器衰减为16dB时的ADC采样原始数据。实验结果表明:不考虑标定因子k时,处理器相对分辨率达到千分之一。DCLS的SBPM的k为7.59mm,CBPM的k值为300μm,乘上k值后计算出SBPM和CBPM的分辨率分别为4μm和0.4μm,测试结果如图16所示,达到设计要求。

图15 处理器ADC采样SBPM (a)和CBPM参考腔(b)数据

Fig.15 ADC sampled one SBPM pickup (a) and CBPM reference cavity (b) signal

图16 SBPM (a)和CBPM (b)处理器现场分辨率测试结果

Fig.16 On-site testing results of SBPM (a) and CBPM (b)

5 结语

本工作成功研制了用于SBPM和CBPM信号处理的一体化DBPM处理器,SBPM和CBPM系统的测试分辨率分别达到4μm和0.4μm,达到设计要求,可在DCLS与SXFEL上实现批量工程应用。