摘要:为满足绝对式光栅尺接口通讯高速、大数据量、高稳定性等的要求,完成了BiSS协议光栅尺接口模块的设计与实现。该接口基于FPGA设计,利用FPGA模块化设计的优势,建立数据读取模块对BiSS协议的数据格式进行时序上的解码,得到传递的数据信息。另外加入延时补偿、CRC校验等模块,前者对数据传递进行时间补偿,可保证高速长距离传输,后者保证了数据的稳定准确传输。仿真与测试表明,该接口模块具有高速传输、数据量大等特点,适合绝对式光栅尺的数据传输。

关键词:绝对式;光栅尺;FPGA;通讯协议

0 引言

绝对式光栅尺通过读取位置编码获取绝对位置信息[1-2]。具有开机直接获得位置信息的特点,无需“归零”操作就能立即获取当前机床各轴的绝对位置信息,因而可以立即进入加工状态或继续上次操作,提高了机床的加工效率[3-5]。位置信息的传输速度和传输稳定性很大程度上影响着这个数控系统的性能。常用的通讯协议有BiSS协议、EnDat协议、SSI协议和Hiperface协议等[6-8]。其中BiSS协议(bidirectional synchronous serial,由德国IC-Haus公司提出的一种新型的可自由使用的同步串行通信协议)在传输速度、协议长度灵活性方面都具有较大优势[9]。另外,有报警位、可调整协议时间长度、可进行延时补偿,在工业应用上较好,且无协议产权问题。使用BiSS协议作为通信协议是非常合适的。

目前最常用的BiSS协议解码是通过IC-Haus公司官方芯片BiSS Mater进行。但此方法所应用的芯片成本较高、数据处理灵活性不足,不利于进行光栅尺接口模块的相关功能扩展。在此,本文基于FPGA设计BiSS协议解码系统,并加入延时补偿、CRC校验等模块进行接口功能的加强,以达到快速准确解码与校验的目标,实现绝对式光栅尺接口通讯。

1 通讯协议整体结构设计

1.1 设计原理

BiSS协议包括了传感器模式(senor mode)和寄存器模式(register mode)。传感器模式使接口快速地读取相应编码器的位置值等信息[9]。寄存器可以让接口与编码器进行双向读写操作,得到接口需要的信息。控制采用哪个模式,主要是依据MA线在该通信周期内的第一个低电平的时间长度,时间大于timeoutSENS表示接下来会进行寄存器模式的通信,时间小于timeoutSENS表示接下来会进行传感器模式的通信。

传感器模式的连接可以分为单一传感器连接和多传感器串行连接,此处着重介绍单一传感器连接方式的传感器模式。由于本设计的数据传输只用到了BiSS协议的传感器模式,因而着重介绍传感器模式。

接口在MA线上发出一个低电平作为本个周期的启动信号,此低电平的时长会短于timeaotSENS。当第一个MA上升沿到来时,传感器开始测量所需数据。当第二个MA上升沿到来时,已准备好数据输出,便拉低SL,表示准备就绪。SL线在传输周期的最后会出现一段时长为timeaotSENS的低电平,表示本次通信结束[9],如图1中的S1。当MA的第二个上升沿到来与SL第一个下降沿到来存在着时间差,说明传输存在着延时,如图1的S2。数据接口需要自动补偿延时,因此理论上可以高速传输数据。当传感器需要处理其他任务,处于busy状态,则start位会推迟到来,如图1的S3,因此通信周期可以灵活调整时间长度。

图1 BiSS协议时序图

1.2 通讯协议整体结构

BiSS协议接口的整体结构示意图如图2所示,此处数据传输采用传感器模式进行通信。绝对式光栅尺读数头的信号采用常用的差分信号发送方式,其内部集成了差分驱动及反差分功能,结合差分接收电路可以使得信息传送更加稳定。SL和MA差分信号通过差分电路处理,可以得到最终待处理的SL和MA信号。FPGA的内部控制模块通过使能信号控制着FPGA接口模块是否开始工作,当FPGA接口工作,可将位置信息进行读取,并送到后续所需模块。

图2 接口整体示意图

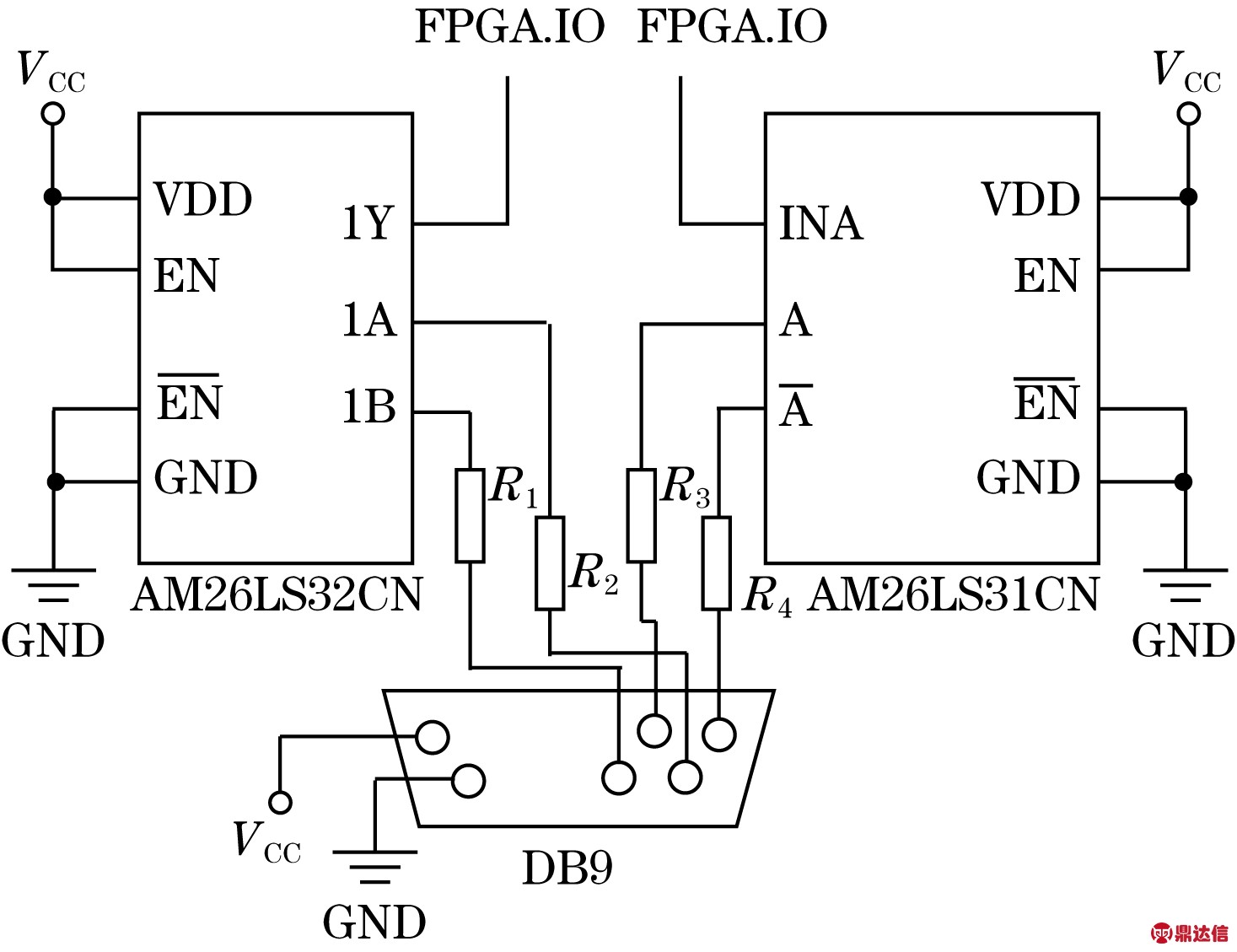

1.3 硬件电路设计

BiSS协议接口功能模块的差分电路及接口具体电路设计图如图3所示。绝对式光栅尺读数头与电路之间的物理转接口采用DB9接口,此接口主要包含MA、SL差分信号线。SL信号经差分处理之后从绝对式光栅尺读数头发出,以AM26LS32CN芯片为核心的反差分电路将信号接收并还原出FPGA所需的SL信号。同样地,MA信号从FPGA引脚发出,通过以AM26LS31CN芯片为核心的差分电路处理后发送给光栅尺读数头。经此处理之后,得到适合FPGA处理的2个信号。

图3 BiSS接口硬件电路图

1.4 软件模块设计

FPGA引脚连接MA及SL信号,需要在每个使能信号en到来之后得出光栅尺读数头所发送的位置值,并校验发送过程是否有误。接收位置值及校验完毕并通过,可得到一个当前的位置信息。根据FPGA的自上而下的模块设计思想及对系统功能的分析,可把本部分软件设计成MA驱动模块、SL接收模块、CRC校验模块,如图4所示。BiSS协议采用传感器模式进行数据传输,采用FPGA电路所产生的MA信号作为系统的传输时钟。BiSS协议可以根据实际需要,对一个数据传输周期的时间总长进行灵活的调整,每个数据传输的总时间是可能不相同的。具体需要的时间由绝对式光栅尺读数头来决定,而SL接收模块可以得出所需的时间,通过2个verilog模块的相互配合,可以对周期通信时间进行匹配。

图4 模块设计示意图

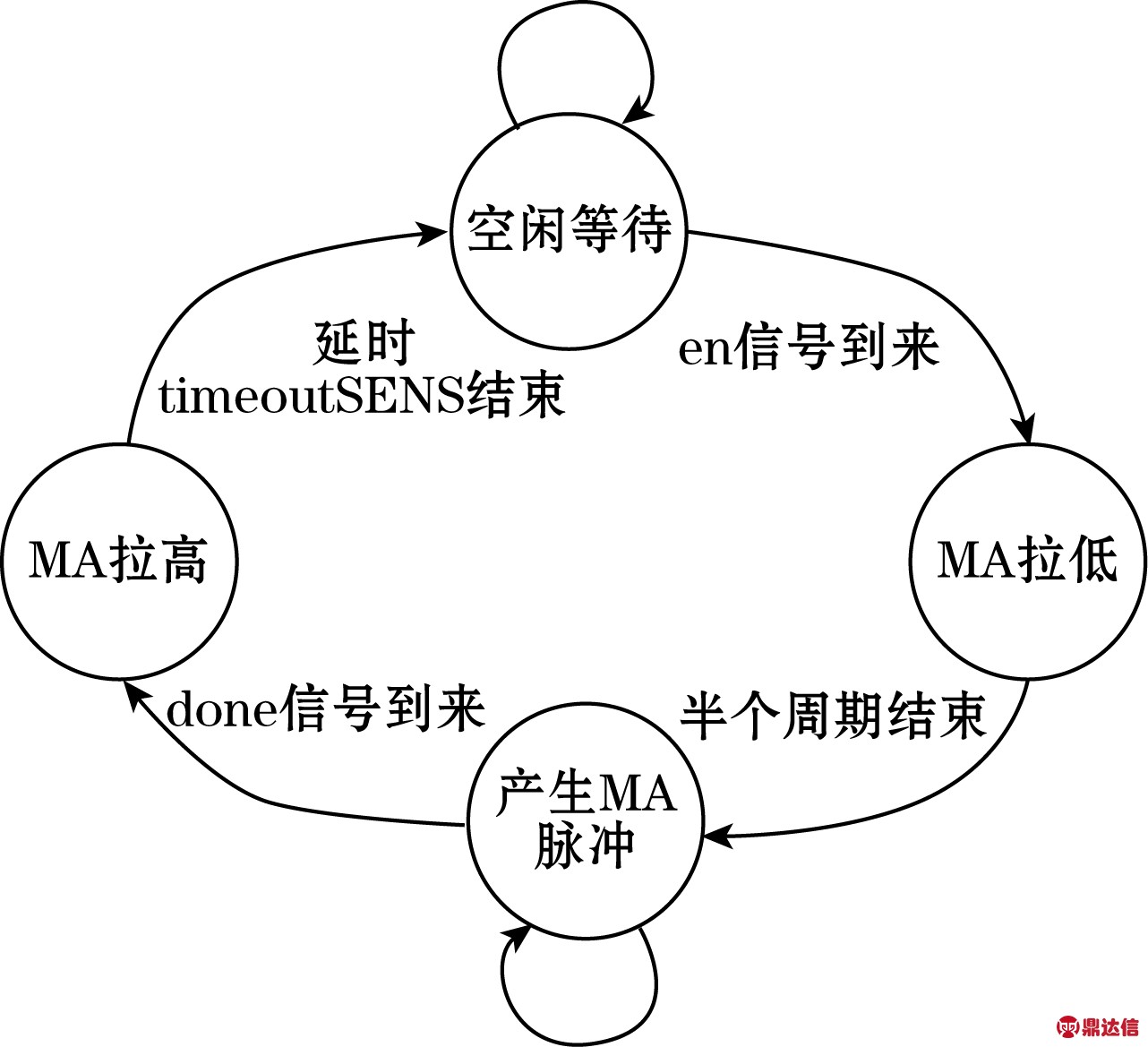

在空闲等待状态,MA信号保持高电平,done信号保持低电平。当MA驱动模块接收到来自接口控制模块的en使能信号时开始工作,进入下一个状态。此状态只需把MA信号拉低,并保持半个MA时钟周期,即进入下一状态。在该状态,不断产生MA脉冲信号。若done线出现一个高电平,即进入下一状态。此状态需保持一个timeoutSENS时间长度的高电平,结束后即重新进入空闲等待状态。图5为MA发生器的状态跃迁图。

图5 MA发生器状态跃迁图

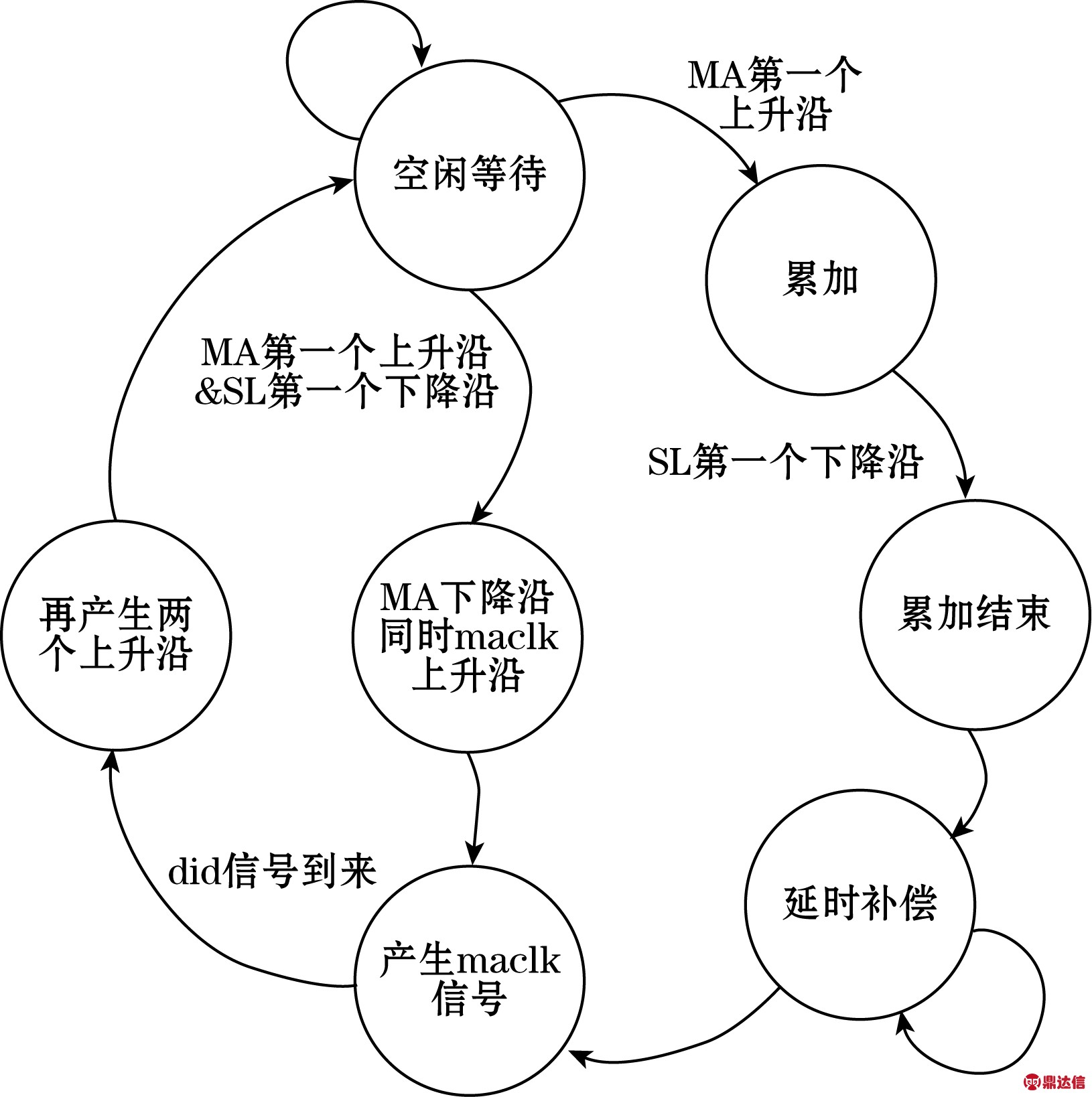

SL接收模块通过done信号线控制着MA时钟的总长度,通过所得到的位置值和did信号线控制着后续CRC校验模块。在数据传送的时候,有可能发生信号的延时,SL数据的改变相对于MA时钟的上升沿出现滞后。BiSS接口需要对此延时进行补偿,以适应高速长距离传输。因此在接口读取SL信号的时候,不能直接用MA驱动模块的MA信号作为同步接收时钟,需要先制作出经过延时补偿的并按数据接收周期产生的接收时钟信号maclk,利用其上升沿检测SL读数触发。通过FPGA逻辑检测到MA信号第二个上升沿与SL信号的第一个下降沿的延时时间,得到相对MA信号延时若干时钟的maclk信号,其状态跃迁如图6所示。

图6 延时补偿

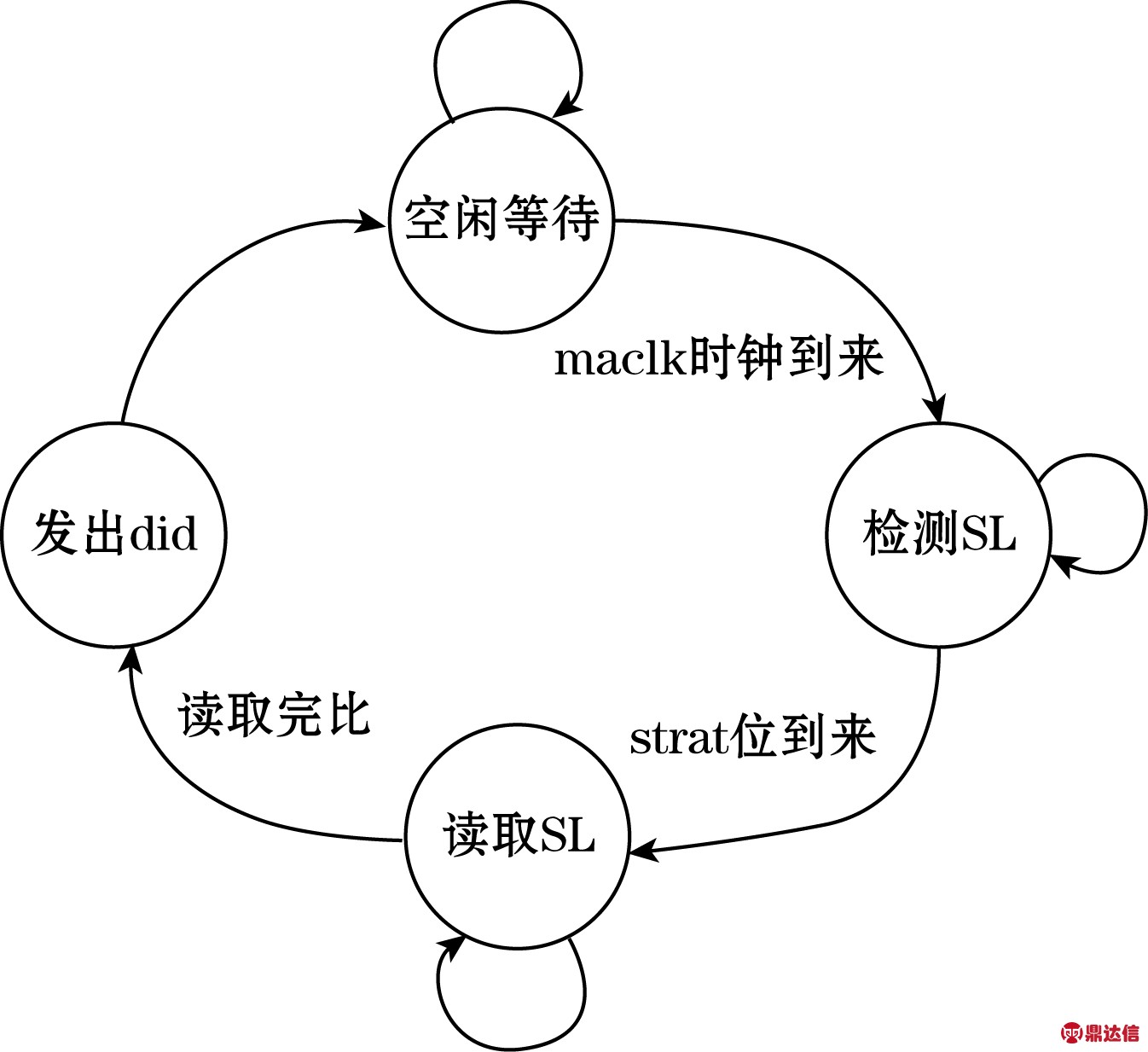

在FPGA芯片内部定义一个包括位置值、错误位和校验位等数据的寄存器data。maclk的上升沿为读取SL的触发信号,maclk上升沿没到来时不进行检测,处于空闲等待状态。当检测到SL的start位(即SL线上的第一个为1的信号)到来时在kaishi信号线产生一个时钟的高电平,并进入读数模式,在上升沿时读入SL的电平值。同时需要进行计数,当读完所有位数,即完成读数,并向CRC校验模块发出一个did信号。如图7为其状态跃迁图。为了提高数据传送时的稳定性,BiSS协议在数据位的后面加入了循环冗余校验。循环冗余校验(CRC)是一类重要的线性分组码,编码及解码方法简单,检错能力强,在通信及测控等领域都等到了广泛的应用[10-12]。

图7 数据读取

光栅尺读数头端发送的数据已经包含了CRC校验码,接口建立CRC校验模块,对其进行verilog设计,以下是以二进制序列G=1000011为例的数据校验主要程序:

always@(posedge clk)

begin

if(data[35])data[35∶29]<= data[35∶29]^7'b10000111;

else if(data[34])data[34∶28]<= data[34∶28]^ 7'b 10000111;………

else if(data[6∶0]==crc)begin error<=1'b0;end

else begin error<=1'b1;end

end

如verilog主代码所示,先通过模二除法求出数据序列D的新校验码,使之与接收到的CRC校验码进行对比,若一致则正确,输出接收的数据值;否则不正确,发出error信号,输出上一个读数周期的数据值。另外,在校验完毕的时候,需要发出一个en_sig的信号,表示已经处理完成。

1.5 软件整合

通过以上模块的理论分析以及预设功能所需的输入输出引脚,对上述3个功能模块进行例化。SL接收模块为整个BiSS接口的主要控制模块,MA驱动模块接收来自外部的启动信号并首先开始工作,CRC校验模块对接收的数据进行校验并输出正确的位置值。图8为可以通过编译的例化代码所对应的RTL图,与上述接口整体设计示意图基本一致。

图8 BiSS接口verilog模块的RTL

2 系统仿真与测试

通过ModelSim软件进行功能仿真,向BiSS协议接口模块进行数据传送,设定第一个周期开始发送的数据是3,第二个周期数据是4,并以此类推,另外设置一定的传输延时。在ModelSim软件设置位置值输出使能en_sig、错误信号error、总数据寄存器dataall、MA信号ma、SL信号sl和位置值jduiwei,为6个观测对象。图9为ModelSim仿真波形图及其波形局部放大图,信号波形符合理论形状,解码结果(位置值)与预先设定的数据值一致。通过波形图可分析得到发送一个数据所用的时间约为22.5 μs(取决于数据长度,并可通过改变波特率与数据长度改变传输时间),可适应大数据量传输。由于设定了传输延时,SL值的改变滞后于MA上升沿,而data的更新也并不与MA下降沿同步,而是同步于一个SL数据的中点。可见延时补偿功能发挥效用,使SL信号的读取做出同样时间的滞后,以补偿传输延时,增强接口在高速传输时的适应性。另外,可观察到位置值的更新与数据接收完毕存在一段时间,此段为CRC校验时间。校验完毕error信号不发出错误使能信号,即更新位置及发出使能信号en_sig。

图9 ModelSim仿真波形图

3 实验测试与分析

3.1 系统实验测试

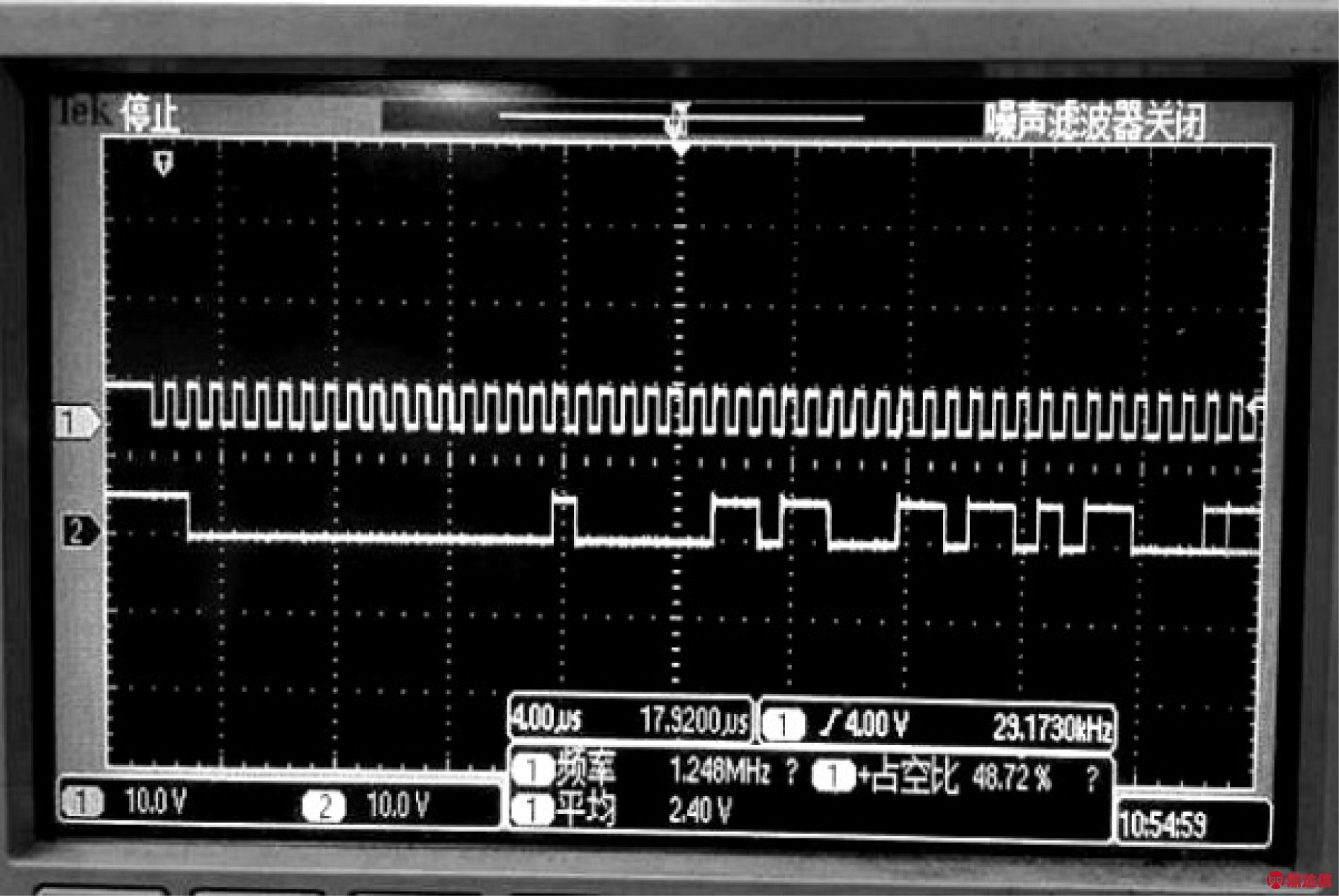

将软件模块固化到FPGA嵌入式电路中,连接数据长度更长的绝对式光栅尺。移动光栅尺,使得光栅尺发出不同的位置信息,通过FPGA接口进行位置值的读取。通过示波器检测和显示相应的信号,并对比实验波形与协议理论波形。波形如图10所示,可以观察到SL和MA信号符合协议理论波形,BiSS协议接口模块可正常驱动光栅尺编码器,令绝对式光栅尺位置值正常传输。

3.2 分析结果

由仿真结果和测试结果可知,此接口模块可正常实现接收数据,并且带有延时补偿、CRC校验、数据长度可变等的功能。此接口及其功能对光栅尺数据的传输有着良好的适应性。

图10 系统检测波形图

4 结束语

本文研究了BiSS协议的接口构建。针对绝对式光栅尺信号传输所需的高速、高精度和稳定性的要求,提出了FPGA实现BiSS接口构建的方案,建立以FPGA为核心的嵌入式系统。系统仿真分析与实验测试表明,此方案可准确对BiSS协议进行解码实现位置信息传输,并且具有延时补偿、CRC校验等的功能。且FPGA设计可取代大量的电路系统,节约了空间和成本。可满足绝对式光栅尺信号传输的需求。