摘 要:针对现有编码系统处理视频格式单一的问题,提出多接口视频编码方案,采用TI DSP(TMS320DM8168)+FPGA构架,将多种常见的视频接口设计在同一系统中,应用FPGA采集视频数据后传送给DM8168,通过软件控制送至各子模块,进行编码。经长期测试结果表明,该系统编码性良好,视频显示无误码,适用性和通用性更强。

关键词:TMS320DM8168;多接口;DSP+FPGA;视频编码

随着视频质量的不断提高,而带宽有限,所以视频编码技术得到广泛应用。但是现在主流视频编码技术主要针对某一领域,接口方式单一,很难适应多种应用场景,故提出多接口编码方案,在不改变控制系统的前提下,通过修改控制代码使其能够应用到大部分领域,缩短开发周期、减小成本。

TI的达芬奇系列是专用于多媒体数据压缩芯片,其中TMS320DM8168是一款可编程浮点DSP,内部集成高分辨率视频/成像协处理器,可以实现多路高清、高帧视频的采集、编码、显示和控制,从而可满足用户在高集成度和高清晰度上越来越苛刻的需求。

1 总体方案设计

方案采用DSP+FPGA构架,总体方案设计如图1所示,FPGA主要功能为采集输入的视频信息缓存然后传输给DSP;DSP收到信息后,按照程序将视频编码后输出。其中设计了高清、数字、模拟和Camera link 4种常见的视频接入方式,基本满足现有百分之八十以上的视频输入接口,输出设计了高清输出、USB接口和千兆网口,可以更好、更快的与上位机通信。

图1 系统总体设计框图

2 多接口设计

2.1 数字视频接口与模拟视频接口的设计

常见的数字摄像头支持DVP和MIPI两种数据接口,本系统采用了DVP接口,即8 bit并行数据接口。通过I2C总线配置摄像头的采样频率和分辨率。一般摄像头的驱动电源为3.3 V,部分为1.8 V或2.5 V,故预留3种电源接口,以满足更多种类摄像头。调试过程中发现,I2C总线信号SDA、SCL需加上拉4.7 K电阻,上拉电源与摄像头电源相同,根据摄像头选择相应的上拉电源。如图2为DVP接口与电源选择原理图。

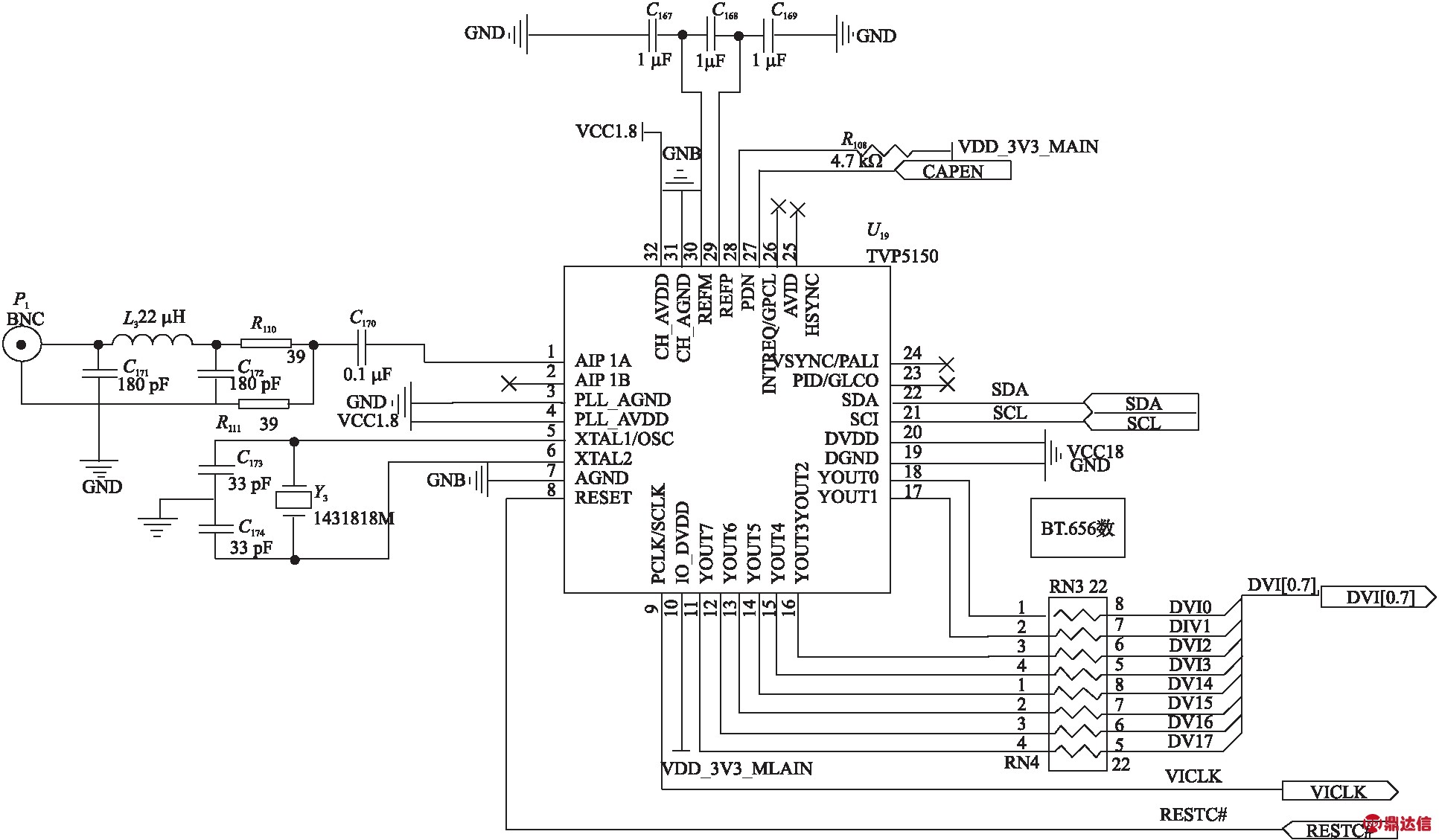

模拟视频接口与数字视频接口类似,只不过采集的为模拟视频信号,方案采用TVP5150为视频解码芯片,将模拟视频信号转化为DVP接口信号,也是通过I2C总线配置摄像头。TVP5150可以将摄像头采集的模拟视频数据解码为YCbCr422类型的数字视频数据,满足ITU-RBT.656协议格式。模拟视频接口设计原理图如图3所示。

图2 DVP接口与电源选择原理图

图3 模拟视频接口设计原理图

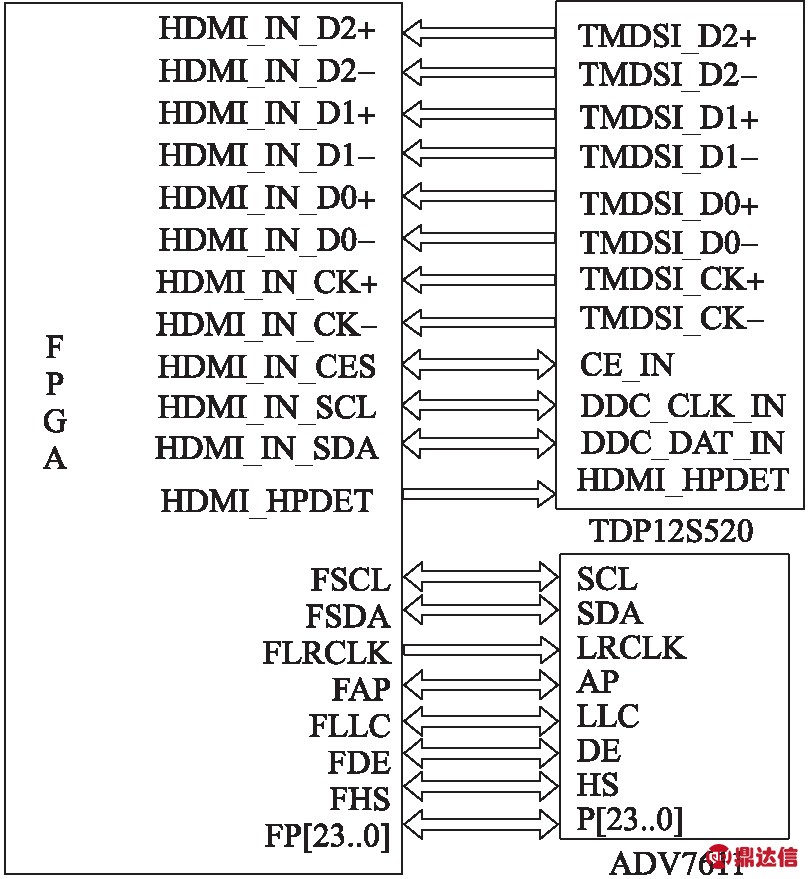

2.2 高清接口设计

系统选用ADV7611和TDP12S520作为视频译码和接收芯片。其中ADV7611为低功耗HDMI接收器,TMDS时钟频率最大可达165 MHz,支持高清多媒体接口(HDMI®)1.4a功能,支持所有强制性和附加3D视频格式扩展的色度,包括sYCC601、Adobe RGB、Adobe YCC 601、xvYCC扩展颜色范围并且兼容CEC 1.4。TDP12S520主要是起电平转换时的反向驱动保护,防止静电过大而引起的系统崩溃或者传输出现误码,为高速差分信号传输提供静电放电保护(ESD)。如图4为高清接口示意图。

图4 高清接口示意图

2.3 Camera link接口设计

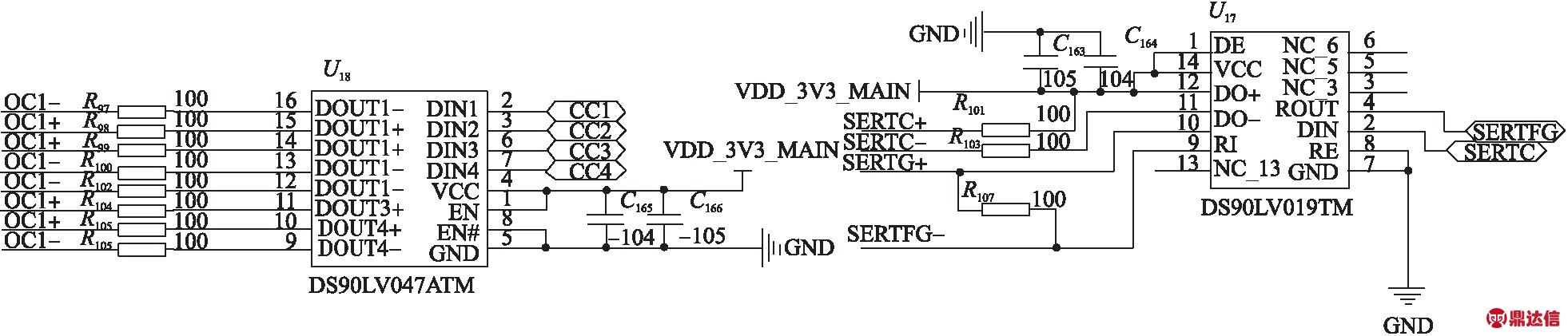

工业高帧相机的接口一般为Camera link接口,输出LVDS信号,而FPGA的I/O接口标准为LVCMOS/LVTTL,故要使用转换芯片,选用DS90CR288A把4对LVDS信号转换成28 bit TTL电平信号,输出给FPGA。根据LVDS 工作原理,需要在其两根传输线之间加上100 Ω的电阻。

Camera link接口有3种传输方式:低速、中速、高速,对应的配置方式为:base、medium、full。base模式包含一块Channel link芯片(选用DS90CR288A)和一个CameraLlink机械接口;Medium模式包含两块Channel link芯片和两个Camera link机械接口;Full模式包含3块Channel link芯片和两个Camera link机械接口;本设计选用Full模式,可根据视频接入方式在base、Medium、Full 3种模式之间切换,选用DS90LV047和DS90LVO48芯片为控制和配置工业相机。图5为其硬件原理图。CC1为外部同步信号(EXSYNC)下降沿出发读取数据,CC2为像素重置(PRIN)低电平有效,CC3高电平有效,低电平翻转,CC4保留信号(未定义)。

图5 Camera link硬件原理图

3 FPGA+DSP结构设计

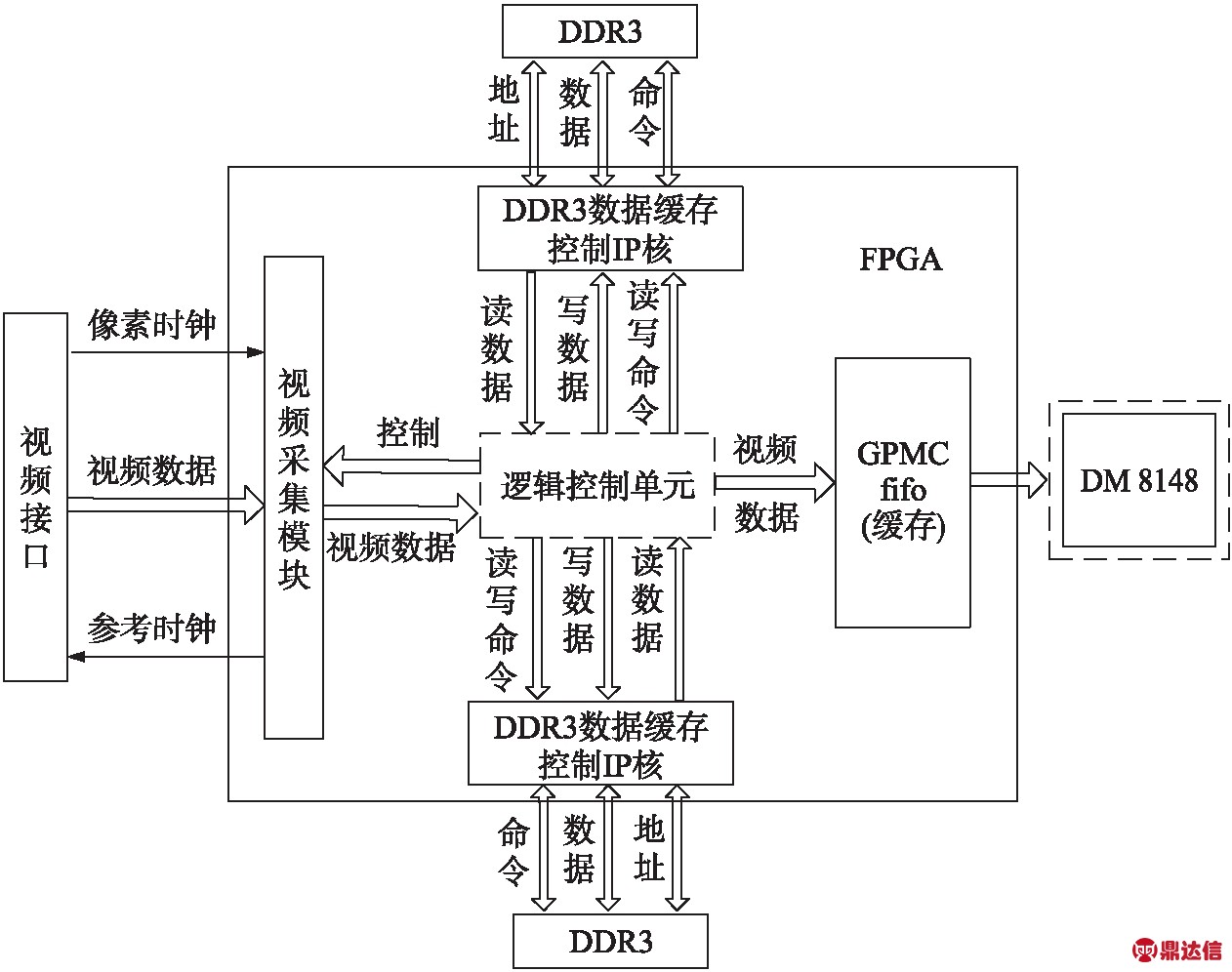

3.1 FPGA逻辑设计

FPGA主要功能为采集视频信息,缓存传输给DSP。当视频像素达到1080p及以上时,DDR2就不能满足设计需要,所以设计两片DDR3进行乒乓操作缓存。DDR3采用数据宽度为16 bit的MT41J64M16芯片,FPGA逻辑设计如图6所示。其中DDR3与FPGA连接,包含了16 bit数据总线,15 bit地址总线,Bank地址包括了BA2~BA0,还有一对差分输入时钟,频率设置为200 MHz;FPGA对DDR3的控制主要通过列地址选择信号(CASA)、行地址选择信号(RAS)、写使能信号(WE)实现。此外为了防止数据线终端反射,通过FPGA控制ODT使能片内电阻优化性能。

3.2 DSP选取

DSP选用TI达芬奇系TMS320DM8168,浮点DSP C674x+ARM Cortex-A8高性能视频处理器;拥有2个独立可编程高清视频图像协处理器,支持8路720P30或2路1080P60的视频编解码。GPU:SGX530 3D图形引擎,支持OpenGLES 1.1/2.0、OpenVG 1.0和OpenMax API;支持2个独立视频输入端口:1路16/24bit HD或2路8bit SD输入。

TMS320DM8168包含的2个独立可编程高清视频图像协处理器,即硬件编码模块,每个编码模块的最大处理速度为每秒处理60帧1080P高清视频,即每个编码模块处理带宽约为116 MHz左右。带宽计算公式为:带宽=分辨率·像素·帧率/8/1024/1024/1024=1920·1080·60/1024/1024/1024=0.115 9 Gbyte,整体处理带宽为232 MHz。

图6 FPGA逻辑设计图

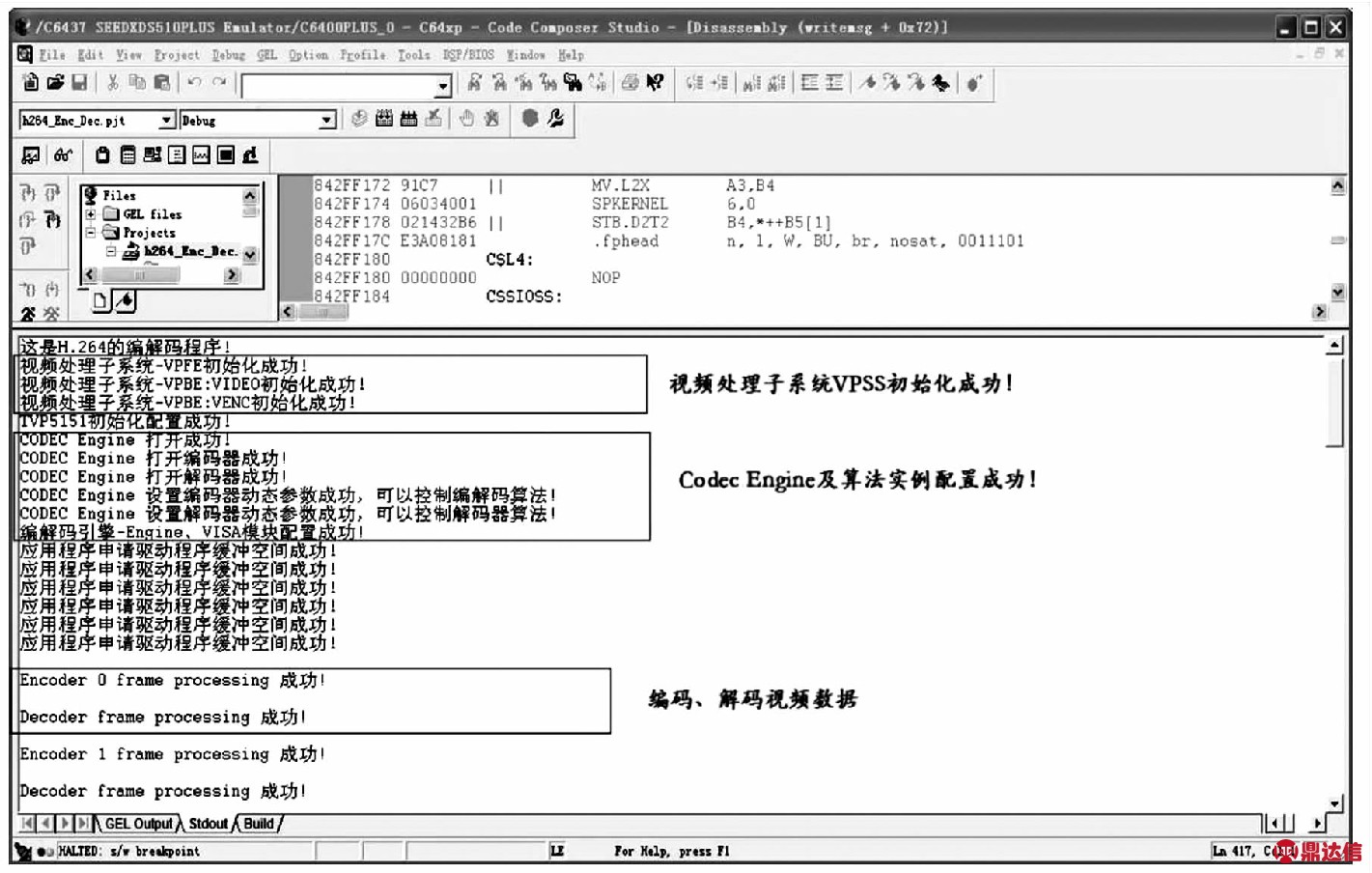

图8 本地回放程序测试

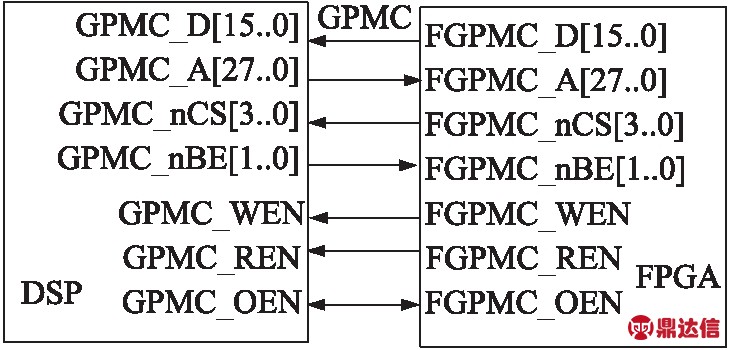

3.3 FPGA与DSP接口设计

DM8168包含了GPMC(General-Purpose Memory Controller)接口,即通用存储控制器,可与外部存储设备如NOR FLASH、NAND FLASH、SRAN等接口通信。可以通过EDMA方式实现DSP与FPGA之间的高速数据交换。如图7为DSP与FPGA的GPMC连接示意图。在DM8168中GPMC接口时钟工作在异步模式,频率125 MHz配置并设置模式,应用到其相关I/O口如下,其中GPMC_D为数据总线,GPMC_A为地址总线,nCS为片选信号,WEN、REN为读、写使能信号,OEN为使能时钟。

图7 GPMC接口连接图

4 验证与分析

处理好的视频信息经千兆网口传输至PC机,自动保存到硬盘上。应用本地回放测试功能,播放存放的视频信息,运行实例如图8所示。

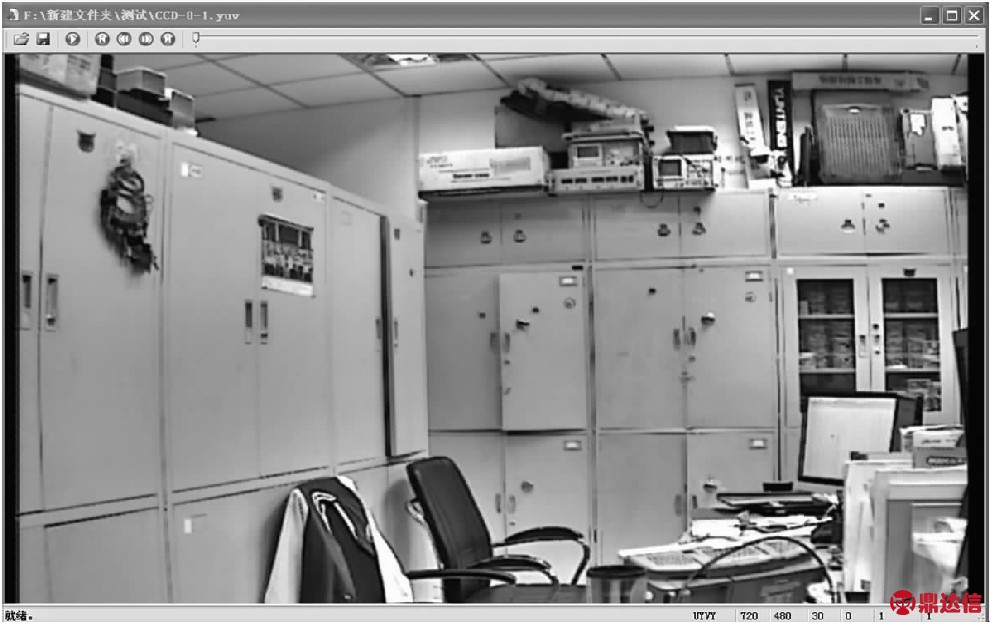

观看测试结果图,如图9所示,频画面清晰、平滑、无丢帧,效果比较好,在满足人眼识别的情况下,整体满足方案预期效果。

图9 测试效果图