摘 要:基于国内0.13 μm E-FLASH 工艺,设计了一种由E-FLASH 控制的锁相环芯片,为芯片提供可配置的频率源,内置LC 压控振荡器、射频分频器、数字分频器、环路滤波器接口和电荷泵,实现了锁相环的全集成。芯片功耗仅为30 mA,面积仅1 mm ×1.5 mm。工艺可集成于E-FLASH 工艺的片上系统,能提供良好的相位噪声和抖动特性,最高输出频率可达2.4 GHz,锁定后10 kHz 频偏的相位噪声优于-116 dBc/Hz。

关键词:锁相环;E-FLASH;相位噪声

0 引 言

随着频率源技术的不断发展,锁相环的应用范围也在逐步扩大。随着整机系统规模的不断扩大,系统设计的复杂度和调试难度也在逐步增大,因此为了减少系统的调试难度,越来越多的项目使用片上全集成锁相环系统对系统提供时钟。在整个T/R 链路中,频率合成器的功耗占比可达50%,因此低功耗锁相环设计成为了整个系统降低功耗的核心指标。

系统设计过程中对功耗提出了严格的要求,为了满足用户对低功耗的进一步要求,需要将现有的分立式频率源芯片化,从而在不影响系统性能的同时,将功耗大幅降低。

随着CMOS 工艺的不断进步,器件在更高截止频率和更低功耗上取得了突出的进步,同时成本大幅下降,E-FLASH是一种非易失性存储器,其结构为浮栅结构,通过隧穿效应进行编程。

通过E-FLASH 存储器对锁相环进行配置,使用方便、调试难度小,后期装机后故障排查效率高。而且本芯片可以与MCU 和FPGA 等工艺进行集成,大幅度减少外围电路器件数量和芯片测试的成本,可以实现单片系统的片内集成频率源,批次一致性好,调试工作量小,易于生产。

通过将分立器件的频率源芯片化,大规模减少了外围电路,仅需少量电阻、电容即可实现高性能低功耗的集成频率源,从而满足了用户对于小型化,低功耗,全集成的要求,大幅降低了整体组件的体积。

1 E-FLASH 工艺

随着集成电路制程和特征尺寸的减小,现阶段的EFLASH 工艺可以在同一晶圆上同时制造电感,电容,MOS器件,变容管和E-FLASH 存储器阵列。从而可以实现射频、模拟与数字电路的单片集成,显著降低成本,提高产品集成度。

本设计所使用的E-FLASH 工艺具有良好的数字性能和优秀的E-FLASH 存储器支持。工艺提供了4 层栅结构用于制造E-FLASH 存储器,提供了浅槽隔离和PN 结隔离来降低衬底之间的耦合。工艺还提供了顶层的超厚金属以实现高Q 值电感等无源器件。芯片面积1 mm×1.5 mm。

2 锁相环原理

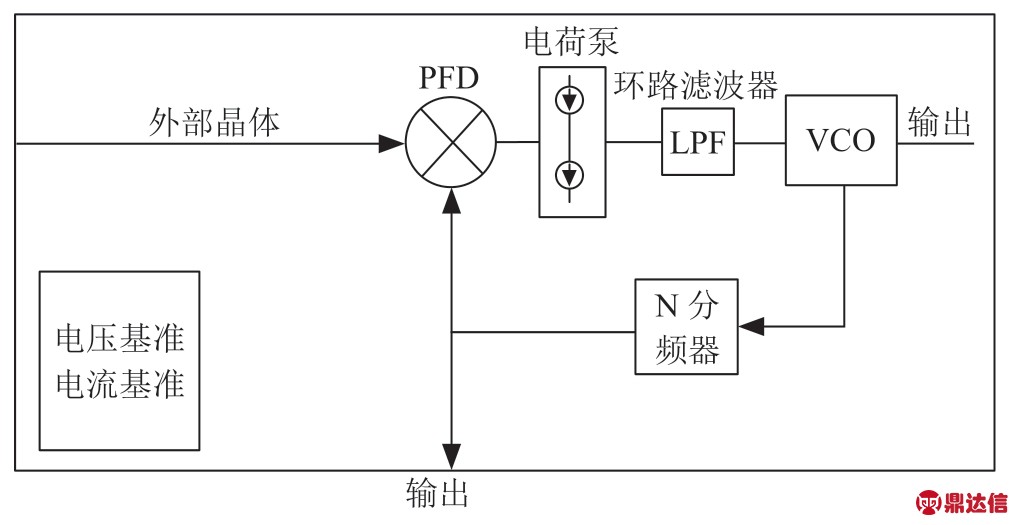

锁相环系统包括:鉴相器(Phase Frequency Detector,PFD),电荷泵,压控振荡器(Voltage Control Oscillator,VCO)和分频器。将VCO 的输出分频后,和参考对比,从而调整VCO 的频率和相位,最终实现稳定的输出频率。系统的原理框图如图1 所示。其中电压基准和电流计准为整个电路提供电压和电流的参考值。

图1 锁相环原理框图

3 射频分频器设计

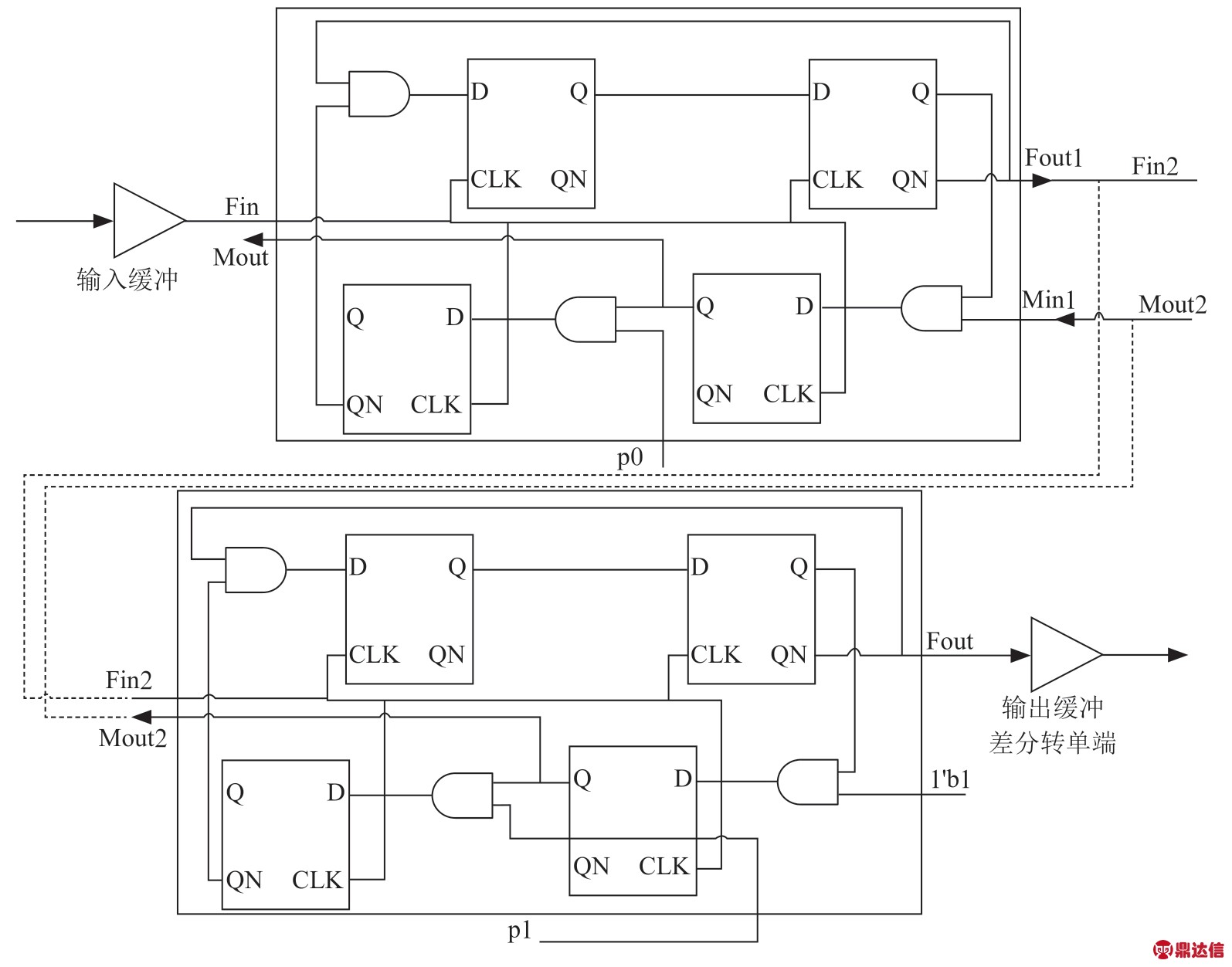

射频分频器的核心结构为2/3 分频器,通过p1、p0 端的不同设置,实现2 分频或3 分频。其工作原理为:在一个分频周期中,最后一位产生的DIV(n-1)信号,依次向前级进行传输,当分频器输入为1 且DIV 有效时,本周期为3分频,同时增加一个输入信号到输出信号的周期上;当分频器输入为0 时,控制部分不对分频信号进行额外控制,此时本单元为2 分频。

射频分频器的结构如图2 所示,电路由输入缓冲级、第一级的2/3 分频器、第二级的2/3 分频器、输出缓冲级、差分转单端电路组成。输入缓冲级接收来自VCO 的差分振荡信号,共模电平通过小电阻直接连至电源,幅度为VDD±0.4 V。图中虚线表示仅列出2 级2/3 分频器,根据分频比需要可以自由设置分频器的级数,从而获得所需的频率分辨率。

图2 射频分频器原理框图

第一级2/3 分频器工作频率比第二级2/3 分频器工作频率高1 倍以上,因此考虑第一级2/3 分频器电路的电流最大,负载电阻为700 Ω,输出摆幅为VDD-0.8 V ~VDD。第二级2/3 分频器电路镜像电流设置为第一级的50%,负载电阻为1 400 Ω,输出摆幅为VDD-0.8 V ~VDD。

根据需要可配置更多的2/3 分频器,用于实现任意整数分频比。本芯片分频器功耗为8 mA。

4 鉴相器电路设计

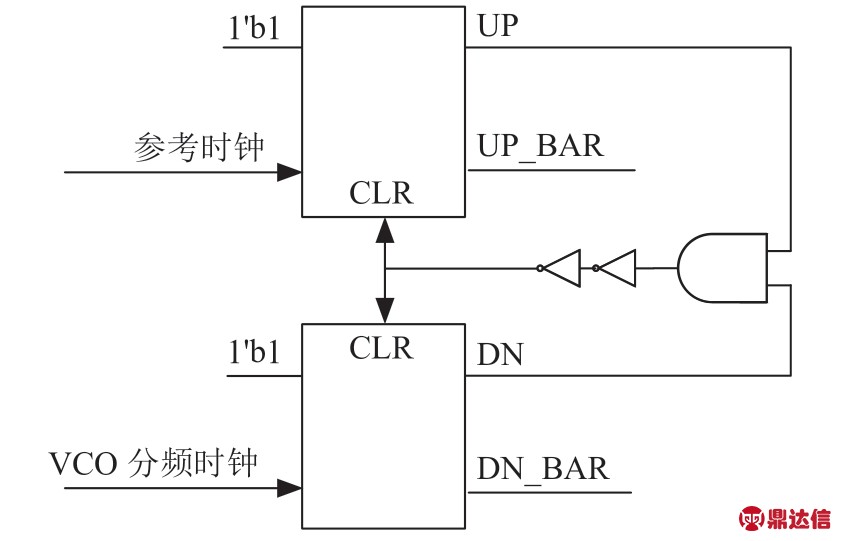

参考时钟和分频器输出时钟同时进入鉴相器,二者的相位差转换为电压信号给电荷泵,电荷泵的作用是将相位差电压信号转换为电流信号给环路滤波器进行充放电。环路滤波器的输出电压输出给VCO,如此可以完成锁相环的一个鉴相周期。最终设计完成的鉴相器结构如图3 所示。

图3 鉴相器原理框图

当VCO 频率高于N 倍的参考频率时,或者相位超前与参考时钟时,鉴相器输出一个更长的DN 信号和一个较短的UP 信号,DN 和UP 信号给到电荷泵可以转换为相应的电流信号。总电流从环路滤波器抽取电流,导致环路滤波器输出电压降低,从而可以降低VCO 的频率。经过多个鉴相周期可以使得参考时钟和VCO分频时钟的频率和相位完全一致。达到锁相的目的。

电荷泵的电流通过时间t 为:

其中,Tin 为参考信号周期。则其电流i 为:

所以鉴相器的增益KPFD 为:

5 电荷泵设计

电荷泵的核心电路为电流源,通过使用多段成比例电流源,可改善电荷泵的噪声特性。同时加入了电流转向运算放大器,可以避免出现电荷分享,降低噪声,最终设计完成的电路结构如图4 所示。

图4 电荷泵原理框图

其中本芯片的电荷泵总电流为6 mA,电流的大小直接决定锁定时间,本芯片设计了可配置的单独的低功耗的模式,可以减小电荷泵的功耗。

6 压控振荡器设计

VCO 的设计中,主要考虑了以下指标:

(1)VCO 的调谐灵敏度:即压控振荡器的增益KVCO,一般设置为50 MHz/V。

(2)频率调谐范围:最大输出频率与最小输出频率的差,一般设置为100 MHz ~150 MHz。

(3)线性度:理想的VCO 要求在整个调谐范围内KVCO都为常数,出于稳定性和实际制造工艺,一般要求在整个调谐范围内KVCOmax/KVCOmin ≤2。

(4)相位噪声:VCO 最重要的设计指标,即指在载波频率ωc 频偏Δω 处,单位带宽内单边带噪声谱密度与载波功率比值的分贝形式,单位为dBc/Hz。

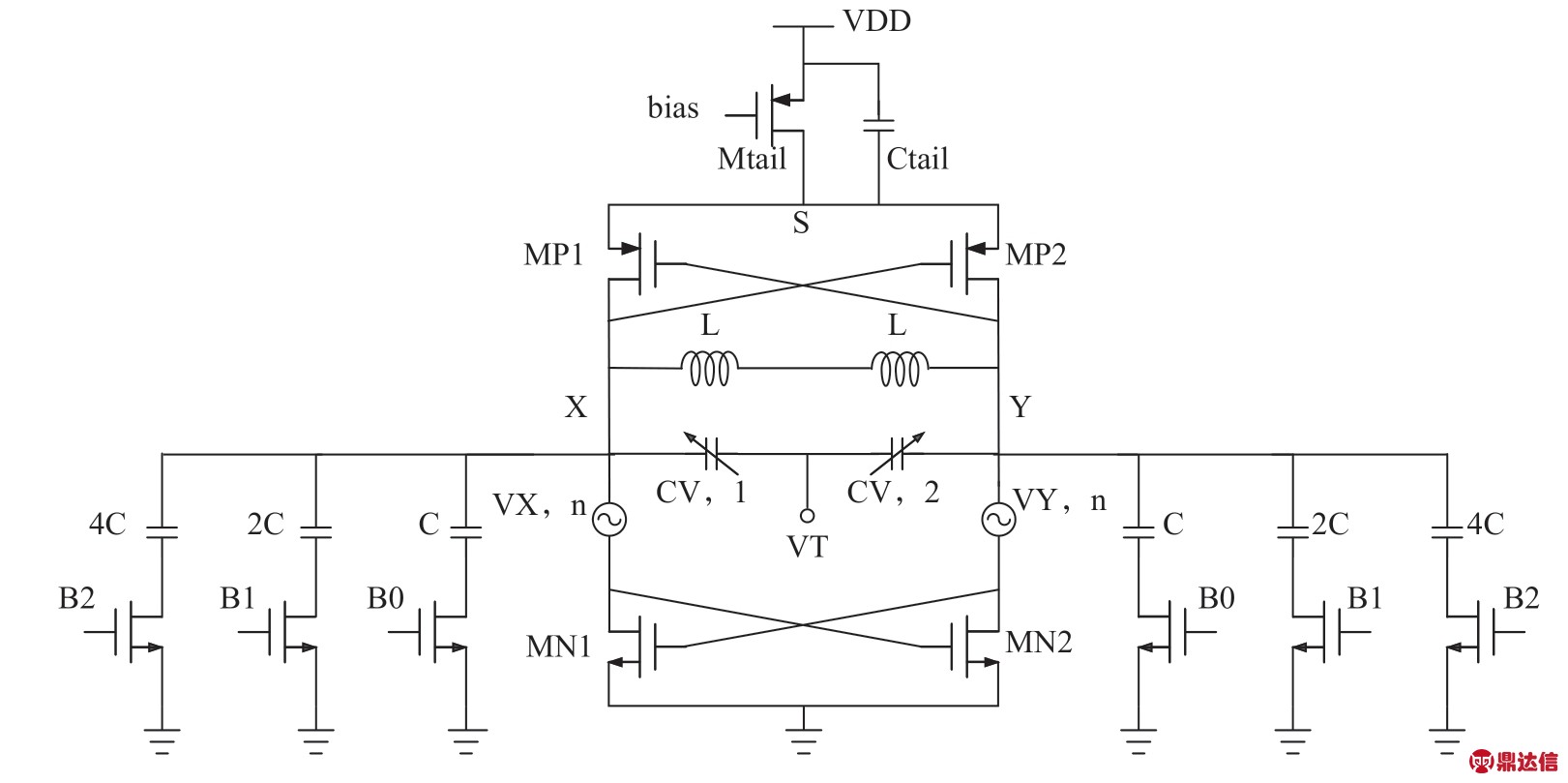

压控振荡器设计采用了LC 振荡电路,其相位噪声指标优势明显,同时PMOS 的噪声系数好,本结构只需使用1个差分电感用于等效图中2 个电感,版图面积小,VCO 的功耗仅9 mA。同时设置了多条选带,可以提高PLL 的锁定范围。最终设计的压控振荡器原理图如图5 所示。

图5 压控振荡器原理框图

7 环路设计

锁相环的开环传递函数G(s)为:

锁相环的环路传递函数H(s)为:

其中外围环路滤波器(二阶)的传递函数F(s)为:

其中,τ=RC,RC 分别为环路滤波器的阻值和容值。本芯片可以使用2 阶环路滤波器即可实现良好的相位噪声参数。通过装配测试,证明2 阶滤波器已经可以实现良好的系统指标。

8 E-FLASH 控制器

本芯片的控制部分全部通过E-FLASH 控制,E-FLASH的优势在于可重复烧写,掉电不会丢失数据,支持重复多次烧写。相比于熔丝结构,E-FLASH 可以大幅缩小芯片面积,可以一次性配置后提供给用户即可使用,用户也可以简单调试,效率可大幅提高。比熔丝结构有更大的灵活性,相比于SPI 和I2C 控制,工作量更小。

9 测试结果

芯片工艺的顶层选择制作了超厚金属以便提高模拟部分的性能,降低了互联线的方块阻值,可提高LC 振荡器中电感的Q 值,从而显著改善芯片的相位噪声指标。

其中为了确保射频部分的测试和仿真的一致性,对射频部分添加了阻挡层,此部分未填充金属密度,避免引入寄生的电容对VCO 的LC 振荡器频率产生影响。

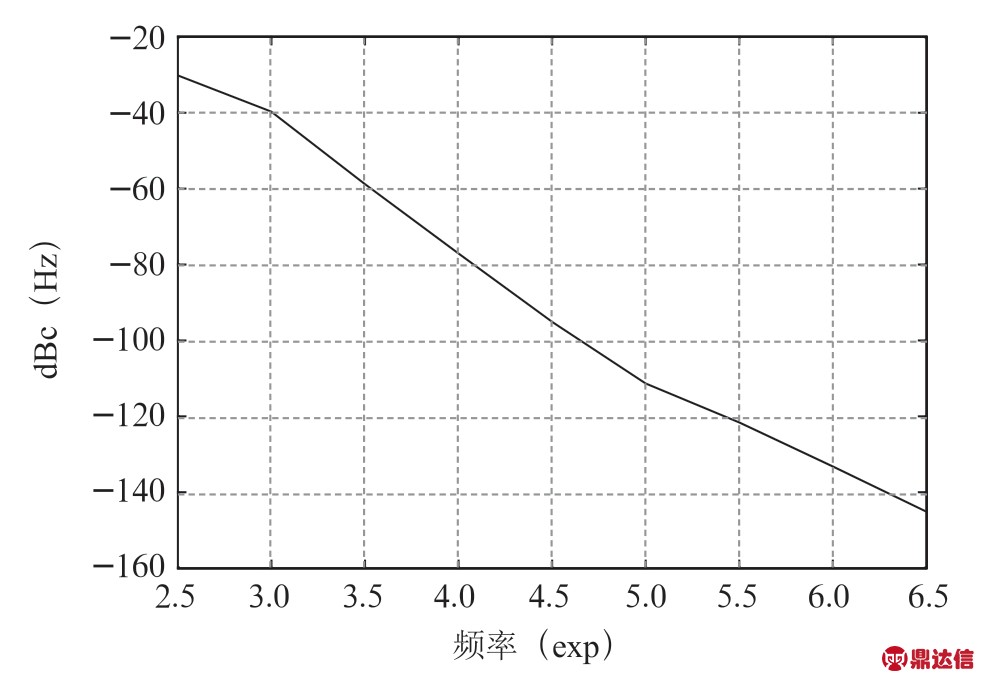

PLL 开环测试1.87 GHz 处测试相位噪声为-77.1 dBc/Hz@10 kHz,-111.4 dBc/Hz@100 kHz,-133.3 dBc/Hz@1 MHz。测试结果如图6 所示。

图6 锁相环相位噪声

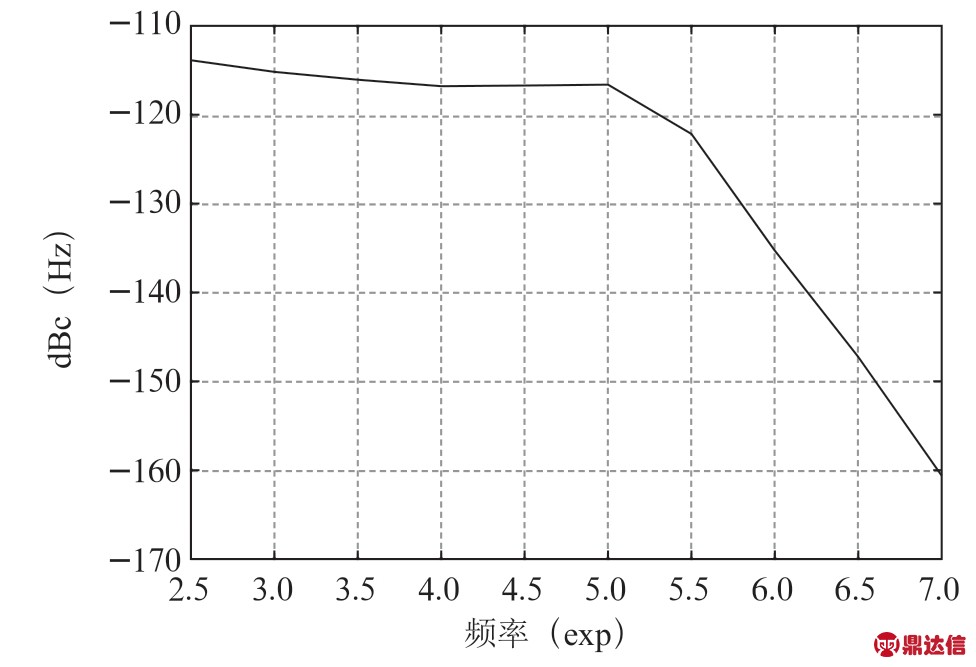

PLL 闭环测试1.8 GHz 处测试相位噪声为-116 dBc/Hz@10 kHz,-116 dBc/Hz@100 kHz,-135 dBc/Hz@1 MHz。测试结果如图7 所示。

图7 锁相环相位噪声

10 结 论

本文基于国内自主E-FLASH 工艺,设计了一款用于频率源的锁相环芯片,频率范围50 MHz ~2.6 GHz。测试显示,本芯片在-55 ℃~125 ℃下,3.0 V ~3.6 V 供电电压下均可长期可靠工作,相位噪声达到-116 dBc/Hz@10 KHz,135 dBc/Hz@1 MHz。可以用于基站设施、无线手持通信设备、时钟源、Wi-Fi 等领域。