基于TIA/EIA-899标准的TYPE-I型M-LVDS接收器设计

李智 1,2 , 陈迪平 1 , 赵建中 2 , 曹成成 1,2

| 【作者机构】 | 1 湖南大学物理与微电子科学学院; 2 中国科学院微电子研究所 |

| 【来 源】 | 《计算机工程与科学》 2015年第3期 P452-456页 |

| 【分 类 号】 | TN851 |

| 【分类导航】 | 工业技术->无线电电子学、电信技术->无线电设备、电信设备->接收设备、无线电收音机 |

| 【关 键 词】 | M-LVDS 高速接口 共模电压 迟滞 |

| 【基 金】 | 湖南省工业支撑项目(2013gk3019) |

| 【摘 要】 | 提出了一种基于TIA/EIA-899标准的TYPE-I型M-LVDS接收芯片的实现方案,设计了一种新颖的共模搬移电路在实现超越电源电压轨的共模输入范围的同时简化了后级电路设计,节约了面积和功耗,电路中预放大器将输入信号放大一定倍数,迟滞比较器为系统引入迟滞效果。芯片采用GSMC0.18μm 1P6M CMOS工艺流片验证。测试结果表明,该芯片共模输入范围为-1.4V~3.8V,信号传输速率大于250 Mbps,具有典型值为28mV的迟滞效果。 |

| 【全文获取】 |  pdf下载 pdf下载 |

基于TIA/EIA-899标准的TYPE-I型M-LVDS接收器设计*

摘 要:提出了一种基于TIA/EIA-899标准的TYPE-I型M-LVDS接收芯片的实现方案,设计了一种新颖的共模搬移电路在实现超越电源电压轨的共模输入范围的同时简化了后级电路设计,节约了面积和功耗,电路中预放大器将输入信号放大一定倍数,迟滞比较器为系统引入迟滞效果。芯片采用GSMC 0.18 μm 1P6M CMOS工艺流片验证。测试结果表明,该芯片共模输入范围为-1.4 V~3.8 V,信号传输速率大于250 Mbps,具有典型值为28 mV的迟滞效果。

关键词:M-LVDS;高速接口;共模电压;迟滞

1 引言

随着集成电路工艺尺寸的不断缩小,芯片内部工作频率越来越高,接口电路速度也随之提高,不断发展的高速微处理器、多媒体、光传输连接、智能路由以及网络传输对接口电路提出了更高要求[1],为了应对这一挑战,20世纪90年代,美国国家半导体公司提出了低电压差分信号LVDS(Low Voltage Differentical Signaling )技术,并成为行业标准,即TIA/EIA-644标准,具有高速、低功耗、低抖动、低串扰等优点,在高速数据传输领域得到了广泛应用。

为了实现芯片间及系统间的多点连接的信号传输,人们在LVDS接口的基础上发展了M-LVDS(Multipoint Low Voltage Differential Signaling)接口,并于2001年成为TIA/EIA-899国际标准。相比于LVDS,M-LVDS有更小的电磁干扰、更大的抗地电位漂移能力及噪声容限,特别适用于工业控制、电信基础设施和计算机的外围设备接口等场合[2]。

M-LVDS标准推出以来,国际上各大芯片厂商如德州仪器、国家半导体纷纷推出了相关商业芯片,最高传输速率可达250 Mbps,但国内并没有商业芯片面市,仅复旦大学做过相关研究。本文基于TIA/EIA-899标准设计了一款Type-I型[3]M-LVDS接收器,相比于普通的实现方案具有面积小、功耗低的优点。芯片采用GSMC 0.18 μm 1P6M CMOS工艺流片验证,各项测试结果均满足标准要求,最高信号传输速率大于250 Mbps,为相关设计提供了参考。

2 M-LVDS接收器拓扑结构

M-LVDS主要应用于工业控制、电信基础设施和计算机外围设备接口,这些场合电气环境复杂,噪声干扰大,传输线两端地电位漂移大,TIA/EIA-899标准针对地电位漂移要求接收器能实现-1.4 V~3.8 V的共模输入范围,LVDS标准针对差模噪声要求接收器应具有至少25 mV的迟滞效果[4]。为实现以上功能本文提出的M-LVDS接收器构架如图1所示。

Figure 1 M-LVDS receiver structure

图1 M-LVDS接收器结构

其中共模搬移电路将-1.4 V~3.8 V的共模输入信号搬移共模为1.2 V的位置,预放大器将输入差分信号放大一定倍数,最后由迟滞比较器为系统引入差分迟滞效果,同时完成差转单的功能。

3 M-LVDS接收器电路原理

3.1 共模搬移电路

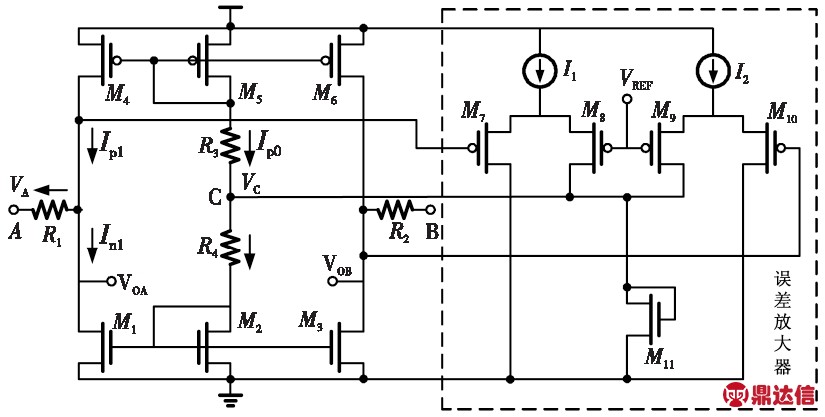

标准CMOS工艺,3.3 V电源电压下,放大器无法实现-1.4 V~3.8 V的共模输入,所以输入信号必须经过处理使其落在放大器的输入范围之内。为了满足共模输入范围的要求,参考文献[2]中利用电阻分压的原理设计了一个压缩网络,将输入信号压缩一定倍数使输出信号处于0 V~3 V之内。但是,在压缩过程中电路有用的差分信号也被压缩了,降低了接收器信噪比,同时下级电路仍需采用轨到轨输入放大器对信号进行放大,电路实现复杂。针对上述缺点,本文设计了一种共模搬移电路,如图2所示,该电路能将不同共模值的差分信号搬移到参考电平的位置,同时不改变差分信号幅值。电路由输入电阻R1及R2、电流调整电路、误差放大器构成。其中M7~M11与电流源I1、I2构成误差放大器,该部分电路将输出端VOA与VOB的共模值与1.2 V参考电压VREF进行比较并放大,调整C点电压,控制电流调整电路从输入电阻中抽取或者灌入一定电流形成压降,从而将不同共模的输入信号搬移到1.2 V。

Figure 2 Schematic of common-mode voltage shift circuit

图2 共模搬移电路原理图

对电路共模特性进行分析,以A输入端为例,当输入共模电压为1.2 V时,误差放大器的输入为0,输出为一静态电压,此时流过电阻R3、R4电流相等,由于M4、M5、M6以及M1、M2、M3尺寸相等,M1、M4电流相等,输入电阻R1无电流流过,VA=VOA=VREF。若电路由于某种原因导致共模变化,VOA势必发生变化。设误差放大器放大倍数为AV,那么放大器输出端产生的变化量为(VOA-VREF)×AV,这将导致R3、R4、M4、M1电流变化,最终影响流经R1的电流,从而改变输出端电压VOA,设电阻R3、R4上的电流变化为Ip0、In0,M4、M5漏电流变化为Ip1、In1,电阻R1上电流变化为I,由于M2、M5为二极管连接形式,可近似将M4、M5漏端电压看成不变,根据环路基尔霍夫电压定律或电流定律可列出如下方程:

VOA=VA+I×R1

(1)

I=Ip1-In1

(2)

Ip1=AV×(VOA-VREF)/R3

(3)

In1=-AV×(VOA-VREF)/R4

(4)

联立上述方程可得出:

(5)

其中VA-VOA有最大值,合理设置误差放大器放大倍数AV以及R1、R3、R4的值可使VOA-VREF≈0,即电路在任何共模输入的情况下,共模输出始终与参考电压一致。

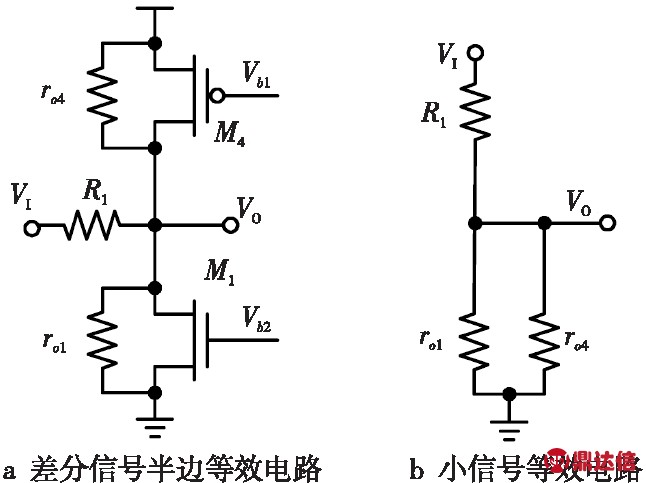

对于输入差分信号,电路半边等效电路及小信号等效电路如图3所示,由基尔霍夫电压定律或电流定律可以得出输入与输出关系为:

(6)

其中ro1、 ro4为晶体管M1、M4的沟道电阻。由于ro1、 ro4阻值远远大于输入电阻R1、R2的阻值,上式化简后可得出对于差分信号VO可与VI近似相等,因此电路在完成输入共模搬移的同时,不会对输入差分信号产生影响。

Figure 3 Differential small signal equivalent circuit

图3 差模小信号等效电路

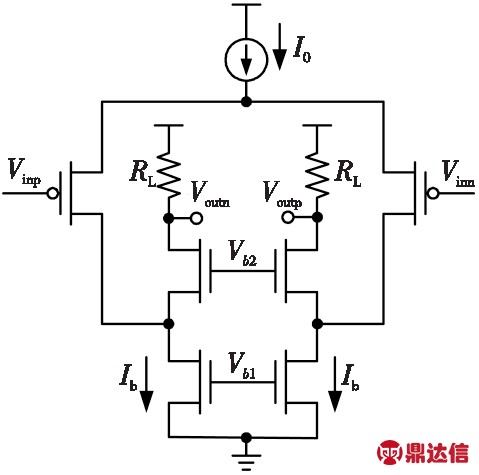

3.2 预放大器

预放大器在接收器中处于承上启下的位置,主要功能是将共模搬移电路输出信号放大一定倍数,以提高后级迟滞比较器分辨能力、降低失调,同时将迟滞比较器翻转时产生的回扫噪声与输入低压差分信号隔离[5]。

Figure 4 Schematic of pre-amplifier

图4 预放大器电路原理图

电路如图4所示,由PMOS构成输入对,负载采用Cascode结构以获得尽可能大的信号带宽[6]。因TIA/EIA-644标准要求接收器应具有至少25 mV的迟滞效果,本设计中迟滞比较器迟滞电压为300 mV,可知预放大器放大倍数AV约为12,AV由式(7)决定,合理选择RL大小可实现所需的放大倍数。

AV=-gm×RL

(7)

电路输出共模电压由式(8)确定,在RL、VDD、I0确定的情况下,调整Ib大小可满足迟滞比较器的共模输入范围要求。

(8)

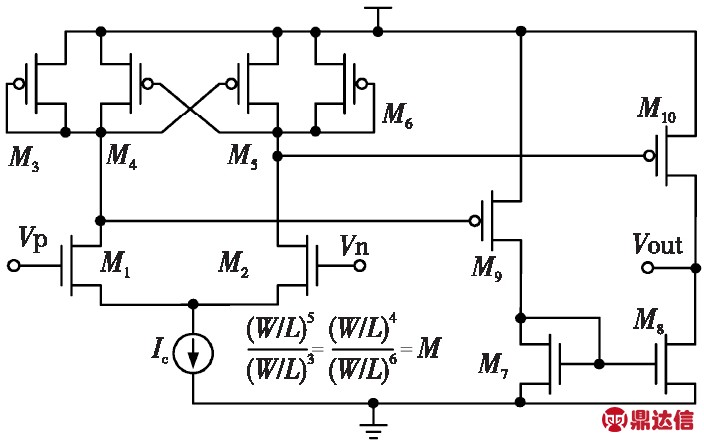

3.3 迟滞比较器

M-LVDS主要应用于噪声环境,因电路使用差分线传输信号,共模噪声能有效地抑制,但差模噪声却无法避免,接收器阈值附近的噪声将直接导致错误的输出信号。为了避免这一现象,本文利用内部正反馈原理设计了一迟滞比较器,为系统引入迟滞效果的同时完成差转单功能,如图5所示。图5中,电路中有两条反馈通路,第一条为M1、M2共源节点的串联电流反馈,表现为负反馈,第二条为M6、M7漏端源端的并联电压反馈,表现为正反馈,当电流镜比例M大于1时电路总体表现为正反馈并出现迟滞效果。迟滞电压表达式由式(9)给出:

(9)

其中β=uncox(W/L)1/2。

为了使电路获得尽可能快的速度,电路采用NMOS管作为输入管,M3、M4、M5、M6、M9、M10设计成较小尺寸以减少寄生电容。电路中M7~M9将迟滞比较器输出的差分电压信号单端化,使迟滞曲线更加陡直。此电路具有全摆幅输出能力,可直接驱动数字逻辑电路[7]。

Figure 5 Schematic of hysteresis comparator

图5 迟滞比较器原理图

4 仿真与测试结果

本文设计的M-LVDS接收器采用GSMC 0.18 μm 1P6M标准CMOS工艺流片验证。由于共模搬移网络有固定的输出共模,仅需要采用单一的P输入预放大器就能对信号进行放大,无需设计轨到轨输入的放大器及相应的偏置电路,如图6所示,接收器电路面积仅为400×250 μm2,芯片整体面积为1.2×1.2 μm2。

Figure 6 Layout of M-LVDS receiver

图6 M-LVDS接收器版图

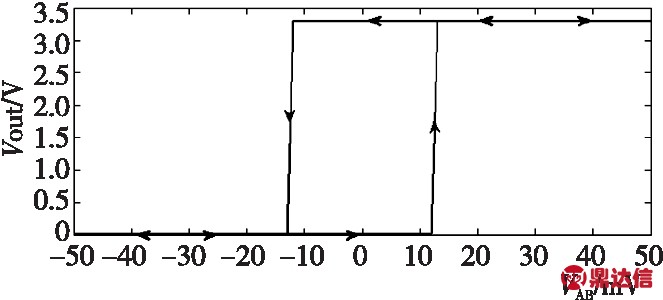

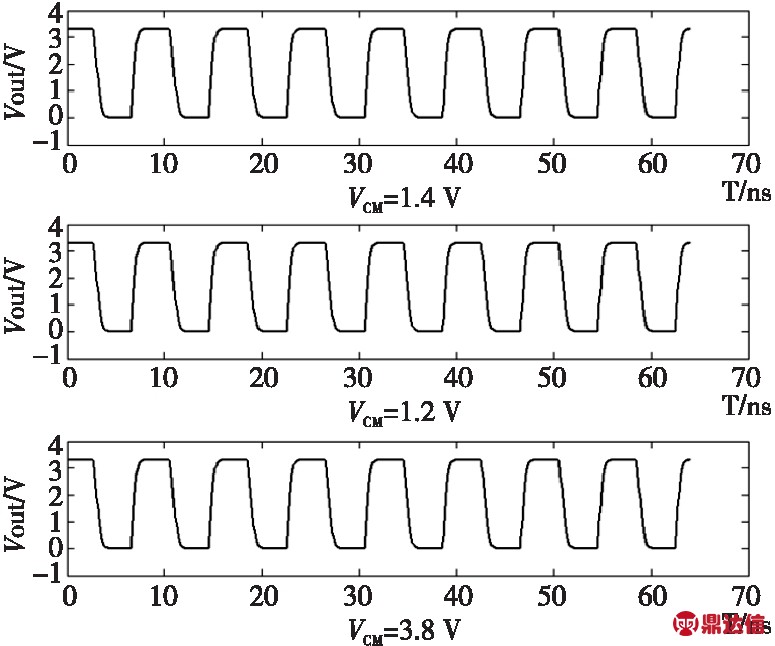

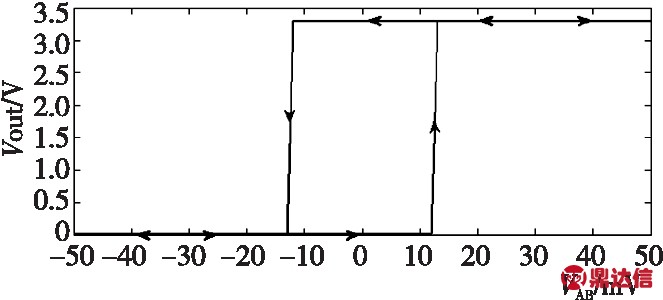

在Hspice环境下对提取寄生参数后的电路进行仿真,图7显示了接收器输入端分别接共模电压为-1.4 V、1.2 V、3.8 V,频率为125 MHz、差分幅值为200 mV的方波输入时输出端的波形。结果表明,使用了共模搬移电路的接收器能实现超越电源轨的共模输入范围,满足TIA/EIA-899标准对芯片容许地电位漂移的要求。图8为芯片迟滞效果的后仿真结果,系统正翻转电压值为12.5 mV,负翻转电压值为-12.5 mV,总迟滞电压为25 mV,芯片实际测试迟滞电压典型值为28 mV,与后仿真结果偏差较小。

Figure 7 Output waveform of different common-mode inputs

图7 不同共模输入信号下接收器输出波形

Figure 8 Hysteresis curve of receiver

图8 接收器迟滞曲线

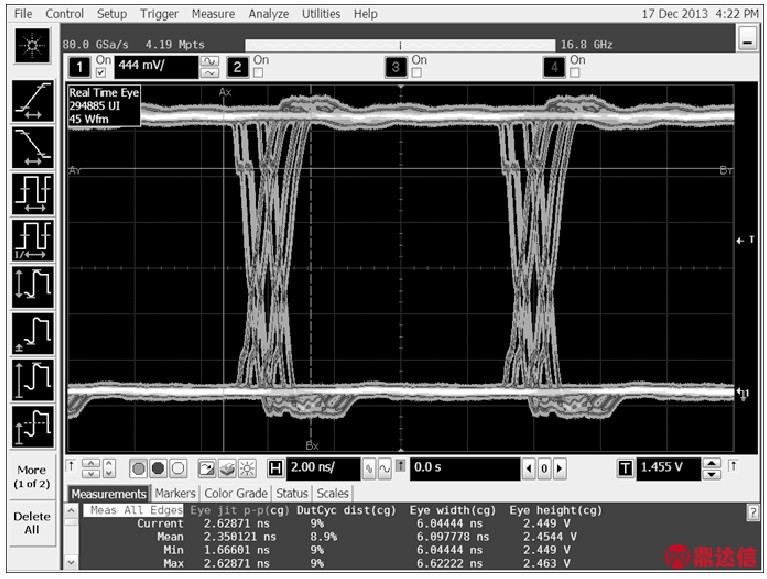

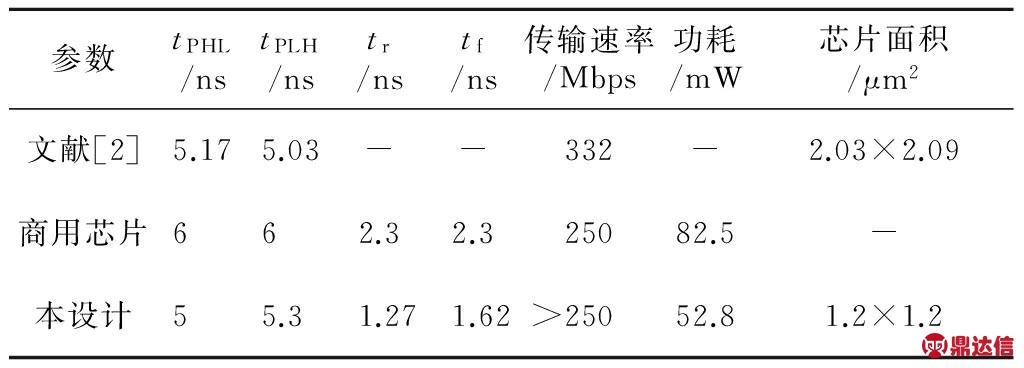

图9为250 Mbps 215-1 PRBS输入时输出端信号眼图,测得眼高为2.45 V,眼宽为6.1 ns、峰峰值抖动为2.3 ns。表1将本设计与参考文献[2]以及德州仪器推出的一款型号为SN65MLVD2的商用芯片关键参数进行比较,其中tr、tf分别为输出波形上升时间和下降时间,tPHL、tPLH分别为上升沿传播延时和下降沿传播延时。可以看出本文提出的接收器芯片交流参数均达到或超过了另外两款接收器,同时在面积与功耗方面具有一定优势。

Figure 9 Eye-pattern of receiver at the signaling rate of 250 Mbps

图9 250 Mbps信号传输速率下输出端眼图

Table 1 Parameters comparison

表1 接收器参数比较

5 结束语

本文设计了一款TYPE-I型M-LVDS接收器,提出了一种新型的共模搬移电路,能将不同共模值的差分信号搬移到固定共模电压的位置,简化了后级电路,节约了面积与功耗。由折叠式共源共栅放大器将输入信号放大固定倍数,并设计迟滞比较器为芯片引入迟滞效果。测试结果显示,该接收器具有-1.4 V~3.8 V的共模输入范围,信号传输速率大于250 Mbps,常温、3.3 V电源电压下迟滞电压为28 mV,各项指标均满足标准要求,适用于高速接口相关的应用。