摘 要:结构和工艺设计优化已经成为封装必不可少的步骤。随着探测器封装尺寸越来越小以及可靠性要求的不断提高,气密性封装结构向表面贴装、超薄型、芯片与封装体面积比更高的方向转变,封装结构和封装工艺的设计成为可靠性、成品率和成本的关键。骑跨式贴片半导体辐射探测器陶瓷封装中,存在芯片粘接衬底、密封环、引脚与HTCC陶瓷件钎焊处有Ag72Cu28焊料堆积、爬行的现象,以及芯片的Au80Sn20焊接层存在空洞大而又无法通过X射线照相或芯片粘接的超声检测来筛选剔除不合格的问题,分析原因并通过优化封装结构、改进封装工艺等解决封装的质量和可靠性。实际生产结果表明,结构优化、工艺改进有效地简化了外壳结构,减少了制造工序步骤,并提高了芯片烧结质量和成品率,降低了封装成本。

关键词:一体化引线;合金烧结;封装结构;封装工艺

1 探测器封装概述

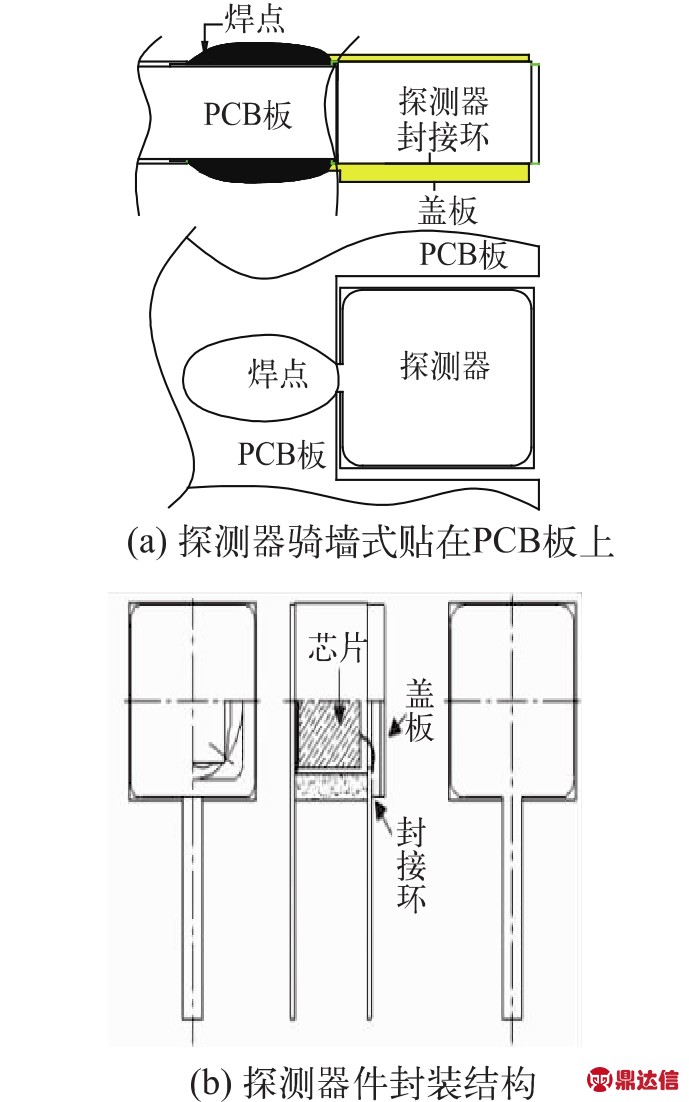

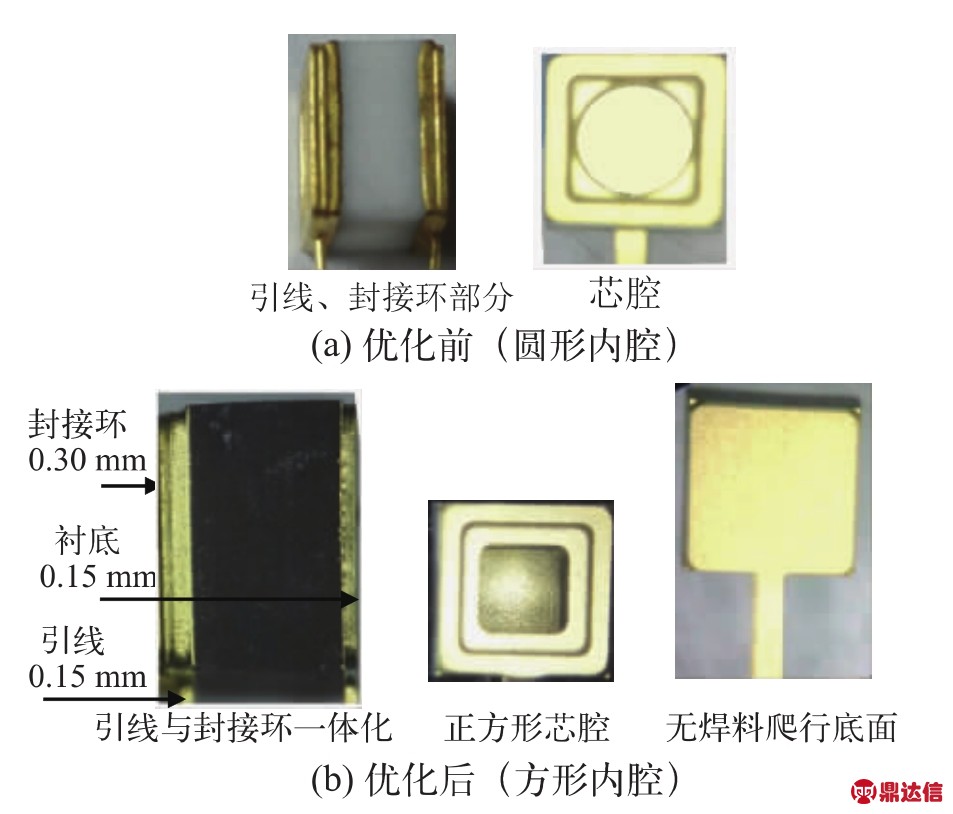

半导体辐射探测器为了提高可靠性,通常采用气密性陶瓷封装,在CDFN/CQFN、CLCC、CSOP等表面贴装中[1],要适应2 mm甚至更高厚度的探测器单元的封装需要增加外壳腔体高度,信号引出端通过金属化通孔或表面金属化布线均会增加外壳壁厚而使封装体尺寸增大,为此需采用与PCB板相同厚度的骑墙式陶瓷封装结构,参见图1(a)。外壳陶瓷件采用抗弯强度400 MPa以上的氧化铝HTCC工艺制备,芯腔衬底采用4J42或4J29金属板并与引脚整体加工成型,引线键合台阶与引脚亦采用4J42或4J29金属板整体加工成型,封接环冲制或刻蚀[2],金属件与陶瓷件通过Ag72Cu28钎焊在一起,然后电镀Ni-Au[1],盖板亦电镀Ni-Au或者化镀Ni-P。采用Au80Sn20共晶合金焊料将背面金属化的芯片烧结于芯腔衬底上,其是采用SnPb、InAg和BiSn等锡焊强度的2倍[3],然后依次进行铝丝或金丝的键合、平行缝焊封帽等,参见图1(b)。

图1 平行缝焊直插HTCC封装结构图

2 探测器封装可靠性分析

2.1 探测器封装可靠性

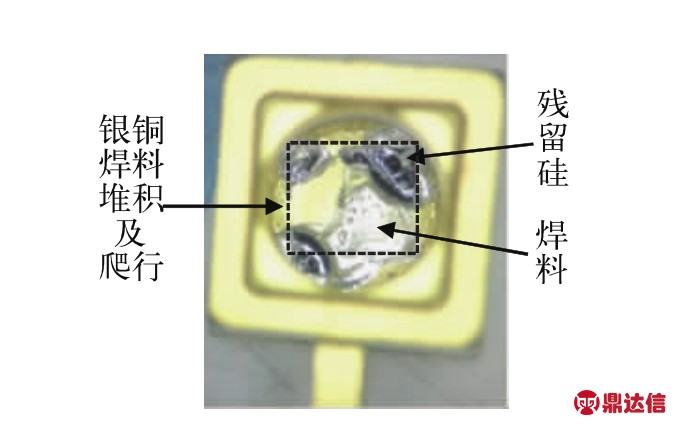

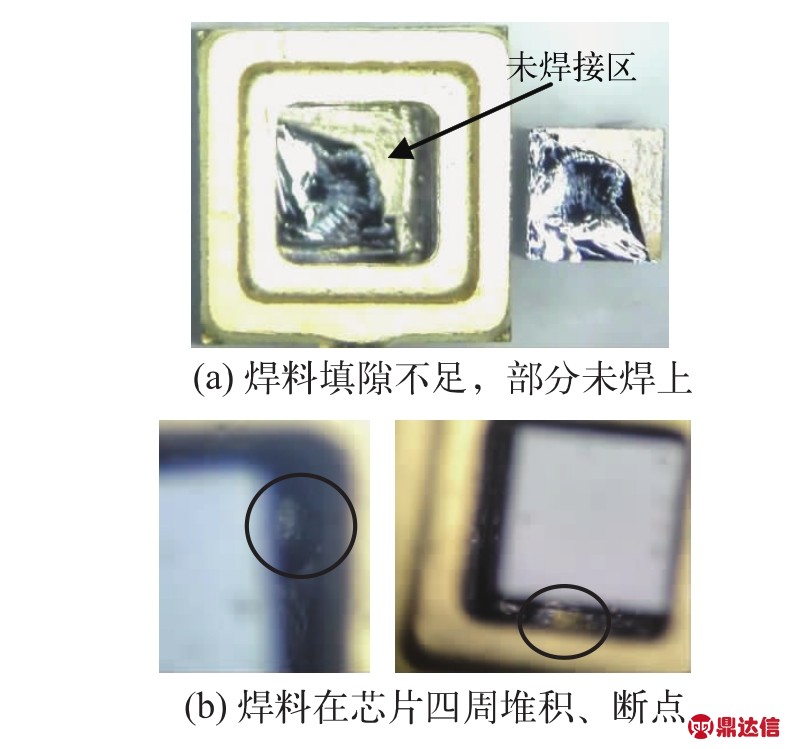

对封装探测器进行非破坏性键合拉力(抽样)、-55~125℃温度循环、20000 g恒定加速度、粒子碰撞噪声检测(PIND)、密封等筛选和考核,发现主要存在芯片偶发性脱落,未发现其他封装问题。对失效样品开帽后发现芯片与衬底烧结有效接合面小,结合面主要集中在芯片4个顶角位置,参见图2和图3。进一步分析发现,Ag72Cu28焊料钎焊时,焊料沿衬底爬行,并在钎焊缝四周形成略比中间芯腔高的堆积,当50μm厚的Au80Sn20焊料不足以填充芯片下的缝隙时,则会出现图2和图3中局部焊接上或焊料填充不足的问题。

采用X射线仪对封装器件进行无损检查,发现芯腔四周边缘有明显的Ag72Cu28堆积、Au80Sn20堆积以及芯片下的空洞,表明外壳衬底的不平坦是造成可靠性的主要问题,参见图3。

图2 机械试验后出现脱落典型图

图3 封装探测器件X射线照片

2.2 探测器外壳和封装工艺

对探测器用陶瓷外壳外观进行分析,除了图2中出现的芯腔内四周有Ag72Cu28焊料堆积外,还发现衬底外侧及底部四周也存在一定比例的焊料爬行,参见图4。对芯腔表面进行检查也发现银铜爬行到的区域,若存在微沟(参见图5)则会出现图3左边探测器的焊接层空洞。这些缺陷均可导致Au80Sn20焊料片在氮气中烧结芯片遇到温升不均匀、Au80Sn20焊料填隙能力减弱而容易堆积的问题,图3中就可明显看到Au80Sn20焊料堆积的现象。

图4 银铜焊料在底面上的爬行

图5 芯腔衬底表面状态

3 封装结构和工艺优化

封装问题主要是芯片烧接以及封装生产效率,以及芯片烧结缺陷封装的检验筛选,从封装结构优化和封装工艺优化2个方面来解决。

3.1 封装结构优化

在不改变封装尺寸的情况下,基于芯腔内的Ag72Cu28焊料堆积主要在四周和芯片为方形,将内腔结构改为正方形,这样芯片的4个顶角离外壳侧壁的距离就会增大,四周堆积的银铜焊料离芯片的距离增加,芯片与外壳侧壁距离也由不均等变为均等,有利于Au80Sn20焊料烧结时均匀分散。同时银铜焊料片由80 μm降到60 μm,金属零件均采用刻蚀以保证圆边吸收银铜焊料,这样可以减少银铜焊料的堆积和爬行;0.15 mm封接环、0.15 mm引线键合台阶与引脚改用0.30 mm材料一次性做台阶刻蚀[2],去掉0.15 mm封接环与0.15 mm引线键合台阶(含引脚)之间的银铜钎焊,从设计上消除银铜钎焊流淌造成引线键合区不平坦对键合成品率和可靠性的影响。引脚、键合台阶与焊框一体化刻蚀、腔体改为方形后的外壳照片见图 6(b)。

图6 封装结构优化

3.2 封装工艺优化

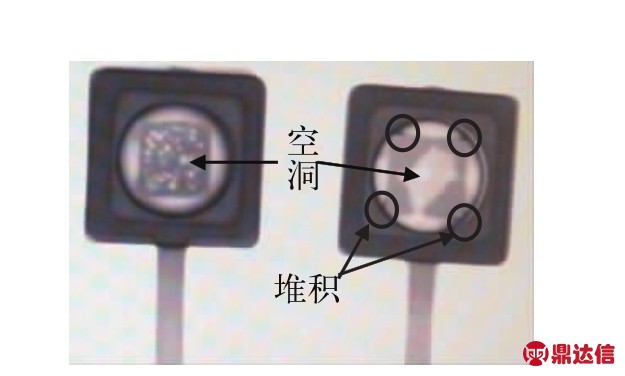

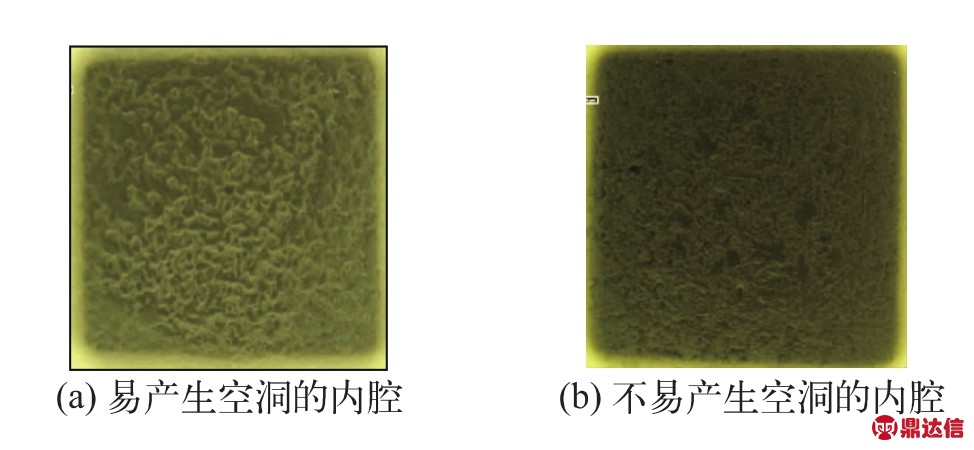

芯片焊料烧结有Au80Sn20真空烧结工艺、保护气氛静压烧结工艺以及金-硅共晶摩擦焊工艺[4],在这些工艺中保护气氛静压烧结工艺是相对简单且可批量生产的,但存在烧结缺陷较多的问题。这些缺陷与焊料片尺寸(尤其厚度)、杂质(尤其表面氧化、污染),芯腔焊接面平整度、可焊性(尤其镀金层厚度),烧结气氛(尤其氧和水汽含量)等相关。结构改进后的保护气氛静压Au80Sn20焊料烧结芯片工艺中主要缺陷有:(1)因芯腔存在微细颗粒导致焊接缝隙大而使焊料熔融填隙不足,芯片焊接层有空洞,参见图 7(a);(2)少部分器件存在Au80Sn20焊料在芯片四周堆积或者形成断点,参见图 7(b)。

图7 Au80Sn20烧结芯片的典型缺陷

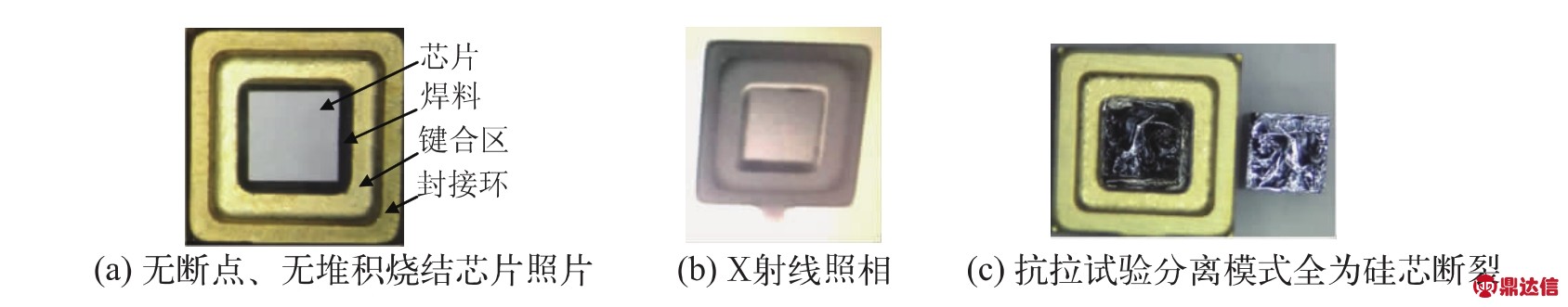

针对采用Au80Sn20焊料保护气氛静压烧结工艺存在的缺陷,包括Au80Sn20焊料在芯腔内均匀铺开但与芯片偶尔有孔洞而X射线又不能筛选掉的问题,首先将焊料片厚度由50 μm增加到100 μm,即使芯腔衬底平坦度差也可以保证芯片与衬底之间有足够的焊料填充;对于Au80Sn20焊料片等因贮存等可能存在的表层氧化问题[5],采用《电子工业生产技术手册(半导体与集成电路卷):硅器件与集成电路》第14.3.2节中的清洗工艺,对Au80Sn20焊料片进行清洗处理;陶瓷外壳则在组装前进行微波等离子清洗[6],或200℃、2 h还原性气氛下的高温清洁处理;带真空烘箱的充氮手套箱中装架或净化工作台装架后进行除气充氮处理;烧结气氛由N2保护气体(O2含量小于50×10-6(V/V))改为还原性95%N2-5%H2中烧结;将烧结模具(带加热)改用吸热量小、可重复使用的耐350℃高温不锈钢弹簧夹具替代,烧结设备由充氮烘箱改为N2-H2还原气氛链式炉并增加水冷控温装置,以保证连续批量生产的稳定性。工艺优化后,芯片四周的焊料连续且无焊料断点、无焊料堆积,参见图8(a),芯片烧结层中的空洞率低于2%,X射线照相也未发现芯片焊接层有可见的空洞,参见图8(b),抗拉试验后的分离模式均为芯腔衬底上100%残留硅,分离发生在硅芯片中间,参见图8(c),工艺优化达到了“零缺陷”工艺技术要求。

图8 优化烧结工艺后的外观、X射线检查

4 批量生产结果

结构和工艺优化后,HTCC外壳钎焊由两次钎焊变为一次钎焊,银铜焊料爬行得到解决,芯片烧结外观和焊接层空洞率大幅度降低,经过90000只生产,芯片烧结成品率在99%以上(破坏性检测不计算在内),封装总成品率提升到98%以上(破坏性检测不计算在内),较改进前提升30%以上。器件在筛选、鉴定中未出现封装成品率波动或批次问题,表明封装结构、工艺可靠性设计已达到最优化。

5 结论

气密性探测器封装结构和工艺优化结果表明,结构优化有效地简化了外壳结构,并减少制造工序步骤,降低外壳成本;Au80Sn20合金烧结芯片工艺改进消除了焊料堆积、断点以及芯片与衬底之间焊料缺失、空洞等工艺缺陷,提高了芯片烧结成品率和焊接质量与可靠性。这些结构改进、工艺优化也适用于同类型封装产品的封装设计与封装工艺优化中。